文‧Shivansh Chaudhary/Lennart Berlin

目前的雷达系统往往需经过进阶测试与验证,才能确保该系统可在复杂且混乱的通讯环境下正常运作,同时确定该系统完全符合效能规格,并可进一步充分发挥其效能特性。工程师在针对雷达系统设定自动化测试时,评估系统中最重要的仪器为RF/微波讯号产生器与频谱分析器。讯号产生器可做为测试讯号源,用以精确模拟作业环境,而基本函式产生器则可驱动讯号产生器的脉冲和AM与FM电路。接收器中天线所接收的微弱讯号,透过具备高动态范围与低相位杂讯的频谱分析器,便可侦测与放大。

雷达系统考验接收器杂讯水准

近期雷达技术越来越先进,例如主动电子扫描阵列雷达(Active Electronically Scanned Array, AESA)与多功能系统等皆有进展,因此雷达测试需求也变得越来越具挑战性。本文将说明这些挑战,并介绍目前可执行新一代雷达测试自动化测试设备(Automated Test Equipment, ATE)系统的测试需求。

目前的雷达系统必需能在复杂无比的讯号环境下达成目标,因此必须使用失真度比以往更低的接收器。为满足最严格的接收器规格,测试需要一个可以产生低相位杂讯的讯号,且需具备优异的杂波与谐波效能。由于直接将数位域转换为微波频率有其难度,而反之亦然,因此有项常见的做法便是使用两个以上的局部震荡器(Local Oscillator, LO)来执行多阶段转换。使用多个L时,每一个LO皆必需尽快且紧密地同步化,并彼此锁定相位。如果能在所需的频率上越快执行相位锁定与同步化,整体的测试与量测时间便会越快。同步化在AESA雷达中是特别重要的考量,由于一个AESA雷达中就具有几千个与天线相连的接收器,因此每个接收器都必需经过同步化。

如上所述,测试雷达接收器可藉由多种测试讯号的讯号产生器,涵盖范围从脉波CW至利用频率调变与扫频产生的唧声。一般而言,雷达使用脉波RF/微波讯号来执行测试,而脉波的特性将深深影响系统效能与功能。举例来说,脉波功率会决定目标的范围,而脉宽则会定义目标的空间解析度。在雷达测试与检验中,讯号产生器可做为替换LO的来源,因其低相位杂讯与高频谱精纯度能提供量测接收器更高的动态范围与灵敏度。

有了AESA多功能雷达系统,雷达效能、稳定性与扫描速度得以大幅提升。常见的AESA架构包含数千个传输/接收(T/R)模组,每个模组皆搭载天线。每个T/R模组均需具备精确的相位,并使振幅相符,而这些要求是雷达测试与验证的重大挑战,因此使得设计更加复杂。

Giraffe 4A AESA雷达具备多功能运作弹性

AESA雷达在过去30年间不断演进,不管在讯号处理或RF/微波的技术,都持续推陈出新,例如氮化镓功率放大器、单晶微波积体电路(Monolithic Microwave Integrated Circuit, MMIC)与毫米波积体电路,皆是为了降低T/R模组成本。不同于传统的机械控制阵列(Mechanically Steered Array, MSA)或被动式电子控制阵列(Passive Electronically Steered Array, PESA)雷达,AESA雷达提供传输/接收模组增益与相位的数位和独立控制功能。此特性在雷达的波束赋形与波束控制的灵敏度上带来极大的优势。AESA雷达与传统雷达相比稳定得多,主要是因为上千个独立的T/R模组取代了单一通道,让雷达得以不在停用整个系统的情况下,还能承受些许故障。

AESA的模组化方法可顺畅地以更高阶的元件取代T/R模组,使效能大幅提升。AESA多功能雷达的其中一个例子,就是Saab推出的Giraffe 4A雷达(Giraffe 4A Radar)(图1)。Giraffe 4A是一款具备多功能运作弹性的软体定义雷达,可让操作人员视情况灵活修改讯号处理任务与波形,并在不同运作模式间切换。Giraffe 4A是绝佳的解决方案,证实在因应雷达测试的挑战时,确实需要模组化雷达的ATE系统。Giraffe 4A雷达分别由3个功能性元件组成:激发器、接收器与天线。测试的主要需求与元件的特性描述如下:

图1 Giraffe 4A AESA雷达

激发器

激发器的主要功能是针对接收器产生内部LO,并对传输器产生载波讯号。其所产生的讯号必需稳定,具备低相位杂讯与低混附内容,且能够快速切换频率,因为低混附内容与谐波才能传输排除杂讯的讯号。当清晰的LO讯号穿透接收器,接收器便能在混杂的环境下轻松侦测该讯号。

接收器

接收器的功能为粹取来自天线的微弱反射讯号,在不增添杂讯与失真的情况下将之放大,并传送至处理器执行脉波解压缩/讯号处理。

接收器必需具备低杂讯系数与干扰讯号的高电阻。接收器杂讯(更精确的说法是「灵敏度」)会限制雷达的涵盖范围,而低相位杂讯在侦测与追踪目标的细微改变上扮演着重要的角色。接收器同时必需具备高动态范围,以预防杂讯讯号使系统达到饱和状态。

天线

天线接收来自电磁场(Electromagnetic, EM)的能量,并传导激发器产生的电磁波。AESA的天线包含传导元件与天线结构,T/R模组与相关控制电路、RF波束形成器、DC电源分配与波束控制的控制器。天线必需搭载精确的主瓣(位在最大量辐射方向的区域)与低旁瓣,以大幅降低来自他处的辐射,并针对波束赋形减少主瓣快速转向。

模组化雷达ATE系统

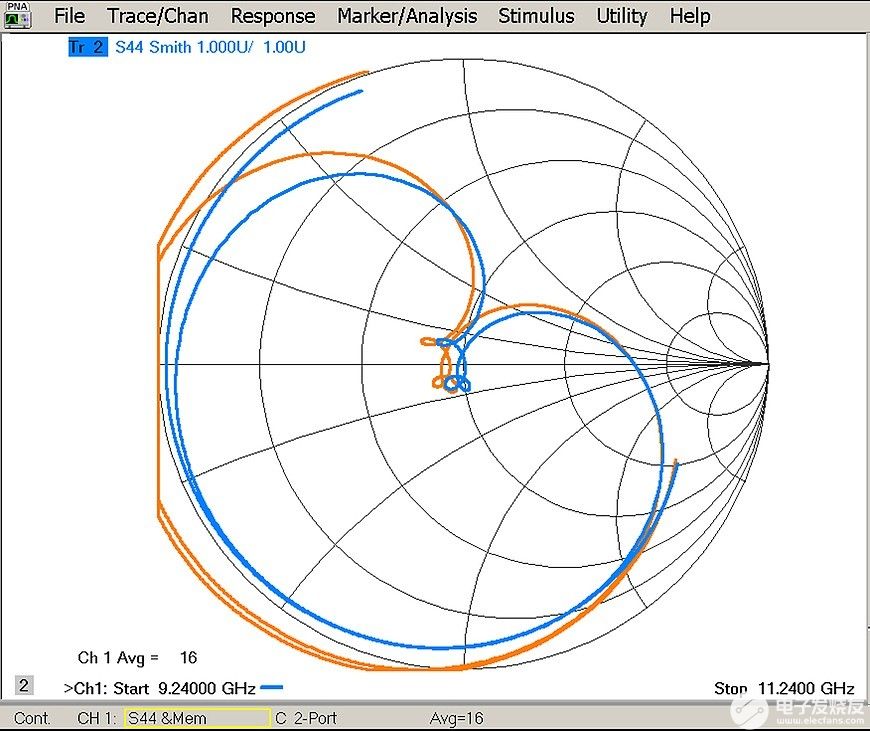

为了测试并进行Giraffe 4A雷达子模组的特性描述,Saab的工程师决定选用NI PXIe-5668多阶段超外差26.5GHz向量讯号分析器(Vector Signal Analyzer, VSA)。

NI的VSA除了具备低混附与谐波内容之外,还可以在765MHz瞬间频宽中提供所需的动态范围与合理的扫描时间。PXIe-5668R的模组化机型非常符合Saab的雷达测试台的标准。为了突破成本与体积的限制,Saab的测试工程师使用NI PXIe的模组化仪器,设计一款内部相位杂讯量测系统。该相位杂讯量测作业将撷取到的讯号分成双通道,使用LO讯号将其降转为基频类比波形,并把该类比波形传送至示波器执行交叉相关的作业。本系统同时也使用其他PXIe仪器,例如数位I/O、用于控制降转换器的驱动程式和切换模组、乘法器、分压器与切换电路。整个相位杂讯量测系统则是透过LabVIEW控制。测试工程师针对天线测试的部分架设室内测试范围并利用NI PXIe架构的模拟战场情境模拟器,并透过LabVIEW架构的应用搭载远端存取(图2)。

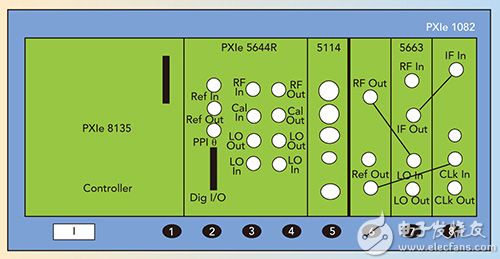

图2 此战场模拟器使用NI PXIe-5663 VSA执行RF量测,其中的PXIe-5114为示波器,而PXIe-5664R向量讯号收发器运用使用者可设定的内建FPGA,来执行即时情境模拟。

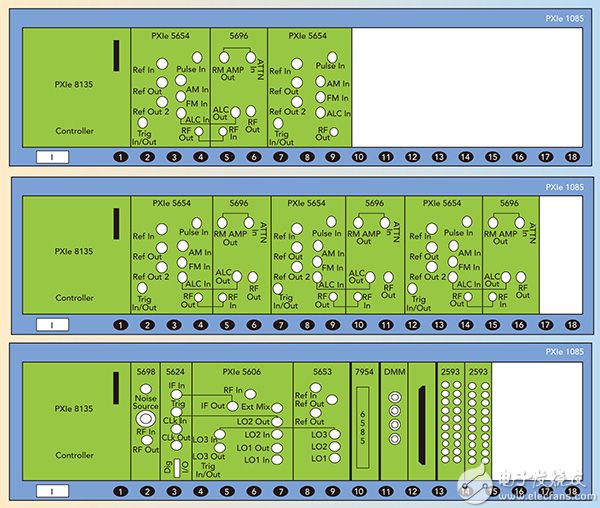

透过LabVIEW,测试设定的模组化特性让许多仪器能够整合成先进的雷达ATE系统。本系统包含3个PXIe机箱(图3)、5个PXIe-5654 RF讯号产生器、4个PXIe-5696振幅扩充模组、前端装载低杂讯微波的PXIe-5668R VSA。该系统同时也包含搭载低电压差动讯号传输(Low Voltage Differential Signaling, LVDS)的NI FPGA机板,主要做为传送与接收指令至受测单位(Units Under Test, UUT)的控制器。系统还包括了NI继电器驱动模组,可控制ATE设备内切换器,微波PXI切换模组可在ATE内连接讯号,NI PXI多功能数位电表(Digital Multimeter, DMM)与PXI多工器模组,可用来连接低频率的讯号。除了3个PXI的机箱之外,此ATE系统具有2组19吋机架可用来置放电脑、电源分配电路、电源供应器与Virginia Panel Corporation, VPC)的介面,并提供空间能视UUT需求额外增设更多仪器讯号路径。

图3 Giraffe 4A雷达的3个PXIe机箱设定

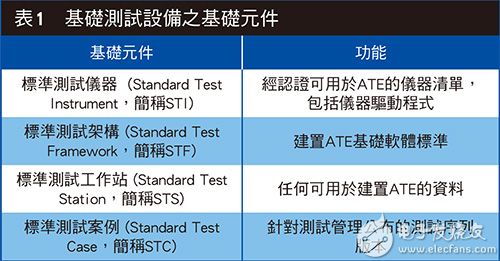

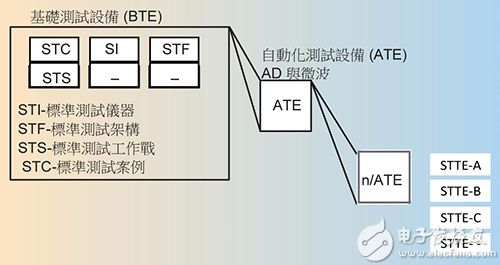

图4为ATE基础测试设备(Base Test Equipment, BTE)常见的基础元件,其功能列于表1。VPC介面为测试仪器与UUT间的大量互连系统,让使用者能连接不同设备,例如根据客户规格设计与打造的特别类型测试设备(Special Type Test Equipment, STTE)(图5)。

图4 BTE基础元件提供UUT测试所需的资源

图5 用以选择BTE资源的VPC介面

平台化雷达ATE带来成本/时间优势

如同Giraffe 4A ASEA雷达的范例所示,打造模组化雷达ATE系统需先符合几项UUT的关键需求。而建置PXI架构的模组化ATE系统带来雷达测试传统方法所缺乏的优势,包括成本、时间与标准化作业。

随着目前雷达的测试挑战持续演变、需求不断成长,BTE函式库也逐渐扩充、支援ATE经检验的驱动程式与仪器记录功能。由于系统不停更新汰换,或无法满足新的测试需求,传统ATE系统往往伴随高额的工具替换成本。

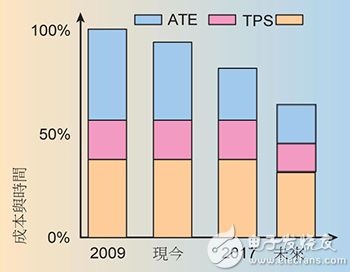

不过,PXI的开放架构却可以确保资源有效利用,并以最适切的方式再利用产品与工程设计。图6可见,为因应全新雷达测试需求,工程成本与时间皆有所下降。当产品越来越复杂,开发与测试的成本便会随之升高。不过,下跌的平均售价也使得测试成本也必需随之降低。因此,要让此系统能持续获利,测试的成本降低的速度便需等于或高于生产价位降低的速度。Saab采用PXIe平台架构,成功降低测试成本,且提升效能、扩充能力与测试速度,从而缩小体积并减少功率损耗。

图6 测试全新雷达系统所减少的ATE成本与时间

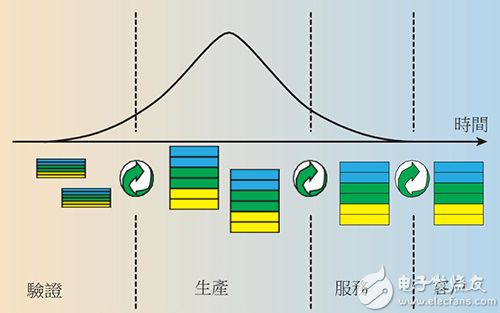

运用平台架构的方式以标准化雷达ATE系统,能带来可互换性。每当一项新的技术推出,它便会升级较旧版的系统,使旧款产品的使用频率降低,或者将之淘汰。PXI平台架构雷达ATE备有能与其他系统互通的元件,只需透过常见的程式设计与作业环境(如LabVIEW),便可彼此结合使用。随着时间过去,应用、操作与维护这些系统的使用者不需透过专门训练也能使用该系统,进而省下成本。图7说明测试策略与产品生命周期间的关系。图中「产品」的曲线显示在生产期间会通过测试的产品数量,「测试系统」则代表ATE的总数。此图显示,每新增一个额外的ATE设备,生产线的生产力便可提升超过双倍。透过PXIe平台架构的方式来标准化ATE,便能设立一套长效的测试策略,其与产品寿命周期呈正相关。

图7 测试策略与产品寿命之间的关系

在建置雷达测试系统时,雷达设计师与测试工程师必需谨慎评估测试仪器的规格,进而判断如何提高投资收益。随着近年来多功能雷达(如AESA)越来越先进,测试系统也变得更加复杂与昂贵,促使人们开发一套先进的模组化雷达测试系统,以便能在应测试挑战的情况下仍可降低测试成本。Saab藉由NI PXI平台架构方法来标准化雷达ATE架构,因此能大幅减少所需的工程资源、成本与时间,而这些都是因应进阶AESA雷达日渐复杂的测试挑战不可或缺的要件。

(本文作者为NI国家仪器RF产品行销经理)

-

雷达系统

+关注

关注

6文章

220浏览量

28452

发布评论请先 登录

相关推荐

模组化基础仪器势力抬头 性价比更高

缩减LED/功率元件测试成本 PXI模组化SMU亮相

规格大翻新 是德模组化测试方案重装上阵

加快MIMO测试速度和降低测试成本的方法

可提高测试吞吐量并降低测试成本的LTE无线综测解决方案

什么是测试成本?(如测试测量 设备、自动元器件处理设备等)

利用测试排序仪器降低测试成本

弹片微针模组可满足屏下指纹模组的测试需求

虹科电源测试系统,实现更高的测试密度和更低的测试成本

多功能雷达增加测试成本模组化测试平台满足需求

多功能雷达增加测试成本模组化测试平台满足需求

评论