PLDA的XpressRICH4™和XpressRICH4-AXI™为Xilinx® Virtex® Ultrascale+™ FPGA提供PCIe 4.0 v0.9支持,为FPGA技术提供最先进、最高性能的互连技术。

PLDA今日宣布推出在FPGA上支持PCIe® 4.0 v0.9的PCIe软IP解决方案。PLDA的XpressRICH4™和XpressRICH4-AXI™ IP解决方案已证明具有可靠的可靠性,许多ASIC和SoC已经投入生产。

PLDA PCIe 4.0软IP解决方案现在支持最新功能,这些功能已强制纳入PCIe 4.0规范,包括支持EIEOS。

此外,经在由PCIe 4.0 x86提供支持的早期平台(具有端到端DMA流量)上验证,面向Virtex Ultrascale+的PLDA PCIe 4.0软IP在硬件中的运行速度为16GT/s。这些测试证明PLDA PCIe 4.0 IP在PLDA的PCIe 3.0至PCIe 4.0透明模式交换机上运行时可实现最大的吞吐量。

欢迎光临TSMC OIP圣克拉拉(9月13日)和IP SoC上海(9月14日)研讨会,您将有机会认识我们的团队、参观我们的演示会并了解我们的PCIe 4.0解决方案

关于PLDA XpressRICH4:PLDA的XpressRICH4是一种高度可配置的PCIe 4.0接口软IP,支持端点、根端口、交换机、桥接器以及SR-IOV、多功能、数据保护(ECC、ECRC)、ATS、TPH、 AER等高级功能。

关于PLDA XpressRICH4-AXI:PLDA的XpressRICH4-AXI是一种企业级PCIe 4.0接口软IP,具有可配置的AMBA AXI3/AXI4用户界面和高性能DMA、地址转换、排序规则监督、ECAM、数据保护(ECC、ECRC)。支持SR-IOV、6 BARs+ EPROM和开放式中断接口。

关于PLDA XpressSWITCH:XpressSWITCH是一款可定制的嵌入式PCIe交换机,专为ASIC和FPGA实现而设计,支持一个上行端口和多个下行端口连接,提供大量的配置选择。该产品支持PCIe 3.0至PCIe 4.0交换机。

关于PLDA检测仪:该检测仪是一个PCI Express 4.0 主机平台,适用于PCIe 4.0硅芯片、设备和软件的诊断和性能优化。它支持在L0阶段前和L0阶段后诊断PHY和链路问题,测试您的通道边限电路并在x86环境中验证和优化你的PCIe 4.0设备性能。

关于PLDA20多年来,PLDA一直成功提供PCI和PCI Express IP。凭借逾6,200项许可证,PLDA已建立起庞大的客户群和全球最广泛的PCIe生态系统。PLDA在四代PCI Express规格中一直保持领导地位,使客户能够降低风险并加快其基于ASIC和FPGA的设计的上市时间。PLDA提供全面的PCIe解决方案,涵盖IP核、用于ASIC原型设计的FPGA电路板、PCIe BFM/试验台、PCIe驱动器和API。PLDA是一家全球性公司,在北美洲(加州圣何塞)和欧洲(法国、意大利、保加利亚)设有办事处。

往期精彩回顾一个新颖的系统架构: Kintex-7 FPGA + Nvidia TX2 = 16通道高速ADC数据采集系统

Xilinx、Arm、Cadence和台积公司共同宣布全球首款采用7纳米工艺的CCIX测试芯片

【专家坐堂Q&A】我无法在我的 IPI 设计中仿真 MicroBlaze MCS

震惊! 基于 Xilinx Kintex UltraScale实现nvNITRO NVMe超高速加速器卡

Xilinx 助力华为 FPGA 加速云服务器,将机器学习、数据分析与视频处理性能提升 10 倍以上

硬件云?Yes,Aldec推出基于Xilinx FPGA实现的HES硬件云台

性能飞升350%~400%!Xilinx DSP slices实现SDF 流水 FFT Core

通过Xilinx工具和Amazon EC2云上的InTime优化设计性能

售价59$的WiFi/蓝牙Pmod模块Murata 1DX上市!

-

FPGA

+关注

关注

1600文章

21281浏览量

592856 -

PLDA

+关注

关注

1文章

4浏览量

3828

原文标题:PLDA宣布面向FPGA推出支持PCIe® 4.0 v0.9的控制器,允许在FPGA上即时完成PCIe 4.0实现

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

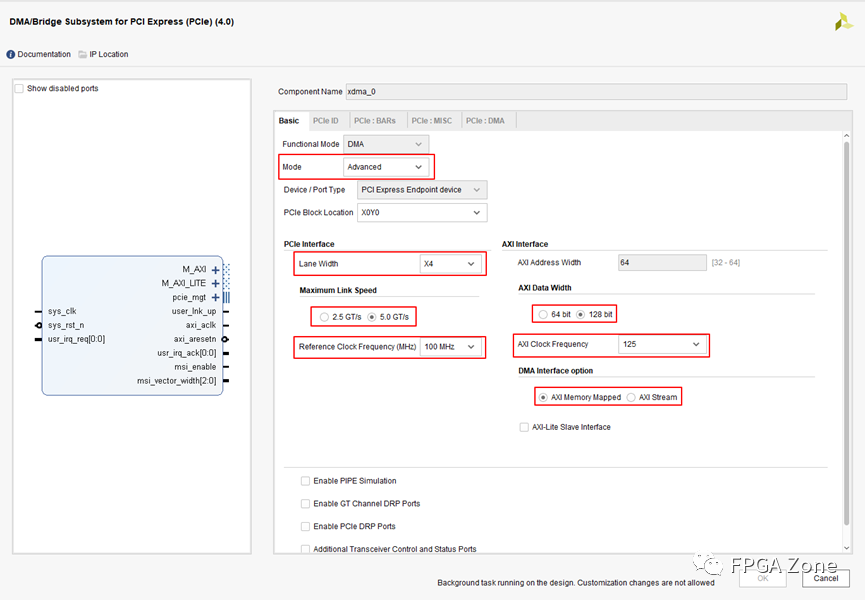

Xilinx FPGA 1/4/8通道PCIe-DMA控制器IP,高性能应用介绍

PCIe控制器(FPGA或ASIC),PCIe-AXI-Controller

【正运动】高速高精,超高实时性的PCIe EtherCAT实时运动控制卡 | PCIE464

体验紫光PCIE之使用WinDriver驱动紫光PCIE

关于xilinx FPGA pcie测试问题

pcie3.0和4.0差距大吗 怎么看pcie3.0还是4.0

紫光同创FPGA入门指导:PCIE 通信测试——紫光盘古系列50K开发板实验教程

如何读写PCIe?

英特尔发布的首款支持PCIe 5.0和CXL功能的Agilex 7 FPGA R-Tile现已量产

PLDA在FPGA上支持PCIe® 4.0 v0.9的PCIe软IP解决方案

PLDA在FPGA上支持PCIe® 4.0 v0.9的PCIe软IP解决方案

评论