在您看来,每个设计都有一个共同的问题吗?似乎总是缺少一个时序参考,设计人员想知道“他们为什么不在他们的时钟发生器上增加一个输出,或者两个,或者 10 个!?” 我将如何在我的电路板上路由所有这些时序信号!?他们的每一代董事会都有更多的董事会。

是的,很明显时钟缓冲器将有一个漫长而成功的未来。但他们遵循达尔文的理论。只有适应的缓冲器才能经受住系统工程试金石的考验。它们有用吗?它们是否简化了正时链设计?它们是否能与时序链的其余部分无缝协作,并因其在信号链中的功能和差异化(尺寸、功率、低抖动和拥有成本)而脱颖而出?

这是客户长期以来一直依赖 IDT 的设计的一个方面——提供种类最多、质量上乘、性能卓越、多功能性最高的缓冲器或满足非常特定的系统要求。换句话说,似乎是为他们准备的缓冲区。

IDT 拥有业内最广泛的高性能缓冲器产品组合,我将介绍一个非常有用的简单但功能强大的缓冲器系列。这些非常适合许多不同的应用,尤其是在有线通信领域。

1PPS 或更高,几乎没有任何抖动影响,高度灵活,占用空间小

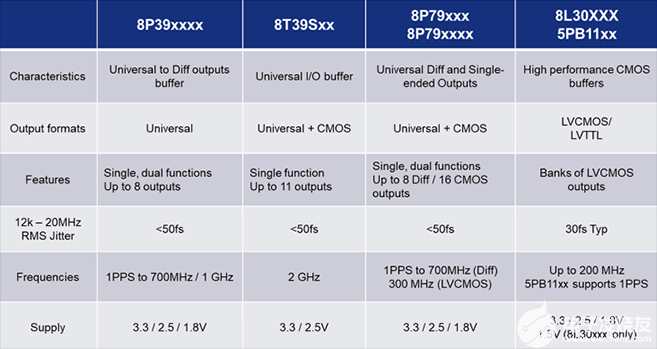

让我们从8P39xx(差分)和8P79xx 开始(差分加 CMOS)设备。这两个系列都针对有线应用进行了定制,并且设计为还支持 1PPS 信号,适用于支持这些信号同步和分配的应用。通过避免内部 AC 耦合,在 1PPS 等足够低的频率下工作时,VOH 和 VOL 不会漂移。它们还涵盖了有线应用中使用的大部分或所有频率。这些缓冲器还具有非常有利的低功耗与高扇出比,以缓解系统热限制。每个 bank 可以在不同的 VDDO 下运行,因此用户可以根据特定用途定制每个输出 bank。提供无毛刺输出禁用功能以避免在启用或禁用输出时产生欠幅脉冲。

引脚绑定提供了灵活性,因此不需要串行编程。差分输入对可以接受输入电平,例如 LVPECL、LVDS、HCSL、HSTL 和单端,并且每组输出的格式可以选择为 LVPECL、LVDS、CML 或 HCSL。IDT 还以非常小的占位面积提供了所有这些灵活性、出色的 50 fs 最大附加抖动和低本底噪声。

你用水晶输入吗?没问题。8T39Sxx系列除了提供 35 fs RMS(12 kHz 至 20 MHz 集成范围)的典型附加抖动性能和 80ps 最大输出到输出偏移之外,还将添加一个集成晶体振荡器。

8P391208 和 8T39S08A – 高性能 8 输出缓冲器的两个示例

好处:

专为高性能有线应用而设计

设计用于支持 1 PPS 的同步应用

具有高扇出的最低功耗

极低的附加抖动,可实现最佳 SNR、数据速率优化和低 BER

无需编程——上电就绪(三态引脚)

降低拥有成本的灵活性(格式、1 或 2 个集成缓冲器)

只需要一个非常简单但高性能的 CMOS 缓冲器?

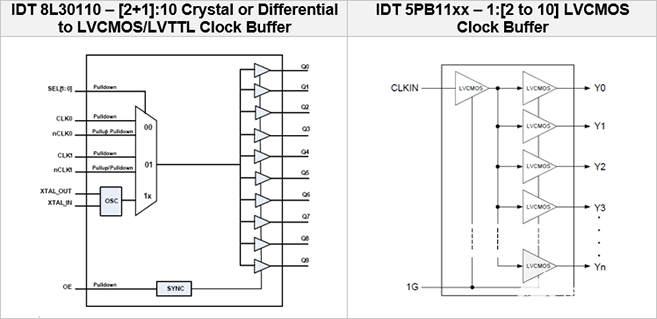

IDT 提供8L301xx系列 CMOS 缓冲器。例如,8L30110 在 5x5 封装中提供多达 10 个输出,具有所有基本功能,但仅此而已。24 fs 的典型附加抖动几乎不会影响应用的总抖动预算。还提供无毛刺 OE 和 XTAL 振荡器。这些缓冲器还提供输入多路复用器,因此用户可以在两个不同的输入或 XTAL 输入之间进行选择。

IDT 还提供另一个更简单的 CMOS 缓冲器系列,即5PB11xx系列,由五个时钟扇出缓冲器成员组成,其中最后两位数字代表输出数量。这些缓冲器是非常高性能、低抖动、低偏移和传播延迟、非常低功耗的直接 CMOS 扇出缓冲器。

高性能低功耗 CMOS 时钟扇出缓冲器 – 8L30110 和 5PB11xx 系列示例

好处:

专为高性能有线应用而设计

非常低的功率允许在几乎不考虑散热和功率/散热的情况下进行分配

非常低的附加抖动,对总抖动预算几乎没有影响

无需编程 – 开机准备就绪

8L30xx 系列提供 XTAL 输入和输入多路复用器的可能性

5PB11xx 支持 1PPS 分配

5PB11xx 系列具有完全表征的传播延迟

TSSOP 和 DFN/QFN 封装,小至 2 × 2 mm

时钟缓冲器系列概述

工程师发现这些缓冲器在一系列应用中非常实用和有用,包括:

GPON OLT 和 DSL DSLAM 提供低功耗、电压和格式灵活性以及抖动性能

PTN/OTN 和核心网络的性能和灵活性

可轻松将时钟分配到 FPGA 和以太网 PHY 的企业交换机

性能、功能和简单性的数据中心

PON ONT 或 DSL CPE 用于 CMOS 缓冲器系列和内部晶体振荡器的成本效益、低功耗和小尺寸

审核编辑:郭婷

-

CMOS

+关注

关注

58文章

5146浏览量

233312 -

振荡器

+关注

关注

28文章

3513浏览量

137626 -

缓冲器

+关注

关注

6文章

1566浏览量

44868

发布评论请先 登录

相关推荐

矽力杰高性能20路PCIe时钟缓冲器

请问如何将缓冲器与AD8221搭配使用 ?

时钟信号的同步 在数字电路里怎样让两个不同步的时钟信号同步?

如何设计和使用缓冲器

三态输出的缓冲器有哪些用途?

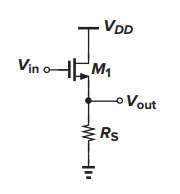

为什么共漏级又称为源极跟随器、电压缓冲器?

MAX13256的缓冲器设计

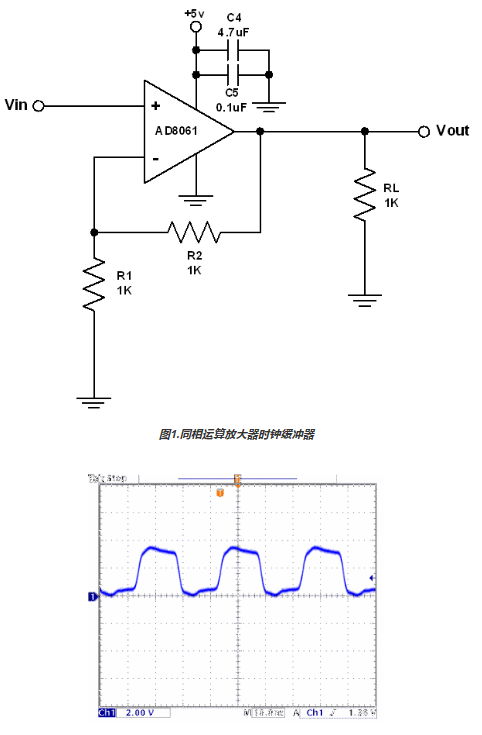

廉价的高速放大器提供灵活的时钟缓冲器

高性能时钟缓冲器HMC7043介绍

源跟随器作为缓冲器的使用

使用IDT时钟缓冲器提升应用设计

使用IDT时钟缓冲器提升应用设计

评论