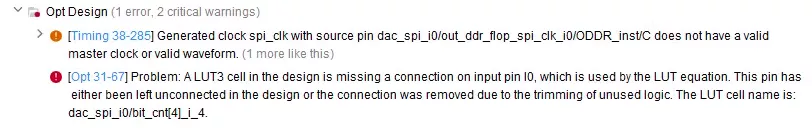

在Vivado中,可能由于某些逻辑输入悬空而导致Implementation的opt_design时会错,比如:

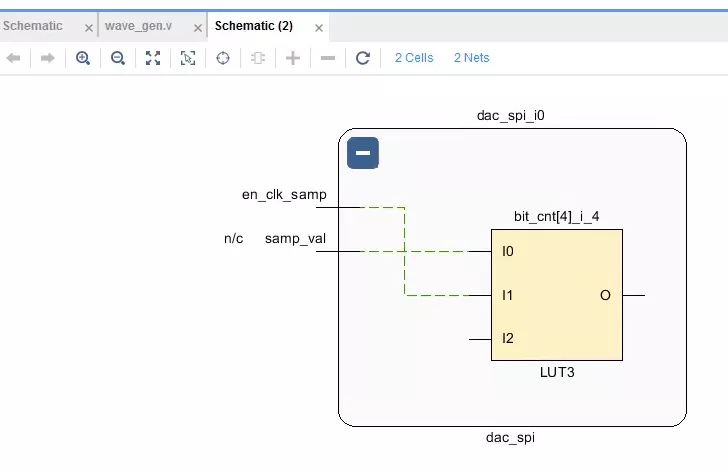

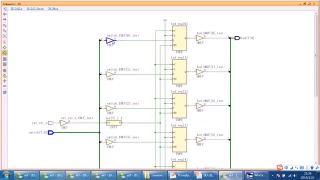

报的错误是dac_spi_i0/bit_cnt[4]_i_4的这个LUT有个输入悬空了,这个工程的逻辑比较简单,例化的嵌套也比较少,因此在schematic一层层找也很容易可以找到,但如果工程比较复杂,在很内部的一个LUT的输入悬空了,找起来就很费劲了。

笔者碰到的问题是在vivado的axi-interconnect ip中报了这个错误,而且是ip内部套了好几层的地方,如果再一层层往下找就比较麻烦了,不过vivado提供了tcl指令可以帮我们快速找到这个LUT在schematic中的位置:

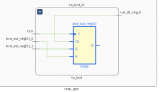

show_schematic [get_cells dac_spi_i0/bit_cnt[4]_i_4]

就会快速定位到schematic中的位置:

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

指令

+关注

关注

1文章

577浏览量

35360 -

逻辑

+关注

关注

2文章

818浏览量

29289 -

Vivado

+关注

关注

18文章

787浏览量

65084

发布评论请先 登录

相关推荐

如何快速找到PCB中的GND?

如何快速找到PCB中的GND? 在PCB设计和制作过程中,找到地线(GND)是非常关键的步骤。GND是电子电路中一个非常重要的参考面,它提供了电路中的参考电平,并在电路中提供低噪声的当前路径。因此

串联谐振怎么使用才能快速找到谐振点

串联谐振怎么使用才能快速找到谐振点 串联谐振是指通过串联电路中的电感和电容来实现谐振的现象。谐振是一个非常重要的电路现象,在无线电通信领域、音频信号处理领域等都有广泛的应用。在设计和调整串联谐振

sigmastudio没有找到Schematic Terminal ,是版本的问题吗?

sigmastudio没有找到Schematic Terminal ,是版本的问题吗?

发表于 11-29 07:37

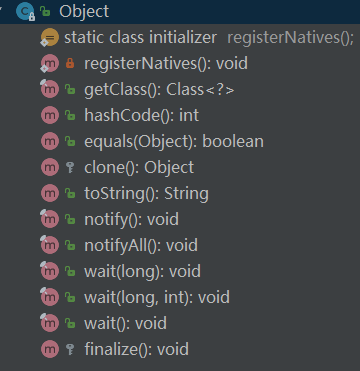

Object类中的所有方法

Object 类属于 java.lang 包,此包下的所有类在使用时无需手动导入,系统会在程序编译期间自动导入。Object 类是所有类的基类,当一个类没有直接继承某个类时,默认继承Object

Vivado设计套件用户:使用Vivado IDE的指南

电子发烧友网站提供《Vivado设计套件用户:使用Vivado IDE的指南.pdf》资料免费下载

发表于 09-13 15:25

•5次下载

Vivado使用指南

TakeVideos:快速使用的视频连接口,关联到DocNav,并筛选出Vivado使用的一些教学视频;Release NotesGuide:在DocNav中打开Vivado rel

发表于 09-06 17:55

Vivado怎么快速找到schematic中的object

Vivado怎么快速找到schematic中的object

评论