传统上,汽车中的计算任务由微控制器单元 (MCU) 和应用处理器 (AP) 执行。一辆典型的中档汽车可以包含 25 到 35 个 MCU/AP,而豪华车可能使用 70 个或更多。越来越多的汽车需要极其复杂的计算密集型功能来完成高级驾驶辅助系统 (ADAS)、信息娱乐、控制、网络和安全等任务。其中许多应用涉及图像和视频处理形式的机器视觉以及人工智能 (AI)。

单独的处理器架构很难处理传感器、相机和显示器等外围设备所需的所有电气接口和协议。此外,在许多情况下,这些处理器根本无法满足机器视觉和人工智能等任务的极端计算需求。

为了解决这种复杂性,汽车系统的设计人员正在转向现场可编程门阵列 (FPGA),而不是取代现有的 MCU/AP,而是充当它们与其他设备之间的桥梁,并通过卸载通信和其他计算密集型任务。

由于可以对 FPGA 进行编程以支持各种电气接口和协议,因此它们可以充当 MCU/AP 与传感器、摄像头和显示器之间的桥梁。此外,由于它们可以以大规模并行方式执行计算和操作,FPGA 可用于执行计算密集型视觉处理和 AI 任务,从而腾出主机处理器用于其他活动。

本文讨论了现代汽车的处理要求,并描述了 FPGA 可以解决的一些汽车应用。然后介绍了莱迪思半导体的一些示例 FPGA,并展示了如何使用它们来解决连接、处理和安全问题。还提供了相关的开发板以帮助设计人员入门。

FPGA 的目标汽车应用

为了支持其 ADAS 功能,当今的汽车在车外采用了许多传感器,包括摄像头、雷达、激光雷达和超声波检测器。在许多情况下,有必要从不同的传感器获取数据,对这些数据进行预处理(去除噪声并根据需要对其进行格式化),并使用传感器融合来组合数据,从而使所得信息的不确定性低于如果来自不同传感器的数据将单独使用。在许多情况下,人工智能应用程序被用来分析数据、做出决策并采取适当的行动。

一个相对较新的趋势是部署电子(也称为“数字”)后视镜。在这种情况下,后窗内安装了广角高分辨率摄像头。来自该摄像头的视频流显示在数字显示屏上,取代了传统的镜子,从而形成清晰的后方视野,不受后座乘客的阻碍。在某些情况下,来自安装在后视镜上的摄像头的视频流可能会与来自后窗摄像头的视频流合并。这三个信息被“拼接在一起”,以提供在超宽电子镜上呈现的单一图像,从而使驾驶员对车辆周围发生的情况有更高程度的态势感知。

最近的另一个趋势是在仪表板上、转向柱上或集成到后视镜(常规或电子)中部署车内摄像头。当与 AI 结合使用时,这些车内后视镜可用于各种任务,例如识别谁坐在驾驶座上并相应地调整后视镜和后视镜。除了监控司机以确保他们注意道路而不是打瞌睡外,这样的系统还可以寻找困倦的迹象,以及医疗问题或痛苦,如癫痫发作或心脏病发作,并采取适当的措施行动。这些操作可能包括激活危险警告灯、应用刹车以及将车辆引导到路边。

对于基于视频的应用,在某些情况下,需要将单个视频输入拆分为多个流;在其他情况下,设计要求可能是将多个视频流聚合为一个。

随着电动汽车 (EV) 的日益普及,需要监控和控制电机,以及监控和管理充电过程以实现最长的电池寿命。

最重要的是,当今的许多汽车都开始支持 5G 或 V2X,其中 V2X(“车辆到任何事物”)是指车辆与可能影响(或受其影响)车辆的任何其他实体之间的通信,从路边基础设施到其他车辆。除了这种连接性之外,还需要安全性以防止车辆被黑客入侵。

汽车级设备

重要的是要记住,并非所有 FPGA 都适合汽车应用。汽车电子委员会 (AEC) 最初是由克莱斯勒、福特和 GM 于 1990 年代成立的一个组织,目的是建立通用零件鉴定和质量体系标准。最常被引用的 AEC 文件之一是 AEC-Q100,“基于失效机制的集成电路压力测试认证”。

IATF 16949:2016 是一项技术规范,旨在开发质量管理体系,提供持续改进、强调缺陷预防以及减少汽车行业供应链和装配过程中的变化和浪费。IATF 16949:2016 基于 ISO 9001 标准,由国际汽车工作组 (IATF) 和 ISO 技术委员会创建。

汽车市场的电子系统供应商越来越要求半导体供应商提供符合 AEC-Q100 标准的产品,并且能够证明其质量体系的 ISO/TS-16949 认证。

为工作选择正确的 FPGA

FPGA 非常灵活,但不同的器件系列提供了各种能力和功能组合,使其更适合特定任务。例如,在嵌入式视觉应用中,现代相机和显示器通常采用 MIPI 接口。MIPI CSI-2(摄像头/传感器)和 DSI(显示器)协议都采用称为 D-PHY 的通信物理层 (PHY)。传统 MCU/AP 可能不支持此接口,但一些 FPGA 支持,例如莱迪思半导体的 CrossLink-NX 嵌入式视觉和处理 FPGA。

除了两个强化的四通道 MIPI D-PHY 收发器,每个 PHY 支持 10 Gb/s (Gbits/s),CrossLink-NX 设备还支持 5 Gbits/s PCIe、1.5 Gbits/s 可编程输入/输出 (I/O ) 和 1066 兆位每秒 (Mbits/s) DDR3。这些器件还支持传统的电气接口和协议,如低压差分信号 (LVDS)、Sub-LVDS(LVDS 的降压版本)、开放式 LVDS 显示接口 (OLDI) 和串行千兆位媒体独立接口 (SGMII) . 因此,这些设备可用于聚合视频流、拆分视频流、运行 AI 应用程序,并且在执行所有这些操作的同时,还可充当传统 MCU/AP 与现代传感器和显示器之间的桥梁。

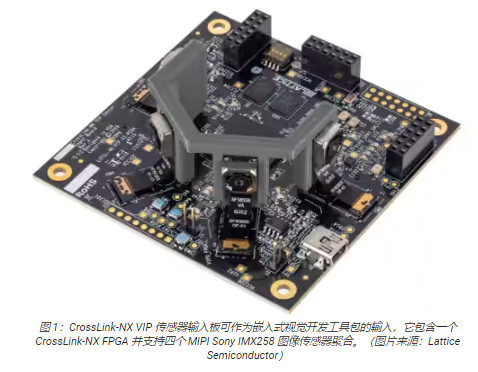

希望评估 CrossLink-NX FPGA 的汽车系统开发人员会发现LIFCL-VIP-SI-EVN CrossLink-NX VIP 传感器输入板(图 1)和LF-EVDK1-EVN模块化嵌入式视觉套件的组合很有趣(前者可以作为后者的输入板)。除了 CrossLink-NX FPGA,传感器输入板还配备四个 13 兆像素索尼 IMX258 CMOS MIPI 图像传感器,支持 4K2K @ 30 帧每秒 (fps) 或 1080p @ 60 fps。它还支持通过三个独立的 PMOD 接口轻松连接传感器。

图 1:可作为嵌入式视觉开发套件输入的 CrossLink-NX VIP 传感器输入板包含一个 CrossLink-NX FPGA,并支持四个 MIPI Sony IMX258 图像传感器的聚合。(图片来源:莱迪思半导体)

对于同样需要高 I/O 带宽的计算密集型应用,例如用于手势识别和控制、语音识别和控制、人体存在检测、乘员识别和驾驶员监控等任务的 AI,莱迪思的 ECP5 FPGA 具有高达 3.2 Gbit/串行器/解串器 (SERDES),双通道块中每个器件最多四个通道,以实现更高粒度,多达 85K 查找表 (LUT),增强型数字信号处理 (DSP) 块,可为对称滤波器提供 2 倍的资源改进,以及单事件扰乱 (SEU) 缓解支持。这些 FPGA 还为 LVCMOS 33/25/18/15/12、XGMII、LVTTL、LVDS、Bus-LVDS、7:1 LVDS、LVPECL 和 MIPI D-PHY I/O 接口提供可编程 I/O 支持。

一个示例 ECP5 设备是LFE5U-85F-6BG554C,具有 84,000 个逻辑元件、3.75 兆位 (Mbits) 的 RAM 和 259 个 I/O。LFE5UM-45F-VERSA-EVNG ECP5 Versa 开发套件也令人感兴趣(图 2)。该板采用半长 PCI Express (PCIe) 外形尺寸,允许设计人员评估 ECP5 FPGA 的关键连接特性,包括 PCIe、千兆以太网 (GbE)、DDR3 和通用 SERDES 性能。

图 2:ECPe Versa 开发套件采用半长 PCI Express 外形尺寸,让设计人员能够评估 ECP5 FPGA 的关键连接特性,包括 PCIe、GbE、DDR3 和通用 SERDES 性能。(图片来源:莱迪思半导体)

使用 FPGA 保护汽车

来自黑客的安全威胁正在增加,新的违规行为不断发生。就汽车而言,网络攻击可能导致失控,导致乘客和行人受伤或死亡,以及汽车、其他车辆和财产损失。

汽车安全解决方案的很大一部分是建立信任根(RoT);即系统中始终可以信任的硬件资源。一种解决方案是基于 FPGA 的硬件 RoT (HRoT),例如莱迪思的 MachXO3D 系列器件提供的解决方案。除了大量 LUT 资源和大量 I/O 之外,这些基于闪存的设备还提供即时启动和热插拔功能。通用应用包括胶合逻辑、总线桥接、总线接口、电机控制、上电控制和其他控制逻辑应用。

特别令人感兴趣的是,MachXO3D 是唯一一款同时具备双引导功能和少于 10K LUT 的 FPGA,它配备了经过国家标准与技术研究院 (NIST) 认证的硬性不可变安全引擎。这使得 MachXO3D 可以作为汽车的 HRoT 以系统的先启动后关闭设备的形式出现。系统通电后,MachXO3D 首先会检查以确保它正在运行经过验证的固件。然后它检查系统中其他设备的固件。如果系统中的任何组件(包括其自身)受到攻击或破坏,MachXO3D 会拒绝可疑固件并使用已知良好、经过验证的固件映像重新加载该组件。

对于有兴趣评估基于 MachXO3D 的设计的开发人员,LCMXO3D-9400HC-D-EVN MachXO3D 开发板提供了一个可扩展的原型设计平台(图 3)。该板具有 L-ASC10(模拟传感和控制)硬件管理设备、用于 Arduino 和 Raspberry Pi 板的通用 I/O 接口、两个 Hirose FX12-40 接头位置 (DNI)、Aardvark 接头 (DNI ) 和 128 Mbit 串行外设接口 (SPI) 闪存,具有四重读取功能。

图 3:MachXO3D 开发板具有一个 MachXO3D FPGA、一个 L-ASC10(模拟传感和控制)硬件管理设备、支持 Arduino 和 Raspberry Pi 板、两个 Hirose FX12-40 接头位置 (DNI)、一个 Aardvark 接头和用于设备编程的 USB-B 连接。(图片来源:莱迪思半导体)

该板采用 4 x 6 英寸外形尺寸,具有用于供电和编程的 USB mini-B 连接器,以及支持 Arduino、Aardvark、FX12、Hirose 和 Raspberry Pi 的多个接头位置。随附 USB 数据线和快速入门指南。

结论

现代汽车电子需要越来越多的传感器、电气接口和协议,对处理能力和带宽也有相应的要求。人工智能和机器视觉处理以及安全要求的增加使使用经典 MCU 或 AP 方法的解决方案实施变得复杂。

如图所示,通过适当应用 FPGA,设计人员可以增加一定程度的灵活性和处理能力,以桥接不同的处理环境,执行传感器聚合和融合功能,满足 I/O 带宽要求,并以大规模并行方式执行计算和操作,同时释放主机处理器用于其他活动。

在安全方面,具有双启动功能和 NIST 认证的不可变安全引擎的基于闪存的 FPGA 可以充当汽车的 HRoT,并确保它和其他设备仅运行经过身份验证的固件,从而防止黑客以密码方式破坏汽车系统.

审核编辑:符乾江

-

FPGA

+关注

关注

1602文章

21309浏览量

593128 -

AI

+关注

关注

87文章

26424浏览量

264029 -

汽车系统

+关注

关注

1文章

126浏览量

19541

发布评论请先 登录

相关推荐

为汽车接口、安全和计算密集型负载选择和使用 FPGA

什么是FPGA?带你初步揭开它的面纱

鸿蒙原生应用开发-ArkTS语言基础类库多线程CPU密集型任务TaskPool

鸿蒙原生应用开发-ArkTS语言基础类库多线程I/O密集型任务开发

什么是DWDM密集型光波复用?DWDM产品有哪些?

计算密集型的程序简析

HarmonyOS CPU与I/O密集型任务开发指导

软件密集型装备故障的静态检测

新型处理器的数据密集型计算

虹科│还在为数据密集型计算环境下的存储连接而烦恼吗?

用于密集型在轨边缘计算的微处理器和FPGA

用于汽车接口、安全和计算密集型负载FPGA的选择和使用

用于汽车接口、安全和计算密集型负载FPGA的选择和使用

评论