美国时间12月2日,RISC-V国际基金会宣布其成员批准了15项新规范,包含了RISC-V指令集架构下的40多个扩展,其中重点强调的就是其矢量、标量加密和Hypervisor三条规范。RISC-V国际基金会表示,这些规范为AI、机器学习、IoT、汽车和数据中心等市场创建了新的机遇,那么对于RISC-V这个仍在蓬勃发展的架构来说,这些规范究竟意味着什么呢?

向量处理

过去向量计算往往只用于气象预报和声呐研究等细分市场,如今人工智能的兴起下,向量运算开始扩展到所有类型的应用和解决方案中,甚至在某些语音和视觉的机器学习推理中成了主要运算方式。

RISC-V的向量规范带来的RISC-V向量扩展,为数据运算密集的应用敞开了大门。该扩展已于今年9月进入冻结公共审核阶段,如今终于通过批准。RISC-V的向量扩展仅有100多条指令,但凭借这些指令,开发者就可以在RISC-V架构的处理器上迅速应对复杂的运算工作,比如稀疏矩阵运算等,并做到极低的延迟。

RISC-V向量扩展中还有针对嵌入式设备和MCU的扩展Zve,为性能不高的RISC-V CPU核心提供32/64整数、单精度和双精度的浮点向量运算,满足边缘端日益增长的算力要求。这样不论是消费级的IoT设备,还是工业级的机器学习应用,都能从中获利。

标量加密

安全是任何一个架构都不容小觑的一环,从支持安全的加密标准到防范x86曾遇到的Spectre和Meltdown等漏洞,RISC-V在加密上同样没有放松。

标量加密规范将为小规模的加密工作带来加速,这些扩展显著降低了物联网和嵌入式设备中安全高效的加速加密技术门槛。标量加密扩展的引入,使得RISC-V在实现某些标准的哈希加密或分组加密算法时,要比直接使用标准指令快一个数量级。

根据RISC-V国际基金会CTO Mark Himelstein的说法,在使用标量加密扩展后,64位的RISC-V运行AES128加密算法所需指令数从1145条下降至78条,提升性能的同时也加强了对边信道攻击的防范。除了性能和安全优势外,引入标量加密扩展所需成本也非常低,不需要像向量处理器一样占用芯片大量的逻辑空间,开发者可以将目前主流的加密算法集成到最小的设备中。

Hypervisor虚拟化

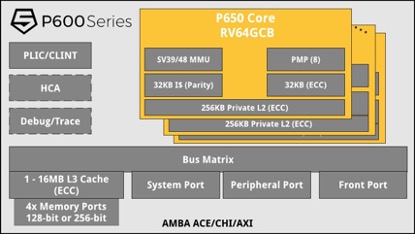

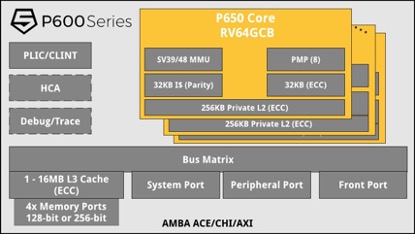

虚拟化支持也是如今常见的需求之一,无论是数据中心还是嵌入式设备,都开始引入虚拟化技术。RISC-V的虚拟化扩展已经停留在草案阶段许久了,如今终于获得批准,RISC-V社区已经完成了KVM的移植,Linux 5.16版本中的KVM也将正式支持RISC-V的hypervisor扩展,另一大开源虚拟机Xen也在今年三月宣布将考虑支持RISC-V的虚拟化。而SiFive在同一天公布的SiFive P650处理器,也声称支持虚拟化。

P650处理器 / SiFive

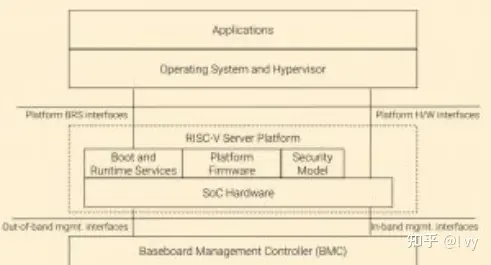

虚拟化技术主要是实现CPU、内存和I/O的虚拟化。RISC-V通过赋予敏感寄存器和指令特权的方式,实现了CPU的虚拟化。在内存虚拟化上,RISC-V和Arm/x86一样,选择实用多阶段页表来实现。RISC-V的Hypervisor规范将supervisor级的架构虚拟化,有效地以type-1或KVM这类type-2的形式托管运行客户操作系统。

RISC-V凭借其扩展性,已经展现了作为加速器的无限潜力,有了虚拟化技术的支持,RISC-V的硬件资源可以得到最大限度的利用,在数据中心的机器和网络基础架构中也将获得更多的机会。

除了数据中心,汽车和工业控制应用也已经全面铺开虚拟化技术,比如UI与控制应用的硬件隔离等等。这也是RISC-V存在感较小的两大市场,有了虚拟化技术的支持,相信RISC-V能够吸引到更多的行业玩家。

小结

尽管RISC-V仍是全球ISA市场中的一小部分,但根据调研机构近期发布的报告,RISC-V的处理器核心将在2022年和2023年实现翻倍式增长。尤其是在这些新规范和新扩展的加入下,欲求快速进入市场的初创小型公司更愿意选择这种开放式的架构。

向量处理

过去向量计算往往只用于气象预报和声呐研究等细分市场,如今人工智能的兴起下,向量运算开始扩展到所有类型的应用和解决方案中,甚至在某些语音和视觉的机器学习推理中成了主要运算方式。

RISC-V的向量规范带来的RISC-V向量扩展,为数据运算密集的应用敞开了大门。该扩展已于今年9月进入冻结公共审核阶段,如今终于通过批准。RISC-V的向量扩展仅有100多条指令,但凭借这些指令,开发者就可以在RISC-V架构的处理器上迅速应对复杂的运算工作,比如稀疏矩阵运算等,并做到极低的延迟。

RISC-V向量扩展中还有针对嵌入式设备和MCU的扩展Zve,为性能不高的RISC-V CPU核心提供32/64整数、单精度和双精度的浮点向量运算,满足边缘端日益增长的算力要求。这样不论是消费级的IoT设备,还是工业级的机器学习应用,都能从中获利。

标量加密

安全是任何一个架构都不容小觑的一环,从支持安全的加密标准到防范x86曾遇到的Spectre和Meltdown等漏洞,RISC-V在加密上同样没有放松。

标量加密规范将为小规模的加密工作带来加速,这些扩展显著降低了物联网和嵌入式设备中安全高效的加速加密技术门槛。标量加密扩展的引入,使得RISC-V在实现某些标准的哈希加密或分组加密算法时,要比直接使用标准指令快一个数量级。

根据RISC-V国际基金会CTO Mark Himelstein的说法,在使用标量加密扩展后,64位的RISC-V运行AES128加密算法所需指令数从1145条下降至78条,提升性能的同时也加强了对边信道攻击的防范。除了性能和安全优势外,引入标量加密扩展所需成本也非常低,不需要像向量处理器一样占用芯片大量的逻辑空间,开发者可以将目前主流的加密算法集成到最小的设备中。

Hypervisor虚拟化

虚拟化支持也是如今常见的需求之一,无论是数据中心还是嵌入式设备,都开始引入虚拟化技术。RISC-V的虚拟化扩展已经停留在草案阶段许久了,如今终于获得批准,RISC-V社区已经完成了KVM的移植,Linux 5.16版本中的KVM也将正式支持RISC-V的hypervisor扩展,另一大开源虚拟机Xen也在今年三月宣布将考虑支持RISC-V的虚拟化。而SiFive在同一天公布的SiFive P650处理器,也声称支持虚拟化。

P650处理器 / SiFive

虚拟化技术主要是实现CPU、内存和I/O的虚拟化。RISC-V通过赋予敏感寄存器和指令特权的方式,实现了CPU的虚拟化。在内存虚拟化上,RISC-V和Arm/x86一样,选择实用多阶段页表来实现。RISC-V的Hypervisor规范将supervisor级的架构虚拟化,有效地以type-1或KVM这类type-2的形式托管运行客户操作系统。

RISC-V凭借其扩展性,已经展现了作为加速器的无限潜力,有了虚拟化技术的支持,RISC-V的硬件资源可以得到最大限度的利用,在数据中心的机器和网络基础架构中也将获得更多的机会。

除了数据中心,汽车和工业控制应用也已经全面铺开虚拟化技术,比如UI与控制应用的硬件隔离等等。这也是RISC-V存在感较小的两大市场,有了虚拟化技术的支持,相信RISC-V能够吸引到更多的行业玩家。

小结

尽管RISC-V仍是全球ISA市场中的一小部分,但根据调研机构近期发布的报告,RISC-V的处理器核心将在2022年和2023年实现翻倍式增长。尤其是在这些新规范和新扩展的加入下,欲求快速进入市场的初创小型公司更愿意选择这种开放式的架构。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

cpu

+关注

关注

68文章

10412浏览量

206468 -

加密算法

+关注

关注

0文章

205浏览量

25407 -

RISC-V

+关注

关注

41文章

1888浏览量

45029

发布评论请先 登录

相关推荐

浅谈RISC-V微架构验证方式

RISC-V 是一个开放的 ISA,任何人都可以接受它并实现处理器。但RISC-V市场的领导者知道,仅仅因为他们不需要支付许可使用费,并不意味着RISC-V是便宜的选择。

发表于 04-15 11:34

•42次阅读

RISC-V 基础学习:RISC-V 基础介绍

是什么?

RISC-V 是一套开放许可证书、免费的、由基金维护的、一个整数运算指令集外加多个扩展指令集的CPU 结构规范(ISA)。

整数运算指令集 + 扩展指令集

任何硬件开发商或者组织都可以

发表于 03-12 10:25

RISC-V的迷人之处

RISC-V的迷人之处之一是它是如此……灵活。作为开源处理器规范,绝对任何人都可以使用它,对其进行修改并将其商业化。没有许可费,没有规则,也没有兼容性测试。这是处理器的狂野西部。在一定程度上。

但是

发表于 02-12 20:58

【RISC-V开放架构设计之道|阅读体验】RISC-V基础整数指令集

第2章 RV32I:RISC-V基础整数指令集

本章重点讲解构成RISC-V基础整数指令集的基本指令和指令格式。主要包含寄存器间操作的R型,用于短立即数和取数操作的I型,用于存数操作的S型,用于条件

发表于 01-31 21:10

RISC-V生态强劲 RISC-V International会员超4000 超75个技术工作组

的 4,000 多名成员,拥有超过 75 个技术工作组,推动 RISC-V 标准、软件、工具等方面的进展。仅今年一年,RISC-V 就批准了 12 项规范,还有更多

备胎的RISC-V在努力,又将走向何方

,并鼓励硬件开发者对指令的修改按照这种规范进行,以此解决架构开源带来的软、硬件不兼容问题。

一个典型的例子是阿里平头哥玄铁C908,就通过了RISC-V根据其指令集修改规范设置的兼容性测试,这

发表于 09-30 12:28

谈一谈ARM上市与RISC-V

,消费电子市场的收缩就意味着Arm营收的收缩。

替代Arm,中国厂商普遍将目光望向了RISC-V。

如果将时间调回2020年,彼时RISC-V基金会总部刚从美国搬迁到瑞士,RISC-V

发表于 09-30 12:22

2023 RISC-V中国峰会:RISC-V深圳技术分享会(同期会议)

本届峰会将以“RISC-V生态共建”为主题,结合当下全球新形势,把握全球新时机,呈现RISC-V全球新观点、新趋势。

由电子发烧友主办的RISC-V技术分享会(深圳站)将于8月26日在深圳举办

发表于 08-15 17:27

RISC-V在快速发展的处理器生态系统中找到立足点

of the architecture into their own chip.

RISC-V是一种免费许可的架构,这意味着任何人都可以将架构的一个版本分叉到自己的芯片中。

Chips with RISC-V can

发表于 08-11 18:20

RISC-V走向开放服务器规范

RISC-V International目前正在起草一份可以标准化RISC-V服务器芯片和系统开发的规范,RISC-V International是一个处理指令集架构开发的组织。

两大架构RISC-V 和 ARM 的各种关系

RISC-V 是一种开源架构,而 ARM 是专有的。

这意味着任何想要在其设计(例如 SoC)中包含 ARM CPU 的设计师都必须向 ARM Holdings 支付版税。另一方面,RISC-V 是开源

发表于 06-21 20:31

RISC-V,正在摆脱低端

”期间,北京开源芯片研究院首席科学家包云岗表示,中美企业正在研发高性能RISC-V处理器,总体处于第一梯队。国内初创企业数量远大于美国,产品主要集中在MCU级。

然而,在物联网领域大受追捧,并不意味着

发表于 05-30 14:11

RISC-V如何保证高权限模式程序及外设的安全性?

RISC-V有机器模式、监管模式和用户模块,但无论在哪个模式下当TRAP发生时都会转到机器模式,是不是也就意味着在用户模式下进入中断服务程序也会拥有机器模式的权限,那我们如何保证高权限模式程序及外设的安全性?

发表于 05-26 08:11

Datasheet v1.2更新到v1.4意味着什么?

38 BOD 静态特性中:

问题:此表从 Datasheet v1.2 更新到 v1.4 意味着什么?这是否意味着不再支持小于 1.75V

发表于 05-04 07:07

RISC-V批准的新规范意味着什么?

RISC-V批准的新规范意味着什么?

评论