1:摩尔定律

1965年,硅谷传奇,仙童“八叛徒”之一,英特尔原首席执行官和荣誉主席,伟大的规律发现者戈登·摩尔正在准备一个关于计算机存储器发展趋势的报告。

在他开始绘制数据时,发现了一个惊人的趋势。

每个新的芯片大体上包含其前任两倍的容量,每个芯片产生的时间都是在前一个芯片产生后的18~24个月内,如果这个趋势继续,计算能力相对于时间周期将呈指数式的上升。

这个就是大名鼎鼎的摩尔定律, 其对集成电路产业的发展描述,异乎寻常的正确。

总结来说:

1:集成电路芯片(wafer)上所集成的电路的数目,每隔18个月就翻一番。

2、微处理器的性能每隔18个月提高一倍,而价格下降一半。

3、用一美元所能买到的计算机性能,每隔18个月翻两番。

你可能觉得摩尔定律平平无奇,只不过是一个总结?

其实这可以推导出了一个公式,那就是每18个月,在芯片规模不变的情况下,芯片面积减半。

这样相同的大小的wafer,可以生产出多一倍的芯片。

如果上一代工艺芯片面积是1mm2,在新工艺上,面积就是新工艺的一半,也就是0.5mm2。

我们假设两代工艺wafer成本一样(一般新工艺会贵一些),那么采用新工艺,其成本是原来工艺成本的一半。

这个就是摩尔定律揭示的现实:

那就是,采用新工艺的芯片,面积更小,功耗更优,频率更高,成本还更低。

这个就是新工艺对老工艺降维式的打击!

这些优点和好处就是驱动芯片工艺不断进步的发动机。

也就是摩尔定律的内涵。

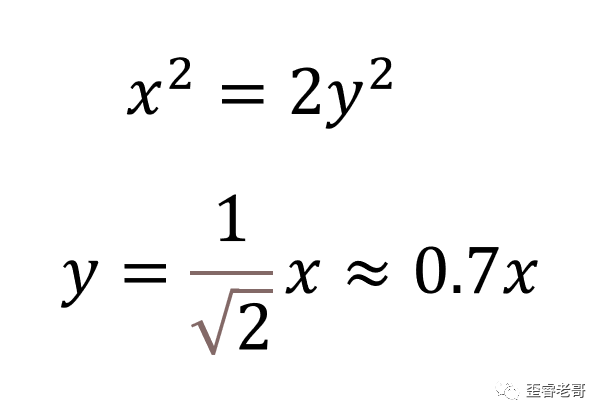

那如果芯片工艺进步,每个晶体管的尺寸就会缩小,那到底缩小多少?

晶体管数量保持不变的情况下, 下一代新工艺的芯片面积是上一代的一半。

那么X和Y什么关系。

如果我们按照正方形来计算的话?

那么新工艺大约是老工艺晶体管尺寸的0.7倍。

也就是晶体管会缩小0.7倍。

那根据摩尔定律,我们利用初中数学知识,就能算出每一代工艺的进步,从800nm开始(这个80586的工艺节点)。

而芯片工艺的发展也印证了这一点:

从0.8 μ m、0.5 μ m、0.35 μ m、0.25 μ m、0 .18 μm、0.13 μ m、90nm、65nm、45nm、32nm、22nm、16nm、10nm、7nm,5nm。

实际的工艺节点,符合了这个要求。

摩尔定律和现在芯片制程完全吻合。

神奇!

2:半节点

可能有些工艺制程知识的同学会说:

有点不对劲,

这个图里,制程很火的40nm,28nm,14nm跑哪里去了。

对,这就涉及到一个芯片制造厂常用的手段。

shrink。

我们都知道,一个工艺节点研发成功后,其研发成本是很高的。

如果可以在这个工艺节点上持续优化,面积,功耗等等。

也是一种最大化利用原有投入的方式。

就像intel就在14nm上做的一样。

14nm+++

持续优化。

而我们今天讲的shrink,也是一种优化。

它本质上是利用光照(MASK)等比例缩放后。晶体管尺寸缩小一点,芯片仍然能够正常工作,从而减少芯片面积,降低成本。

那么shrink的比例是多少?

Shrink 一般可以将晶体管的尺寸缩小0.9倍。

大约每个边长缩放为0.9;整体面积缩小0.81;

这个过程又称为,芯片收缩(die shrink)。

然而,按比例缩小可能引入新的问题,例如漏电流增大,但是通过工艺参数可以来调节漏电,shrink在不改变工艺特性的基础上,修修补补,也能挖掘这个工艺节点的潜力。

这些shrink后的工艺节点,也被人称为半节点。

例如:

40nm是45nm shrink后的半节点。

28nm是32nm shrink后的半节点。

20nm是22nm shrink后的半节点。

14nm也可以看作16nm shrink后的半节点。

把前面的工艺,乘以0.9就可以了。

DIE shrink是芯片制造厂家来做的,和芯片设计公司没有关系。

工程师设计完成的版图都是 pre shrink的,而到了厂家生产的时候,直接进行shrink,生成的die的面积比版本等比例缩小。

所以我们现在芯片设计工程师,做40nm或者28nm等半节点工艺时,都有一个shrink的流程。

会发现,芯片的版图比实际的DIE的面积要大。

如果我们计算最后的DIE(芯片)面积,实际上要算shrink之后的,而不是版图的面积。

EDA工具标注的都是shrink前(pre shrink)的面积。

那就是设计公司给了芯片制造厂一张10X10的设计图纸,而芯片厂生产的尺寸却是9x9。

这些优化后的,40nm,28nm等等,成为了更成熟和长寿的工艺。

而原有的45nm,32nm等,与优化后的40nm,28nm相比,不再具有优势,厂家不再推这些工艺工艺。

事实上,业界通常把45nm/40nm, 32nm/28nm, 22nm/20nm, 16nm/14nm 这些工艺节点,看作同一个工艺节点,是一代,只是厂家通过shrink这种手段,进行的优化。

加上shrink以后,我们看到目前的28nm,14nm,10nm,7nm,5nm都可以用摩尔定律上一节的初中数学知识算出来。

严丝合缝,理论和实际吻合的很好。

戈登。摩尔,真神人也!

3:栅极长度

但是,事实果真如此吗?

这些数字里面隐藏着一个极大的隐情。

我们来看一张图:

大约从20世纪60年代到90年代末,节点的命名是基于它们的栅极长度命名的。IEEE的此图表显示了以下关系。

栅极长度(gate length)和半节距(芯片上两个相同特征之间的距离的一半)匹配工艺节点名称,这个其实0.5um,0.35um,0.25um的一些命名的原因。

但是在28nm以下,由于采用finfet这些新的技术,这些和实际的节点和栅极长度,以及半节距(half-pitch)就匹配不上了

如果保持节点名称和实际特征尺寸同步,就会如红线所示。

2015年前,芯片制造的最小工艺尺寸就会跌破1nm。

而实际上,厂家暗渡陈仓了,

而实际上,整个工艺曲线更接近蓝线所示。

你以为的7nm,5nm,早已不是原来指的栅极长度(gate length),或者(half-pitch)半节距。

那这个7nm,5nm怎么来的。

画大饼来的!

画大饼,这个你是不是比较熟。

公司的老板最擅长搞这个,画大饼,或者叫画路线图(roadmap)。

老板说:未来三年每年增长一倍,今年销售额1亿,10年后就成为销售千亿公司。

关键是,这玩意不能这么算,按照这么算,几十年后,地球都成为你们公司的,你们销售额也完不成。

那么芯片制造的大饼,或者(roadmap)是怎么画出来的?

由于半导体制造涉及巨大的资本支出和大量的长期研究。从论文中引入新技术方法到大规模商业制造的平均时间约为10-15年。

几十年前,半导体行业认识到,如果有一个节点介绍的总体路线图以及这些节点将针对的功能尺寸,这将对参与芯片流程的每个单位都用导引作用。

也就是说,比如,2025年,我们画个大饼要搞1nm,那么,这个时候所需要光刻设备厂家,刻蚀设备厂家,材料厂家,研究机构等等,都要瞄准这个目标来做。

这个路线图,主要是“为大学、财团和行业研究人员提供未来的主要参考,以刺激各个技术领域的创新”。

也就是说,要给芯片制造从业者画一个大饼。

多年来,国际半导体技术路线图(ITRS)发布了该行业的总体路线图。这些路线图延续了15年,为半导体市场设定了总体目标。

ITRS就是画大饼的人!

那如何画这个大饼(roadmap)?

当然是摩尔定律,也就是本文第一部分介绍的那样。

摩尔定律这个就是这么粗暴。

一直从几百nm,干到5nm或者3nm。

关键是,数学可以这么算,物理能这么搞吗?

这么搞,是不是有点太草率了。

4:营销手段:宝马5系和5nm

不久之后, ITRS(国际半导体技术路线图)这个组织也明白了,这么搞是不行的。

不能把栅极长度(gate length)或半节距(half-pitch)与节点大小联系起来的原因是:

因此这些尺寸要么停止缩放,要么缩放得更慢了。

粗暴的乘以0.7还能指望晶体管能工作。

这种晶体管,工业界制造不出来。

于是,在2010年,ITRS将每个节点上的技术,统称为“等效缩放”。

也就是说,不用实际对应上,你觉得差不过就行。

也就是说,7nm,5nm,早已不是原来指的栅极长度(gate length),或者(half-pitch)半节距。

这种改变,反应了芯片制造业的现状:

台积电的Philip Wong在Hot Chips 31主旨演讲中说:“它过去是技术节点,节点编号,意味着一些东西,晶圆上的一些功能。”。

但是:“今天,这些数字只是数字。它们就像汽车模型——就像宝马5系或马自达6。数字是什么并不重要,它只是下一项技术的目的地,它的名称。因此,我们不要把节点的名称与技术实际提供的相混淆。”

画重点:不要把节点的名称和技术实际相混淆

5nm,7nm这些和宝马5,马自达6没有什么区别。

这些只是营销的手段而已。

不是大众要把这个名字相混淆。

而是这些芯片制造厂商,搞这些营销词汇,不就是想混淆工艺制程的节点和晶体管的实际尺寸吗?

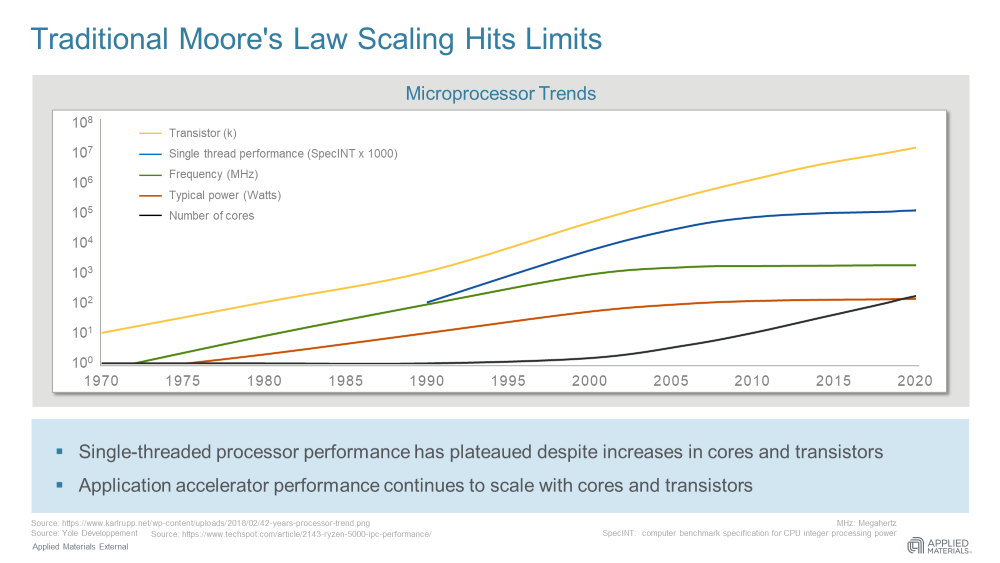

虽然摩尔定律这艘大船进入浅水区,快搁浅了。

让我们一起晃动这艘大船,假装摩尔定律启示的那样继续前进,

所以英特尔就有人提出来了。

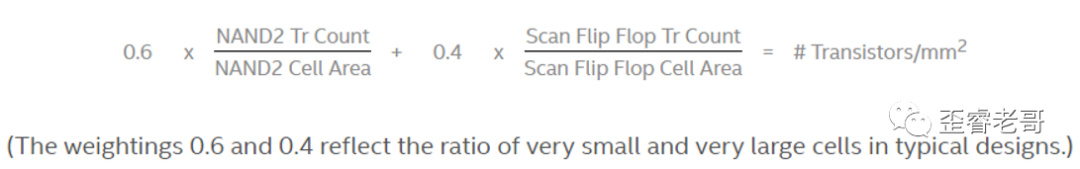

不要扯,5nm,7nm了,直接比拼一下单位面积晶体管的数量好了。

下面就是这个公式:

英特尔的芯片制造专家Mark Bohr提出来的, 它认为每个芯片制造商在提及工艺节点时,都应披露其逻辑晶体管密度,单位为MTr/mm2(每平方毫米数百万个晶体管)

这个也就是解释了,为什么英特尔的10nm和台积电的7nm,虽然看起来是两代,但是二者的晶体管密度基本一样。

但是,这个公式太复杂了。

怎么可能有7nm,5nm对大众的宣传效果好。

但是,实话实说,英特尔本身自己在命名方案里面,也没有真正遵循栅极长度(gate length)的模型。

从下表来看,随着工艺的进步,玩家越来越少了。

高端玩家就剩下了台积电和三星,还有一直要追赶的英特尔。

明年,三星和台积电的3nm都号称要量产。

但是这一次,我们应该知道,这个只是一代工艺代号而已,和3nm本身没有太大的关系了。

从7nm,5nm,到3nm。

摩尔定律不死。只是,已经快“植物人”了。

责任编辑:haq

-

芯片

+关注

关注

446文章

47753浏览量

409048 -

集成电路

+关注

关注

5320文章

10722浏览量

353308 -

电路

+关注

关注

170文章

5480浏览量

169503

原文标题:芯片工艺的5nm和7nm是怎么来的?揭开芯片工艺和摩尔定律背后的“秘密”

文章出处:【微信号:电子工程世界,微信公众号:电子工程世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

英特尔CEO基辛格:摩尔定律放缓,仍能制造万亿晶体

英特尔CEO基辛格:摩尔定律仍具生命力,且仍在推动创新

后摩尔定律时代,Chiplet落地进展和重点企业布局

摩尔定律不会死去!这项技术将成为摩尔定律的拐点

超越摩尔定律,下一代芯片如何创新?

半导体行业产生深远影响的定律:摩尔定律!

什么是摩尔定律?

芯片工艺摩尔定律揭示的现实

芯片工艺摩尔定律揭示的现实

评论