答:对原理图文件进行DRC检测以后,按照设置的DRC检测的选项,会在原理图中留下DRC的标记,对于分页的原理图来说,每一页每一页的去查看DRC的标记,比较繁琐,这里可以运用Browse功能,查看所有的DRC,操作方法如下:

第一步,选中原理图的根目录,执行菜单Edit→Browse功能,然后选择DRC Marks,进行DRC标记的查看。

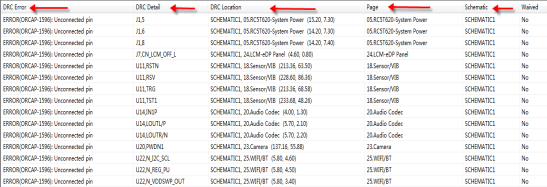

第二步,执行命令以后,如图3-67所示,DRC ERROE显示的是错误的类型说明,DRC Detail显示的是该错误所属器件与位号,DRC Location显示的是DRC的位置,Page显示的DRC所在的页面。

图3-67 DRC Marks显示示意图

责任编辑:haq

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

检测

+关注

关注

5文章

4062浏览量

90721 -

DRC

+关注

关注

2文章

142浏览量

35755

原文标题:【知识分享】34.orcad怎么去浏览DRC检测过后的全部DRC错误呢?

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

带SmartGain™AGC/DRC的3W单声道D类音频放大器TPA2018D1数据表

电子发烧友网站提供《带SmartGain™AGC/DRC的3W单声道D类音频放大器TPA2018D1数据表.pdf》资料免费下载

发表于 03-20 09:55

•0次下载

带快速增益斜坡SmartGain™AGC/DRC的3W单声道D类音频放大器TPA2028D1数据表

电子发烧友网站提供《带快速增益斜坡SmartGain™AGC/DRC的3W单声道D类音频放大器TPA2028D1数据表.pdf》资料免费下载

发表于 03-20 09:43

•0次下载

芯片后端设计的DRC是什么?

DRC的全称为design rule check,也就是设计规则检查。广义上DRC会包含很多分类,只要是设计规则广义上都可以成为DRC。

是否可以在CC中使用DRD AutoFix帮助快速DRC收敛呢?

在版图设计中,常常需要花费很多的时间来clear DRC Violation,是否可以在版图设计过程中来规避一些DRC 问题呢?比如最常见的space,area,enc 等。

怎样用ADAU1761设计DRC的压缩/扩展?

请问怎样用ADAU1761设计DRC的压缩/扩展。我在SigmaStudio 4.5的模块中只找到RMS。如果用ADAU1761设计DRC要怎样做

发表于 11-28 06:41

DRC规则是指什么?怎样使用DRC规则减少PCB改版次数呢?

DRC规则是工程师根据审生产制造标准设定的一些约束,PCB设计工程师都需要遵守这些规则,这样可以确保设计出来的产品功能正常、可靠、并且可以到达量产生产的标准。

Calibre DRC报告自动做修复的教程分享

某些DRC在Innovus里面检查可能没有问题,但是到了Calibre/ICV检查可能发现有DRC问题。

DRC分析和修复经验分享

在DRC的修复过程中,我们可以先分析并修复PR工具里面的DRC,等DRC的数目比较少了之后,我们就可以把PV工具里面signoff DRC的结果load到PR工具里面去分析并做自动或者

编写PCB设计规则检查器技巧

由于DRC必须遍历 PCB设计整个电路图,包括每个符号、每个引脚、每个网路、每种属性,如有必要还能创建数目不限“附属”文件。如4.0节所述,DRC可以标示出任何违反设计规则细微偏差。

发表于 10-13 14:58

•221次阅读

基于CHS软件的线束设计开发流程

CHS软件具有白查功能,所有的器件和电线符号标示均是唯一的,当输入一个重复的名称时会自动提示命名错误。DRC设计规则检查使得在功能图设计中,没有连接到设备端、冗余电线、设备命名不规范、共用管脚号冲突等不容易查出的错误

发表于 06-02 11:35

•1609次阅读

orcad怎么去浏览DRC检测过后的全部DRC错误

orcad怎么去浏览DRC检测过后的全部DRC错误

评论