混合信号建模语言Verilog-AMS很多人做模拟电路的朋友,都希望有一款“模拟FPGA”,希望有一个“模拟的Verilog”,但现实是没有“模拟的Verilog”只有混合信号建模语言-Verilog-AMS,今天就简单介绍一下-Verilog-AMS。

为了便于物理系统的建模,人们在Verilog-2005的基础上,添加了一些新的关键字和语法结构,由此诞生了Verilog-AMS标准。所以Verilog-AMS是Verilog-2005的一个超集。换言之,Verilog-2005又是Verilog-AMS的子集。这里还有一个Verilog-A,具体三者关系如下:

该标准定义了标准的Verilog仿真器和模拟解算器之间的互动。而且,Verilog-AMS语言从诞生开始,就是为常用的物理系统的建模,而不仅是为电路网络的建模而创造的。

Verilog-AMS基础Verilog-AMS引入了一些重要的新概念。其中最重要的新概念可以总结为两个关键字:discipline和nature。在“标准”的Verilog中net(线网)类型表示的只是具体的物理连接线路。在显示仿真的结果时,可以观察到在一段时间里这条线路的状态变化。因此,net有两个含义:具体的物理连接和时间历史。电路节点表示两个或更多个元件连接在一起的那个点。然而,不能讨论该节点本身的行为,除非指定讨论的对象是该节点的电压或流过该节点的电流,以及其他方面。

为了对具体的物理连接和行为进行区别,Verilog-AMS引入了新的关键字。在模型中,节点上的电压或者电流用关键字nature声明。在举例说明之前,必须先解释一下nature和节点之间是怎样相互关联的。

节点和网络类型有着密切的关联。例如,电路节点归属于电路网络,磁节点归属于磁网络。各种网络的行为都可以用关键字nature(性质)来描述。例如,电路网络的行为可以用电压和电流来描述;

而磁网络的行为可以用磁动势和磁通量来描述。每一类型的网络都有自身的一对性质。这一对性质可以描述为flow(流性质)和potential(势性质)。例如,在电路网络中,电流通过元件从网络的一个节点流到另一个节点;

此刻,也可以测量元件两端的电动势。每一类型的网络都具有一对这样的流性质和势性质。(请注意,也可以按照与传统思路完全相反的概念来定义这个电网络,即在该电网络中,定义电流具有势性质,电压具有流性质。

从数学角度来定义性质,无论传统的或相反的定义都是可接受的。然而,在电网络中,接受符合传统约定的性质定义比较容易。而在其他类型的网络中,确定究竟哪个物理量为势性质,哪个物理量为流性质可能不那么清楚。)

在某特定网络节点性质的定义中,事实上定义了该网络的流性质和势性质。因此,只声明某个线网是一个特定的Verilog类型的线网是不够的,所以必须添加一种新结构,即discipline(规则)来描述该线网。规则由两个部分组成:势性质和流性质。此外,domain(域)可以声明为连续的continuous)或者离散的discrete)。在默认情况下,规则是连续的。

电路规则可以用如下语句声明:

disciplineelectrical

potentialVoltage;

flowCurrent;

enddiscipline

与别处-样,代码段中的关键字用粗字体表示。代码段中的Voltage(电压)和Current(电流)是什么?我们知道potential(势)和flow(流)这两部分都是natures(性质),所以Voltage和Current一定是natures。

natureVoltage

units="V";

access=V;

idt_nature=Flux;

abstol=le-6;

endnature

natureCurrent

units="A";

accessI

idt_nature=Charge;

abstol=le-12;

endnature

这两个性质声明块的内容都由四条语句组成,但并非每条语句都是必需的。第1条语句units列出了用于表示该性质的符号。Verilog-AMS语言不执行维度分析,所以这条语句只是提供可读性而已。第2条语句中的access给出了访问功能。由于第2条语句中存在access,所以在代码段中,V(nodel)表示引用节点1的电压。第3条语句中的idt_nature表示等号后的物理量具有时间积分的性质。也可以用ddt_nature来表示等号后的物理量具有时间导数的性质。但在这种场合,Flux(通量)和Charge(电荷)应该在别处声明。最后一条语句中的关键字abstol表示允许的绝对误差,这条语句定义了性质块声明的变量在计算过程中的精确度。

在下面的例子中,假设在文件disciplines.vams中包含一些电规则的定义。每个模块的开头都包括该规则定义文件。现在就可以用该文件中定义的电规则来定义一个或者多个节点。

“electrical nodel,node2;

”

我们可以用与定义线网或端口完全相同的方法在模块中定义节点。在端口声明时,必须声明端口的方向为inout(输入/输岀双向端口)类型。例如,下面的代码段声明了一个电阻模块:

'include"disciplines.vams";

moduleresistor(nodel,node2);

inoutnodel,node2;

electricalnodel,node2;

parameterrealR=1;

写到这里,只是创建了物理节点。可以用I(nodel,node2)表示在这两个节点之间流动的电流;也可以声明一个或多个支路。两个节点之间的支路可以用下面的语句声明:

“branch (nodel,node2) res;

”

所以,现在还可以用I(res)来表示流经电阻的电流。

每个流经物理量的计算基准点就是所谓的参考节点。在电路网络中,该参考节点通常称为地线或者接地点。在Verilog-AMS模型中,通常用下面的语句来表示接地点:公众号:OpenFPGA

“ground gnd;

”

作用语句

作用语句(contrihution statement)用于定义模拟模型的线路方程。在作用语句中,使用符号“<+”来表示表达式如何作用于某线路方程组。请注意,“<+”不是传统意义上的赋值操作符,而是对同一个流或者势的多个作用的总和。

因此,作用语句是由模拟仿真器求解的联立方程。作用语句必须放在模拟过程块之中。为了说明作用语句,我们编写了一个电阻器的完整模型:

'include"disciplines.vams"

moduleresistor(nodel,node2);

inoutnodel,node2;

electricalnodel,node2;

parameterrealR=1;

branch(nodel,node2)res;

analogbegin

I(res)<+ V(res)/R ;

end

endmodule

可以用类似的方法为其他元件建模。例如,下面的代码段是一个电容器的Verilog-AMS模型:

'include"disciplines.vams"

modulecapacitor(nodel,node2);

inoutnodel,node2;

electricalnodel,node2;

parameterrealC=1;

branch(nodel,node2)cap;

analogbegin

I(cap)<+ C*ddt(V(cap));

end

endmodule

上面程序中的ddt是一个求导函数。其功能是求出电容两端电压的变化率,即求电压的微分。而下面语句中的idt是一个积分函数,其功能是计算其后面变量(流经电容的电流)的积分。由于作用语句是代数表达式而不是赋值操作,所以可以用以下方程来表示电容电压:

“V(cap) < + idt ( I(cap))/C;

”

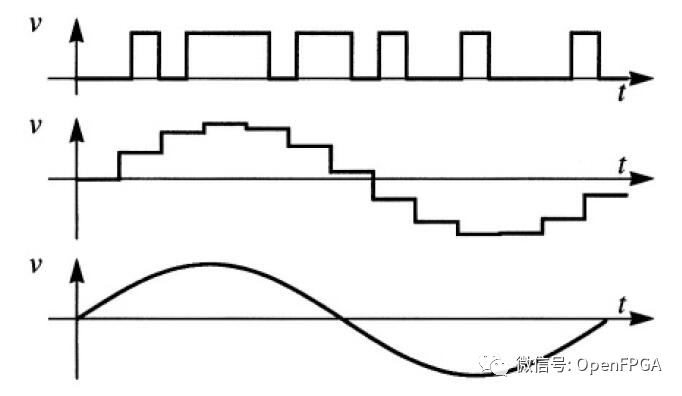

在结束这些基本模型的讨论之前,让我们先考虑一个产生正弦波形的纯电压源,以后需要把这个电压源模型作为基础元件来描述DAC。

'include"constants.vams"

'include"disciplines.vams"

modulevsin(a,b);

inouta,b;

electricala,b;

branch(a,b)vs;

parameterrealvo=1;

parameterrealva=1;

parameterrealfreq=1;

analogbegin

V(vs)<+ vo + va * sin('M_TWO_PI*freq*$abstime);

end

endmodule

在文件constants.vams中,定义了许多有用的参数,其中包括M_TWO_PI(即2倍的圆周率—2π),$time,但是$abstime返回的是一个实型数。

混合信号建模

Verilog-AMS是一种混合信号建模语言,所以我们可以把模拟结构和数字结构写在同一个模块中。下面编写一个简单比较器的模型。该比较器可以对两个模拟电压信号进行比较,把比较结果转换为1比特的数字信号。当第1个输人信号比第2个大时,比较器输出逻辑1,否则输出逻辑0。该比较器的Verilog-AMS模型如下:

"include"disciplines.vams"

modulecomp(Aplus,Aminus,Dout);

inoutAplus,Aminus;

electricalAplus,Aminus;

outputDout;

regDout;

initial

begin

Dout=l'bl;

forever

begin

@(cross(V(Aplus,Aminus),-1))Dout=1'bO;

@(cross(V(Aplus,Aminus),+1))Dout=l'bl;

end

end

endmodule

这个模块有三个端口,其中两个是电路节点,另一个是数字输出端口。在模块体中,必须能检测到其中一个模拟电压大于或小于另一个模拟电压的时刻,根据比较的结果,对开关进行相应的操作,输出逻辑1或者0。这个比较器当然可以用一个简单的比较操作符这个模块有三个端口,其中两个是电路节点,另一个是数字输出端口。在模块体中,必须能检测到其中一个模拟电压大于或小于另一个模拟电压的时刻,根据比较的结果,对开关进行相应的操作,输出逻辑1或者0。这个比较器当然可以用一个简单的比较操作符来表示,但是在这里用cross函数来表示更好一些。当表达式越过0时,立即产生一个数字信号事件。在cross函数中的第2个参数是用来表示方向的,只有从一个方向越过0才能触发事件,+1表示正方向,-1表示负方向,而0或不指定参数,则表示有两个方向。然而cross函数并不触发初始条件事件。因此,编写一个初始化块,先给Dout赋一个初始值,然后检测输入的模拟电压的上升或下降是否越过0,一旦越过,立即触发事件,根据越过0的方向,切换Dout的逻辑值为1或0。公众号:OpenFPGA

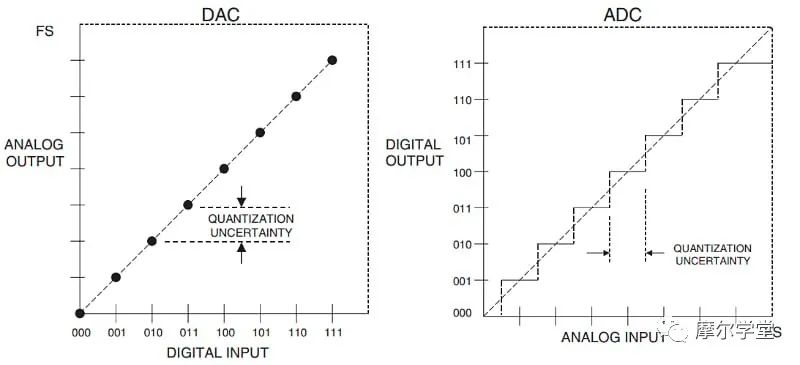

Verilog-AMS仿真器

ADC、DAC和PLL的混合信号模型是否可以完全用标准的Venlog语言来建模,可能还有争论。实际上,在这些模型中只有极少量的行为必须用模拟解算器才行。Verilog-AMS真正强大的功能在于允许在Verilog数字模型仿真的同时,进行模拟电路的仿真,而传统的模拟电路仿真必须使用SPICE软件才行。我们可以把SPICE的网表添加到Verilog-AMS的仿真库中。

目前,有许多仿真器支持多种语言的仿真。因此,组成系统模型的子模块可以用Verilog、SystemVerilog、Verilog-AMS、SPICE、VHDL、VHDL-AMS和SystemC等多种语言来编写。

总结

数字电路必须与真实的模拟世界接口,这个接口及与模拟元件的相互作用的建模总是十分困难的。Verilog-AMS扩展了Verilog功能,允许模拟和混合信号建模。典型的转换器包括阶梯型DAC、快闪型ADC和PLL。所有这些元件都可以用Verilog-AMS建模和仿真。目前从这些无件的行为模型还不能自动综合出元件的物理构造,由于rilog-AMS仿真器还是-个相对较新的事物,所以个別Venlog-AMS语法得不到Verilog-AMS仿真器的支持是很冇吋能的。这些仿真器确实提供了SPICE模型与Verilog-AMS之间进行接口的手段,从而允许完整系统的建模。

目前,国内对Verilog-A/Verilog-AMS研究很少,希望借此文章让更多人了解Verilog-A/Verilog-AMS,在未来可能有更大的用途。

-

dac

+关注

关注

43文章

1971浏览量

189444 -

Verilog

+关注

关注

28文章

1324浏览量

109285 -

AMS

+关注

关注

10文章

204浏览量

86637

原文标题:数模混合信号建模语言Verilog-AMS

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

科普一下CAN总线的基础知识

简单介绍一下-Verilog-AMS的基础知识

简单介绍一下-Verilog-AMS的基础知识

评论