小技巧分享:

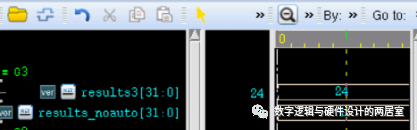

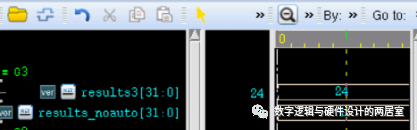

verilog下取对数其实可用$clog2这个系统函数,和自己找代码里面写入function是同样的效果,但是方便的多。这是verilog 2005就开始支持的标准,所以vivado也是支持的,我试了2017.4及以后的版本都可以支持,放心用。

***友情提示:所有支持verilog2005标准的编译器都可以用这个函数,所以使用之前确定编译器是否支持这个标准,还有考虑好后期可移植性的影响

这个是可编译的函数大家可以把她当做宏定义函数一样看待。这操作好玩吗?好玩就赶紧升级编译器吧,新标准总是有很多的改进,如果想了解一些更有意思的东西欢迎关注我,我是最骚的FPGAer。

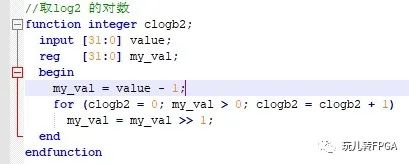

这里附上常用的自定义log2函数,供大家白嫖。图片不清晰尽请担待。

编辑:jq

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1601文章

21296浏览量

593081 -

函数

+关注

关注

3文章

3863浏览量

61303 -

代码

+关注

关注

30文章

4554浏览量

66726 -

编译

+关注

关注

0文章

613浏览量

32371

原文标题:verilog2005的骚操作之对数函数

文章出处:【微信号:HaveFunFPGA,微信公众号:玩儿转FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

verilog调用模块端口对应方式

Verilog中的模块端口对应方式,并提供示例代码和详细解释,以帮助读者更好地理解和应用。 首先,我们来了解一下Verilog中的模块和模块端口。一个Verilog模块被定义为包含一组声明和语句的代码块,类似于C语言中的

verilog中for循环是串行执行还是并行执行

在Verilog中,for循环是并行执行的。Verilog是一种硬件描述语言,用于描述和设计数字电路和系统。在硬件系统中,各个电路模块是同时运行的,并且可以并行执行多个操作。因此,在Veril

什么是函数式接口

、及其所使用的一些和函数式接口相关的知识点进行一个全面的学习。函数式接口所涉及的知识点包含:java.util.function包,@FunctoinInterface注解,Lambda表达式,双冒号操作符。同时,我们还将对

Verilog中的数据位操作技巧

FPGA相比MCU而言,在数据位操作上有很明显的优势。FPGA支持任意位拼接以及数据截取操作。本篇主要是总结和分享一些对数据位操作的实用语法技巧。内容不多,其中最最最重要的内容是数据的

verilog移位操作和C语言的移位操作的异同点有哪些?

C语言的移位操作和Verilog语言的移位操作在某些方面具有相似之处,但也存在一些显著的不同点。下面我们将通过代码示例来阐述这两种语言的移位操作。

Linux Regmap 操作函数

Regmap 操作函数 1、Regmap 申请与初始化 regmap 支持多种物理总线,比如 I2C 和 SPI,我们需要根据所使用的接口来选择合适的 regmap 初始化函数。Linux 内核提供

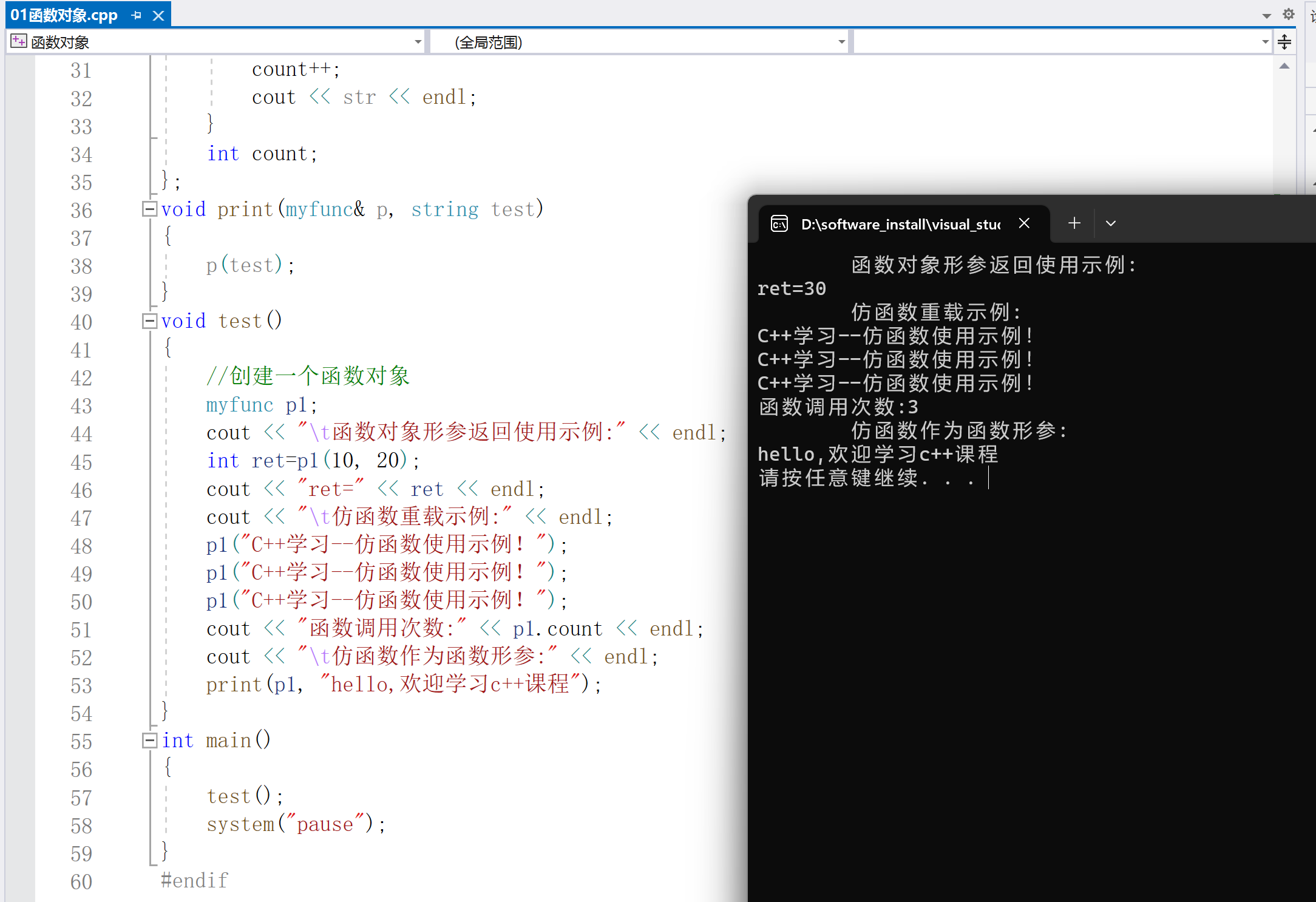

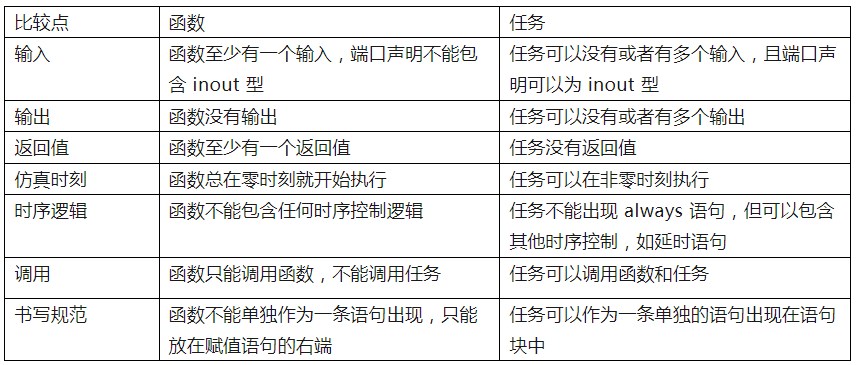

在Verilog中利用函数将重复性的行为级设计进行提取

在 Verilog 中,可以利用任务(关键字为 task)或函数(关键字为 function),将重复性的行为级设计进行提取,并在多个地方调用,来避免重复代码的多次编写,使代码更加的简洁、易懂。

谈谈Verilog/System Verilog和C的几种交互模式

PLI全称 Program Language Interface,程序员可以通过PLI在verilog中调用C函数,这种访问是双向的。

用Verilog函数实现一个数据大小端转换的功能

在 Verilog 中,可以利用任务(关键字为 task)或函数(关键字为 function),将重复性的行为级设计进行提取,并在多个地方调用,来避免重复代码的多次编写,使代码更加的简洁、易懂。

谈谈system Verilog 和C的交互

PLI全称 Program Language Interface,程序员可以通过PLI在verilog中调用C函数,这种访问是双向的。这些用户定义的系统任务和函数的名称必须以美元符号"$" 开头。大家用得比较多的PLI

发表于 05-31 09:59

•388次阅读

剖析verilog2005的骚操作之对数函数

剖析verilog2005的骚操作之对数函数

评论