大侠好,阿Q来也,今天是第二次和各位见面,请各位大侠多多关照。今天给各位大侠带来一篇项目开发经验分享“基于JESD204B的LMK04821芯片项目开发”第二篇,这是本人实打实的项目开发经验,希望可以给有需要的大侠提供一些参考学习作用。

以后机会多多,慢慢分享一些项目开发以及学习方面的内容,欢迎各位大侠一起切磋交流。

204B实战应用-LMK04821代码详解(二)

一、 SPI协议

通过阅读LMK04821数据手册,我们可以从中知道,可以通过SPI协议对LMK04821进行寄存器的配置工作,进而实现我们设计所需要的功能。

SPI协议部分,咱们可以用3线,或者4线,在本次设计中,使用3线。关于SPI的时序部分,这儿就不再赘述,手册里面都有详细的描述。

二、 SPI寄存器配置模块设计

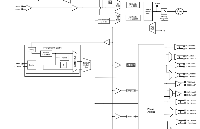

图2

如图2所示,就是配置LMK04821存器的单元,信号定义如下:

1、cfg_clk:系统时钟;

2、cfg_rst:系统复位;

3、通过VIO控制的信号,这组信号存在的目的在于方便检测自己配置寄存器的正确性。

vio_cfg_en:配置寄存器使能信号;

vio_cfg_wr:配置寄存器读写使能,0写1读;

vio_cfg_addr:配置的寄存器地址;

vio_cfg_wdata:寄存器中配置的值;

addr_118_data:预留信号,模块中没有用;

我们在配置LMK04821寄存器时,要验证配置寄存器操作是否正确,就要有写有读,在对应的寄存器内写入对应的数值,然后进行读操作,观察正确性。本次设计是在vivado环境下进行设计,通过添加VIO的IP核,来控制读写操作。同时,添加ILA配合VIO来进行读写数据操作的观测。别的开发环境下思路一样。

该组信号仅在回读寄存器时使用,目的是为了验证寄存器读写正确性。

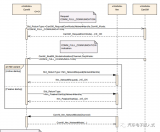

图3

4、lmk_rst:LMK04821复位信号,用于复位LMK04821,直接和LMK04821芯片相连;

5、3线制SPI信号:

lmk_spi_csn:片选;

lmk_spi_sdio:数据;

lmk_spi_clk:时钟;

6、可编程管教:主要和LMK04821内部的PLL相关,本次设计中默认为0;

lmk_clk_sel0 :sel0;

lmk_clk_sel1 :sel1;

三、 SPI数据buffer定义

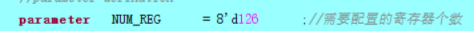

在本次设计中,SPI配置数据buffer,data_reg为24bit,r_w占1bit,箭头1所指包含W1、W2以及地址位占13bit,具体见SPI时序图;箭头2所指数据位8bit。

根据图5我们可以知道,要配置LMK04821我们需要配置126个寄存器,这126个寄存器来源参见第一章实战记录。

其中,126个寄存器包含必须要配的寄存器、一些无关紧要的寄存器、以及功能实现所需要的寄存器等,有些寄存器需要配置多次。

四、 SPI时序实现

设计中,我们需要按照顺序配置126个寄存器,也就是说SPI要执行126次。因此,在代码实现过程中,注意寄存器配置的顺序,并且保证每个寄存器都准确无误的配置完成,才能进行下一个寄存器的配置。如果在设计中,要求LMK004821实现不同的功能,当配置的寄存器个数不一致时,在v文件中更改图6所示的参数即可。

图6

如下:是LMK04821配置的模块,读者可以作为参考。

代码区(参考代码):

//###########################################################################//// Copyright (C) 2017, JSZX, Co. Ltd. All Rights Reserved.//###########################################################################////-- Project Name :

//-- File Name : lmk04821_spi//-- Description ://###########################################################################////---------------------------Modification History----------------------------////-- Date By Ver Comment//-- 12/04/2017 hhh 1.0 Create new//===================================================================//-- End Revision//===================================================================`

timescale 1ns / 1ps

module lmk04821_spi( input cfg_clk , //《=10MHz input cfg_rst , input vio_cfg_en , input vio_cfg_wr ,//0,write;1,read; input [12:0] vio_cfg_addr , input [07:0] vio_cfg_wdata , input [07:0] addr_118_data ,

input r_w , input lmk_cfgen , output lmk_rst , output lmk_spi_csn , inout tri lmk_spi_sdio , output lmk_spi_clk , output lmk_clk_sel0 , output lmk_clk_sel1 , output reg regdatareadvalid , output reg [7:0] regdataread , output reg lmk_cfgdone = 1‘b0 );

//parameter defination parameter NUM_REG = 8’d126 ;//需要配置的寄存器个数 parameter CFG_DONE_DLY = 32‘hF4240 ;//100ms@10Mhz; //====================================================================// //----------------------internal signals------------------------------// //====================================================================// reg [00:0] lmk_cfgen_d0 ; reg [00:0] lmk_cfgen_d1 ;

reg [00:0] lmk_cfgen_d2 ; reg [00:0] vio_cfg_en_d0 ; reg [00:0] vio_cfg_en_d1 ;

reg [00:0] vio_cfg_en_d2 ; reg [07:0] cnt_clk ;// 每个寄存器需要的时钟数计数器 reg [07:0] cnt_reg ;// 需要配置的寄存器计数器,最多255个! reg [23:0] data_reg ; reg [00:0] load_p ; reg [00:0] load_p_d0 ; reg [35:0] mid_data_o ;

reg [35:0] mid_csn_o ; reg [00:0] spi_sdo ; reg [00:0] spi_cs_n ; wire[00:0] spi_sdi ; reg [05:0] sdo_cnt ;// //====================================================================//// //-----------------------------ila debug------------------------------//// //====================================================================

//// //ila_spi// ila_spi ila_spi(// .clk ( cfg_clk ),//// .probe0 ( cnt_clk ),//8// .probe1 ( cnt_reg ),//8// .probe2 ( data_reg ),//24// .probe3 ( load_p ),//1// .probe4 ( sdo_cnt ),//6// .probe5 ( spi_cs_n ),//1// .probe6 ( spi_sdi ),//1// .probe7 ( spi_sdo ),//1// .probe8 ( lmk_cfgen_d1 ) //1// ); //====================================================================// //--------------------------main process------------------------------// //====================================================================//

//lmk_clk_sel assign lmk_clk_sel0= 1’b0 ; assign lmk_clk_sel1= 1‘b0 ; //spi signals; assign lmk_rst = cfg_rst ; assign lmk_spi_clk = (spi_cs_n) ? 1’b0 : ~cfg_clk ;

assign lmk_spi_csn = spi_cs_n ; assign spi_sdi = lmk_spi_sdio; assign lmk_spi_sdio= (data_reg[23]==1‘b1 && sdo_cnt》6’h18)? 1‘bz : spi_sdo ;

//lmk_cfgen_d0/lmk_cfgen_d1/lmk_cfgen_d2/load_p_d0 always @(posedge cfg_clk or posedge cfg_rst) begin if(cfg_rst==1’b1) begin lmk_cfgen_d0 《= 1‘b0 ; lmk_cfgen_d1 《= 1’b0 ; lmk_cfgen_d2 《= 1‘b0 ; load_p_d0 《= 1’b0 ;

vio_cfg_en_d0 《= 1‘b0 ; vio_cfg_en_d1 《= 1’b0 ; vio_cfg_en_d2 《= 1‘b0 ; end else begin lmk_cfgen_d0 《= lmk_cfgen ;

lmk_cfgen_d1 《= lmk_cfgen_d0 ; lmk_cfgen_d2 《= lmk_cfgen_d1 ; load_p_d0 《= load_p ; vio_cfg_en_d0 《= vio_cfg_en ; vio_cfg_en_d1 《= vio_cfg_en_d0 ; vio_cfg_en_d2 《= vio_cfg_en_d1 ;

end end //load_p/cnt_reg/cnt_clk always @(posedge cfg_clk or posedge cfg_rst) begin if(cfg_rst==1’b1) begin cnt_reg 《= 8‘d0 ; cnt_clk 《= 8’d36 ; load_p 《= 1‘b0 ; end else begin if(lmk_cfgen_d1==1’b1 && lmk_cfgen_d2==1‘b0) begin cnt_clk 《= 8’d0 ;

cnt_reg 《= 8‘d0 ; load_p 《= 1’b0 ;

end else if((cnt_clk==8‘d36)&&(cnt_reg《NUM_REG)) begin cnt_clk 《= 8’d0 ; cnt_reg 《= cnt_reg + 8‘h1 ; load_p 《= 1’b1 ; end else begin load_p 《= 1‘b0 ; if(cnt_clk==8’d36)//cnt_reg==NUM_REG begin cnt_clk 《= 8‘d0 ; cnt_reg 《= cnt_reg ;

end else begin cnt_clk 《= cnt_clk + 8’h1 ; cnt_reg 《= cnt_reg ;

end end end end //data_reg:VCO0,1930~2075;VCO1,2920~3080; always @(posedge cfg_clk or posedge cfg_rst) begin if(cfg_rst==1‘b1) begin data_reg 《= 24’h80_0000; end else begin case(cnt_reg)//VCO_2Ghz; // Serial Port Configuration 8‘d1 : data_reg 《= {r_w,23’h0000_80} ;//soft reset 8‘d2 : data_reg 《= {r_w,23’h0000_00} ;//

8‘d3 : data_reg 《= {r_w,23’h0100_04} ;

//500Mhz;DCLKout0: input and output drive level;device clock out divider values 8‘d4 : data_reg 《= {r_w,23’h0101_55} ;//controls the digital delay high and low count values for the device clock outputs 8‘d5 : data_reg 《= {r_w,23’h0103_00} ;

//registers control the analog delay properties for the device clocks 8‘d6 : data_reg 《= {r_w,23’h0104_22} ;//set the half step for the device clock, the SYSREF output MUX, the SYSREF clock digital delay,and half step 8‘d7 : data_reg 《= {r_w,23’h0105_00} ;

//set the analog delay parameters for the SYSREF outputs 8‘d8 : data_reg 《= {r_w,23’h0106_70} ;

//controls the power down functions for the digital delay, glitchless half step 8‘d9 : data_reg 《= {r_w,23’h0107_15} ;//configure the output polarity, and formatLVDS;15:LVPECL16; 8‘d10 : data_reg 《= {r_w,23’h0108_10} ;//125Mhz;DCLKout2;V7_IO_CLK2; 8‘d11 : data_reg 《= {r_w,23’h0109_55} ; 8‘d12 : data_reg 《= {r_w,23’h010B_00} ;

8‘d13 : data_reg 《= {r_w,23’h010C_22} ;//bit[5]:SDCLKoutY_MUX;0, Device clock output; 8‘d14 : data_reg 《= {r_w,23’h010D_00} ; 8‘d15 : data_reg 《= {r_w,23’h010E_70} ;

//bit[3]:0,enable;bit[4]:powerdown; 8‘d16 : data_reg 《= {r_w,23’h010F_11} ;//11:LVDS;15:LVPECL16 8‘d17 : data_reg 《= {r_w,23’h0110_10} ;//125Mhz;DCLKout4; 8‘d18 : data_reg 《= {r_w,23’h0111_55} ; 8‘d19 : data_reg 《= {r_w,23’h0113_00} ; 8‘d20 : data_reg 《= {r_w,23’h0114_22} ;

//bit[5]:SDCLKoutY_MUX;0, Device clock output; 8‘d21 : data_reg 《= {r_w,23’h0115_00} ;

8‘d22 : data_reg 《= {r_w,23’h0116_70} ;//bit[3]:0,enable;bit[4]:powerdown; 8‘d23 : data_reg 《= {r_w,23’h0117_11} ;//11:LVDS;15:LVPECL16 8‘d24 : data_reg 《= {r_w,23’h0118_04} ;//500Mhz;DCLKout6,FPGA;V7_IO_CLK0; 8‘d25 : data_reg 《= {r_w,23’h0119_55} ; 8‘d26 : data_reg 《= {r_w,23’h011B_00} ;

8‘d27 : data_reg 《= {r_w,23’h011C_22} ;//bit[5]:SDCLKoutY_MUX;0, Device clock output; 8‘d28 : data_reg 《= {r_w,23’h011D_00} ; 8‘d29 : data_reg 《= {r_w,23’h011E_70} ; 8‘d30 : data_reg 《= {r_w,23’h011F_11} ;//11:LVDS;15:LVPECL16 8‘d31 : data_reg 《= {r_w,23’h0120_10} ;//125Mhz;DCLKout8,FPGA MGT114 CLOCK; 8‘d32 : data_reg 《= {r_w,23’h0121_55} ; 8‘d33 : data_reg 《= {r_w,23’h0123_00} ;

8‘d34 : data_reg 《= {r_w,23’h0124_02} ;//bit[5]:SDCLKoutY_MUX;0, Device clock output; 8‘d35 : data_reg 《= {r_w,23’h0125_00} ;

8‘d36 : data_reg 《= {r_w,23’h0126_70} ; 8‘d37 : data_reg 《= {r_w,23’h0127_11} ;//11:LVDS;15:LVPECL16 8‘d38 : data_reg 《= {r_w,23’h0128_10} ;//125Mhz;DCLKout10,FPGA MGT116 CLOCK; 8‘d39 : data_reg 《= {r_w,23’h0129_55} ; 8‘d40 : data_reg 《= {r_w,23’h012B_00} ;

8‘d41 : data_reg 《= {r_w,23’h012C_02} ;//bit[5]:SDCLKoutY_MUX;0, Device clock output; 8‘d42 : data_reg 《= {r_w,23’h012D_00} ; 8‘d43 : data_reg 《= {r_w,23’h012E_70} ; 8‘d44 : data_reg 《= {r_w,23’h012F_11} ;//11:LVDS;15:LVPECL16 8‘d45 : data_reg 《= {r_w,23’h0130_04} ;//500Mhz;DCLKout12; 8‘d46 : data_reg 《= {r_w,23’h0131_55} ; 8‘d47 : data_reg 《= {r_w,23’h0133_00} ; 8‘d48 : data_reg 《= {r_w,23’h0134_22} ;

8‘d49 : data_reg 《= {r_w,23’h0135_00} ; 8‘d50 : data_reg 《= {r_w,23’h0136_70} ; 8‘d51 : data_reg 《= {r_w,23’h0137_15} ;//11:LVDS;15:LVPECL16

8‘d52 : data_reg 《= {r_w,23’h0138_00} ;//selects the clock distribution source, and OSCout parameters;VCO0; 8‘d53 : data_reg 《= {r_w,23’h0139_03} ;//sets the source for the SYSREF outputs 8‘d54 : data_reg 《= {r_w,23’h013A_00} ;

//SYSREF_DIV[12:8] DIV register 1;sysref 2000M/160=12.5Mhz; 8‘d55 : data_reg 《= {r_w,23’h013B_A0} ;//SYSREF_DIV[7:0] DIV register 0; 8‘d56 : data_reg 《= {r_w,23’h013C_08} ;//set the delay of the SYSREF digital delay value[12:8] 8‘d57 : data_reg 《= {r_w,23’h013D_00} ;

//set the delay of the SYSREF digital delay value[7:0] 8‘d58 : data_reg 《= {r_w,23’h013E_03} ;//sets the number of SYSREF pulses if SYSREF is not in continuous mode;

8‘d59 : data_reg 《= {r_w,23’h013F_04} ;//controls the feedback feature 8‘d60 : data_reg 《= {r_w,23’h0140_01} ;//13-OSCin PD; powerdown controls for OSCin and SYSREF functions;bit[0]:Powerdown SYSREF pulse generator; 8‘d61 : data_reg 《= {r_w,23’h0141_FF} ;//enables dynamic digital delay for enabled device clocks 8‘d62 : data_reg 《= {r_w,23’h0142_00} ;//sets the number of dynamic digital delay adjustments occur 8‘d63 : data_reg 《= {r_w,23’h0143_91} ;

//sets general SYNC parameters such as polarization, and mode 8‘d64 : data_reg 《= {r_w,23’h0144_00} ;//prevent a clock output from being synchronized or interrupted by a SYNC event or when outputting SYSREF 8‘d65 : data_reg 《= {r_w,23’h0145_7F} ;//Always program this register to value 127 8‘d66 : data_reg 《= {r_w,23’h0171_AA} ;// 8‘d67 : data_reg 《= {r_w,23’h0172_02} ;

// 8‘d68 : data_reg 《= {r_w,23’h0173_00} ;//bit[6]PLL2_PRE_PD; bit[5]PLL2_PD; 8‘d70 : data_reg 《= {r_w,23’h017C_15} ;//OPT_REG_1:21; 8‘d71 : data_reg 《= {r_w,23’h017D_33}

;//OPT_REG_2:51; 8‘d72 : data_reg 《= {r_w,23’h0182_00} ; 8‘d73 : data_reg 《= {r_w,23’h0183_00} ; 8‘d74 : data_reg 《= {r_w,23’h0184_00} ; 8‘d75 : data_reg 《= {r_w,23’h0185_00} ; 8‘d76 : data_reg 《= {r_w,23’h0188_00} ;

8‘d77 : data_reg 《= {r_w,23’h0146_38} ;//CLKin enable and type controls. 8‘d78 : data_reg 《= {r_w,23’h0147_02} ;//CLKin_SEL_MODE. pin select mode; 8‘d79 : data_reg 《= {r_w,23’h0148_02} ;

//CLKin_SEL0 controls 8‘d80 : data_reg 《= {r_w,23’h0149_42} ;//CLKin_SEL1 controls and register readback SDIO pin type 8‘d81 : data_reg 《= {r_w,23’h014A_02} ;//contains control of the RESET pin 8‘d82 : data_reg 《= {r_w,23’h014B_16} ;

//contains the holdover functions:start; 8‘d83 : data_reg 《= {r_w,23’h014C_00} ;// 8‘d84 : data_reg 《= {r_w,23’h014D_00} ;// 8‘d85 : data_reg 《= {r_w,23’h014E_C0} ;// 8

‘d86 : data_reg 《= {r_w,23’h014F_7F} ;// 8‘d87 : data_reg 《= {r_w,23’h0150_03} ;// 8

‘d88 : data_reg 《= {r_w,23’h0151_02} ;// 8‘d89 : data_reg 《= {r_w,23’h0152_00} ;//contains the holdover functions:end; 8‘d90 : data_reg 《= {r_w,23’h0153_00} ;//CLKin0_R[13:8] 8‘d91 : data_reg 《= {r_w,23’h0154_01} ;//CLKin0_R[7:0] 8‘d92

: data_reg 《= {r_w,23’h0155_00} ;//CLKin1_R[13:8] 8‘d93 : data_reg 《= {r_w,23’h0156_40} ;//CLKin1_R[7:0] 8‘d94 : data_reg 《= {r_w,23’h0157_00} ;//CLKin2_R[13:8] 8‘d95

: data_reg 《= {r_w,23’h0158_40} ;//CLKin2_R[7:0] 8‘d96 : data_reg 《= {r_w,23’h0159_00} ;//PLL1_N[13:8] 8‘d97 : data_reg 《= {r_w,23’h015A_01} ;//PLL1_N[7:0] 8‘d98 : data_reg 《= {r_w,23’h015B_D4} ;//PLL1 phase detector 8‘d99 : data_reg 《= {r_w,23’h015C_20} ;//PLL1_DLD_CNT[13:8] 8‘d100 : data_reg 《= {r_w,23’h015D_00} ;//PLL1_DLD_CNT[7:0] 8‘d101 : data_reg 《= {r_w,23’h015E_00} ;//contains the delay value for PLL1 N and R

delays. 8‘d102 : data_reg 《= {r_w,23’h015F_0B} ;//configures the PLL1 LD pin 8‘d103 : data_reg 《= {r_w,23’h0160_00} ;//PLL2_R[11:8] 8‘d104 : data_reg 《= {r_w,23’h0161_01} ;//PLL2_R[7:0] 8‘d105 : data_reg 《= {r_w,23’h0162_44} ;//sets other PLL2 functions:[7:5]:PLL2_P;[4:2]:OSCin_FREQ;[1]:PLL2_XTAL_EN;[0]:PLL2_REF_2X_EN; 8‘d106

: data_reg 《= {r_w,23’h0163_00} ;//PLL2_N_CAL[17:16] 8‘d107 : data_reg 《= {r_w,23’h0164_00} ;//PLL2_N_CAL[15:8] 8‘d108 : data_reg 《= {r_w,23’h0165_0C} ;//PLL2_N_CAL[7:0] 8‘d109 : data_reg 《= {r_w,23’h0166_00} ;//PLL2_N[17:16],MSB; 8‘d110 : data_reg 《= {r_w,23’h0167_00} ;//PLL2_N[15:8],---;

8‘d111 : data_reg 《= {r_w,23’h0168_0A} ;//PLL2_N[7:0],LSB; 8‘d112 : data_reg 《= {r_w,23’h0169_59} ;//controls the PLL2 phase detector 8

‘d113 : data_reg 《= {r_w,23’h016A_60} ;// 8‘d114 : data_reg 《= {r_w,23’h016B_00} ;// 8

‘d115 : data_reg 《= {r_w,23’h016C_00} ;// 8‘d116 : data_reg 《= {r_w,23’h016D_00} ;// 8

‘d117 : data_reg 《= {r_w,23’h016E_13} ;// 8‘d118 : data_reg 《= {r_w,23’h0143_90} ;// 8

‘d119 : data_reg 《= {r_w,23’h0139_00} ;// 8‘d120 : data_reg 《= {r_w,23’h0143_B0} ;// 8

‘d121 : data_reg 《= {r_w,23’h0143_90} ;// 8‘d122 : data_reg 《= {r_w,23’h0144_FF} ;// 8

‘d123 : data_reg 《= {r_w,23’h0143_10} ;// 8‘d124 : data_reg 《= {r_w,23’h0143_11} ;// 8‘d125 : data_reg 《= {r_w,23’h0139_03} ;// 8‘d126 : data_reg 《= {1’b1,23‘h0002_00} ;// default : data_reg 《= 24’h80_0000 ; endcase end end //spi_sdo/spi_cs_n/mid_data_o/mid_csn_o/mid_data_o/vio_cfg_cnt always @(posedge cfg_clk or posedge cfg_rst) begin if(cfg_rst==1‘b1) begin spi_sdo 《= 1’b0; spi_cs_n 《= 1‘b1; mid_data_o 《= 36’h0; mid_csn_o 《= 36‘hFFFFFFFFF; sdo_cnt 《= 6’b0 ; end else begin if

(load_p_d0==1‘b1) begin spi_sdo 《= 1’b0; mid_data_o 《= {data_reg[23:0],12‘hfff};//r_w:0 write;1 read; spi_cs_n 《= 1’b1; mid_csn_o 《= {24‘h0,12’hFFF}; sdo_cnt 《= 6‘h1 ; end else

if(vio_cfg_en_d1==1’b1 && vio_cfg_en_d2==1‘b0) begin spi_sdo 《= 1’b0; mid_data_o 《=

{vio_cfg_wr,2‘b00,vio_cfg_addr,vio_cfg_wdata,12’hfff};//r_w:0 write;1 read; spi_cs_n 《= 1

‘b1; mid_csn_o 《= {24’h0,12‘hFFF}; sdo_cnt 《= 6’h1 ; end else begin spi_sdo 《= mid_data_o[35]; mid_data_o 《= {mid_data_o[34:0],1‘b0}; spi_cs_n 《= mid_csn_o[35]; mid_csn_o 《=

{mid_csn_o[34:0],1’b1}; if(sdo_cnt《6‘h3f) begin sdo_cnt 《= sdo_cnt + 6’h1 ; end else

begin sdo_cnt 《= sdo_cnt ; end end end end //regdatareadvalid/regdataread always @(posedge cfg_clk or posedge cfg_rst) begin if(cfg_rst==1‘b1) begin regdatareadvalid 《= 1’b0 ; regdataread 《= 8‘b0 ;

end else begin if(spi_cs_n==1’b0) begin if(data_reg[23]==1‘b1) begin if(sdo_cnt》6’d18 && sdo_cnt《6‘d25)//2-17;18-25; begin regdatareadvalid 《= 1’b0 ; regdataread 《= {regdataread[6:0],spi_sdi}; end else if(sdo_cnt==6‘d25) begin regdatareadvalid 《= 1’b1 ; regdataread 《= {regdataread[6:0],spi_sdi};

end else begin regdatareadvalid 《= 1‘b0 ; regdataread 《= regdataread ; end end else begin regdatareadvalid 《= 1’b0 ; regdataread 《= regdataread ; end end else begin regdatareadvalid 《= 1‘b0 ; regdataread 《= regdataread ;

end end end //lmk_cfgdone always @(posedge cfg_clk or posedge cfg_rst) begin if(cfg_rst) begin lmk_cfgdone 《= 1’b0 ; end else begin if(cnt_reg》=NUM_REG) begin lmk_cfgdone 《= 1‘b1 ; end else begin lmk_cfgdone 《= 1’b0 ;

end end end //====================================================================// //------------------------------- end ------------------------------// //====================================================================//

endmodule

下一篇,将详细介绍jesd_204B IP核应用的相关知识,各位大侠,尽请关注。

责任编辑:haq

-

FPGA

+关注

关注

1600文章

21285浏览量

592883 -

SPI

+关注

关注

17文章

1610浏览量

89540 -

代码

+关注

关注

30文章

4553浏览量

66666

原文标题:FPGA项目开发:204B实战应用-LMK04821代码详解(二)

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

E4A5 易安卓和单片机keil串口通讯mini理疗仪项目代码

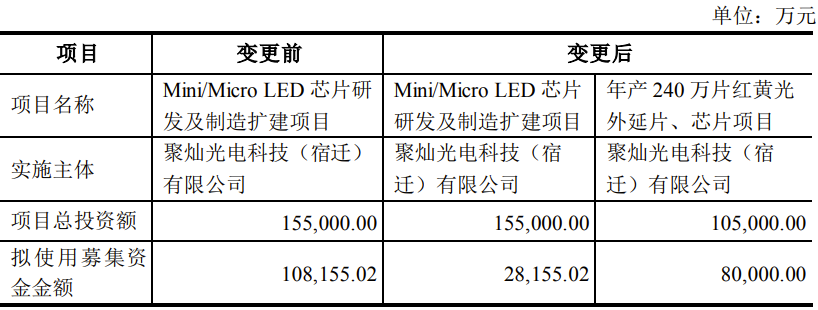

聚灿光电宣布扩建Mini/Micro LED芯片研发及制造项目

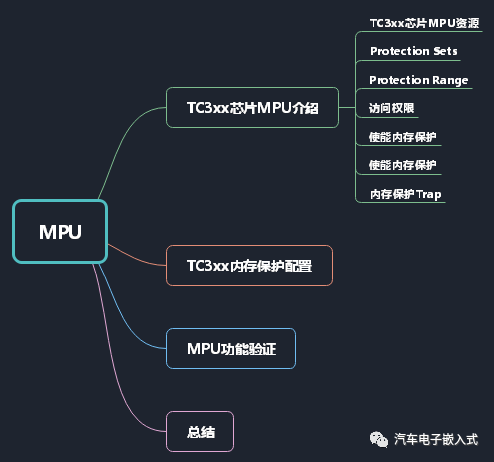

TC3xx芯片的MPU功能详解

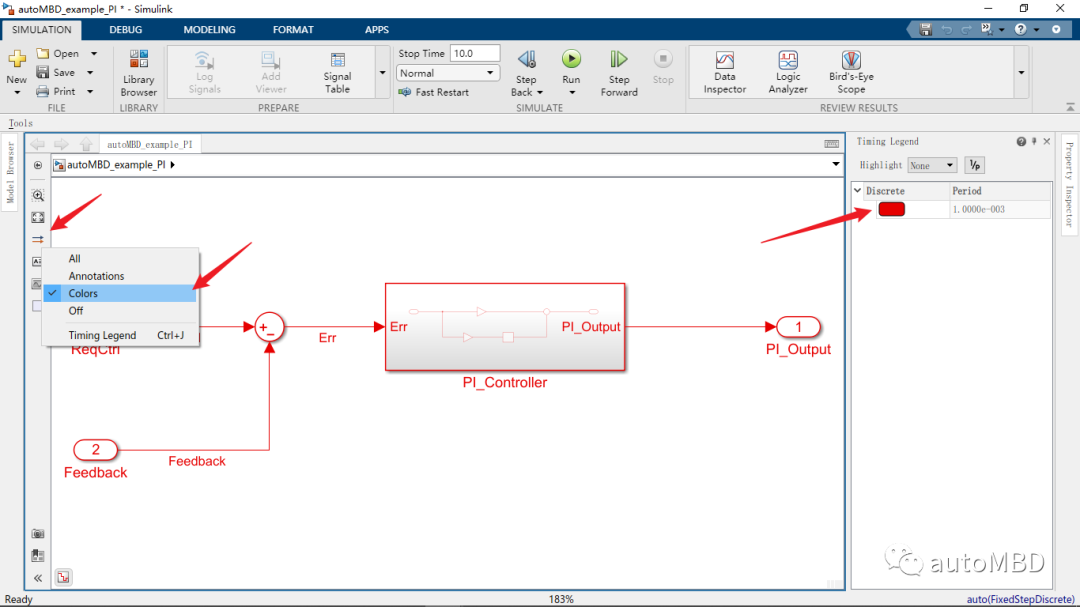

MBD的Simulink使用技巧:详解代码生成中的模型与代码(2)

LMK04821芯片项目代码详解

LMK04821芯片项目代码详解

评论