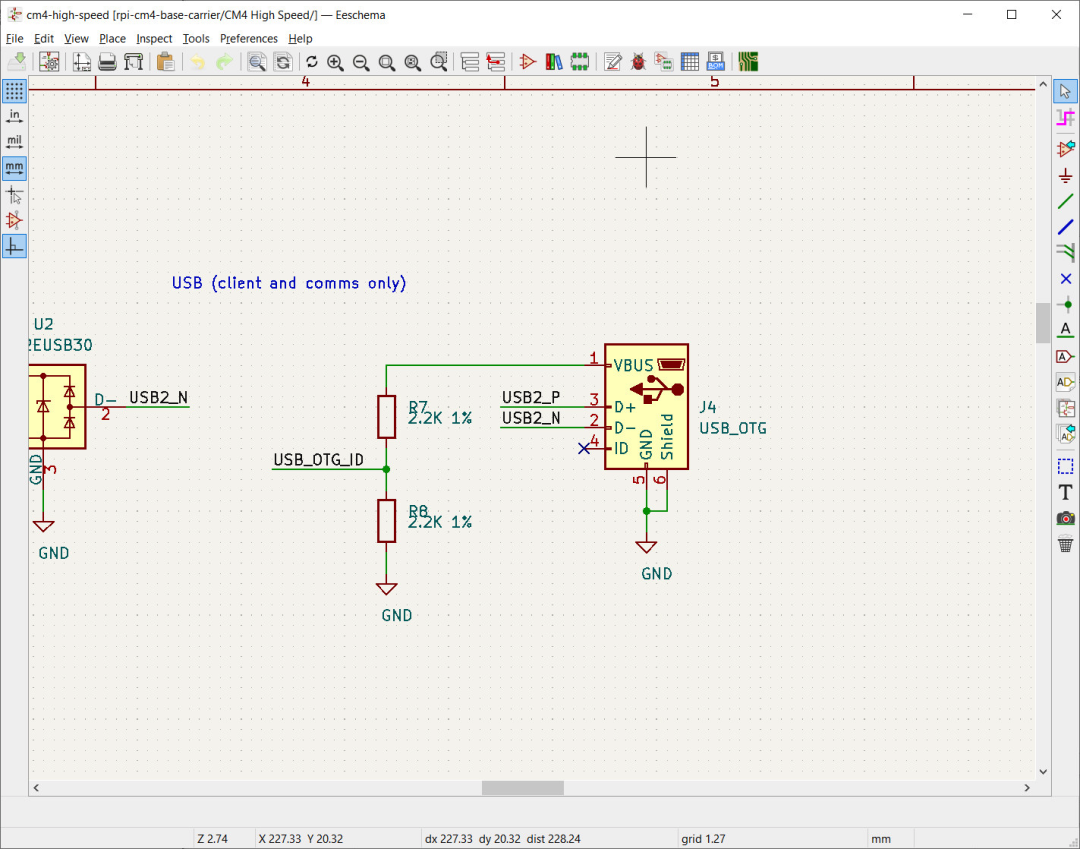

在PCB布局软件中进行差分对走线是一个棘手的过程。幸运的是,KiCad有一些工具可以帮助我们完成这个过程。在本教程中,我们将带领您完成计算差分阻抗的过程,并基于此通过一个项目创建一对USB数据线。

先做一些研究

在对任何高速信号总线或差分对走线进行布线之前,最好对这些信号的要求做一些研究。

以USB2.0高速总线为例,我们可以先下载USB2.0规范作为参考。这个规范的内容非常多,所以仅作参考,同时阅读其它一些易于迅速理解的文档。比如下面一些文章可以帮助你理解如何对USB2.0高速数据线进行布线:

https://www.silabs.com/documents/public/application-notes/an0046-efm32-usb-hardware-design-guidelines.pdf

https://www.ti.com/lit/an/slla414/slla414.pdf?ts=1605978923732&ref_url=https://www.google.com/

https://octavosystems.com/app_notes/osd335x-design-tutorial/osd335x-lesson-2-minimal-linux-boot/osd335x-lesson-2-usb-circuitry/

此外,这里有一些工程师关于做USB数据线走线的不错的讨论:

https://electronics.stackexchange.com/questions/325721/do-usb-data-wires-d-d-have-90-ohm-differential-impedance-and-single-ended-45

https://electronics.stackexchange.com/questions/41851/how-critical-is-the-layout-of-usb-data-lines-how-does-my-layout-look

https://electronics.stackexchange.com/questions/311310/understanding-usb-differential-and-single-ended-impedance-requirements

https://electronics.stackexchange.com/questions/446692/routing-long-usb-2-0-high-speed-traces-microstrip-or-stripline

通过这些文章的阅读,我们可以确定一些要求:

数据线之间的差分阻抗应为90 Ω +/- 15%。

每条数据线的单端阻抗(相对于GND)应为45 Ω +/- 15。

数据线总长度差不大于0.150英寸(3.81 mm)。换句话说,尽量保持D+和D-的长度不变。

数据线应尽可能在不间断的接地面上布线。

在可能的地方避免做90°直角走线(包括过孔)

避免在走线上留下不连接任何地方的分叉

确定PCB的特性

去你想要制板的PCB制造商的网站,找到你计划生产的电路板的特性说明。比如下面是来自一些快板厂的网站上的典型参数:

1盎司铜(走线为1.4 mil或0.036 mm厚)

1.6mm的板厚

FR4材料

2层板

6 mil (0.1524 mm)最小走线宽度

6 mil (0.1524 mm)最小走线间距

注意,这是一个2层板! 在2层1.6毫米厚的板上布线差分对通常是相当困难的,因为数据线需要很宽才能达到所需的阻抗。使用更薄的板(例如铜层之间0.8毫米厚的介质材料),可以使用更窄的走线用于差分对信号。通常,你会发现4层以上的PCB板可以在铜层之间提供较薄的介电材料(如FR4)。

KiCad中的Net Name命名

在创建原理图时,必须使用以下后缀之一来命名差分对信号的Net Name:

+/-(例如D+和D-)

_P/_N(例如D_P和D_N)

KiCad在PCB布线使用差分对走线工具时会自动查找这些后缀对。

使用KiCad阻抗计算器

KiCad在项目管理器面板中有一个内置的阻抗计算器,在项目管理器面板中,选择:工具》计算器工具,选择“传输线路”选项。

传输线计算器选项卡为计算阻抗提供了几个选项。我们想为差分对使用左侧的“耦合微带线”选项。开始填写基板参数部分。

注意,你可以点击“…按钮的一些参数得到弹出窗口选择您的材料。对于这些,我们使用铜作为导体,FR4作为介质材料。

Er(介电常数):4.5

TanD(介电损耗系数): 0.02

Rho(导体的特性电阻):1.72e-08

H(走线距离底部接地平面的距离):1.6 mm(板厚)

H_t(走线和顶部地平面之间的距离):10000毫米(我们使用最外层进行查分对走线,这个参数可以设置比较大甚至近似无穷,如果你在两个地平面之间走线,可以设置这个参数为FR4厚度)

T(铜厚度):0.03556 mm(对应1盎司铜)

Rough(表面粗糙度):0(我们的计算不需要)

mu Rel C(导体相对磁导率):1(计算中不需要)

在物理参数部分,我们输入所需的走线设置。我们在开始的时候一般都会设置差分对两线之间的距离尽可能小,这样也会让走线更窄,后面会根据需要修改走线的宽度(W),直到达到所需的差分阻抗。注意,走线的长度(L)并不重要。

开始的差分线之间的间距为0.1524 mm (一些快板厂需要的最小值),并调整走线宽度(W),直到你得到一个Zodd约45 Ω。注意,Zdiff(差分阻抗)等于2 * Zodd,因此Zodd为45 Ω给出了Zdiff为90 Ω。按下“分析”按钮来计算电气参数。

我们会发现,0.77毫米的走线宽度可以让差分阻抗非常接近90 Ω。

PCB板的设置

打开PCB布局工具(pcbnew),进入文件》板设置。确保您的设计规则》约束符合您的制造商可以生产的。然后,前往项目》网络类。

用您的差分对名称添加一个新的网络类(我给我的名称为“USB Data”)。将间隙设置为制造商的最小值,并将走线宽度(单根走线)设置为与默认类的宽度相同。改变DP宽度为我们计算的线宽(0.77 mm),改变DP间隙为我们计算的间距(0.1524 mm)。

在右下角,高亮两个差分对网名。在分配网络类,选择您的差分对网络类名称(在此为“USB Data”),并单击分配到选定的网。现在,你的差分对线将遵循我们刚刚创建的网络规则。

差分对走线

点击走线工具(或按“x”键)进入走线选择模式。在本例中,由于封装的焊盘非常小,我们需要在使用差分对工具之前先离开焊盘。点击差分对线中的其中一个。

您可能会发现(如果DP宽度很大,就像这个2层板的情况一样),KiCad不希望对线路进行走线。所以,在走线工具仍然激活的情况下,右键单击》选择通过/走线宽度》使用自定义值…

再次左键单击以开始走线跟踪。尽量从焊盘均匀地扇形离开,避免90°弯曲。

单击“走线》差分对走线”。单击其中一个走线,工具将自动开始使用指定的参数来完成这两个走线。

如果你的走线距离太远,你应该将你的“扇形”轨迹移近一点,因为你需要差分对尽可能保持准确的分离距离。您还可以让差分对开始向另一个方向移动,以允许工具匹配差分对线之间的间距。

继续在元件之间进行走线。注意,如果你需要在某些地方停下来(比如,上拉/下拉电阻),你应该尽量通过这些焊盘,避免分叉。

走线应尽可能地直,避免不必要的转弯。有时候,你需要走线到板的外部边缘的连接器,所以不得不使用45°拐弯来逐渐弯曲。

同样,如果差分对的宽度相对于终端元器件的焊盘过大,可以使用具有自定义宽度的单走线,将导线引入到焊盘上,但要尽量避免这种情况。

走线长度尽可能一致

对于高速总线,您几乎总是希望总线上的每一个数据位在同一时间到达目的地(或尽可能接近同一时间)。如果走线的长度不同,每个数据位到达的时间也可能不同! 这就是所谓的“位偏差”,可能会对通信总线造成严重破坏。

通过选择工具,选择差分对线中的其中一根,查看一下它的总长度。

点击另一根线,从第一个网减去那个网的长度。对我来说,我得到21.1484毫米- 18.0616毫米= 3.0868毫米。这在USB数据线的允许偏差3.81 mm范围内,所以我应该没问题。

注意: 我还没有测试这个板,我没有一个足够好的示波器来验证我的走线是否良好。如果您有一个可测量480MHz的示波器,可以使用“眼图”或“眼模式”来进行测试。

要修复不匹配的长度,可以使用差分对的走线》调整偏差工具。启动工具,点击净长度较短的走线段。右键单击并选择长度调优设置…打开调优选项。

在大多数情况下,你会希望偏差为0。请随意调整其他参数,以满足您的PCB制造要求。单击OK。

沿着您希望调优的走线移动鼠标,当工具试图找出如何增加较短的轨迹的长度时,您应该会看到蛇形路径出现。

注意:在上面的例子中,我假设我使用0.8毫米厚的PCB与0.003英寸(0.0762毫米)的线间距。这使得我可以在演示中使用更薄的数据线,因为工具与我实际电路板上的超宽走线不兼容。

你通常想要蛇形部分被添加到更接近不匹配发生的地方(对我来说,这是更接近Hirose连接器,因为路径通常更直靠近USB连接器)。工具还会告诉你添加的东西是否修复了偏差。

单击“接受路径修改”。

注意,如果您正在与一个大型的并行总线(超过2数据行),您可以使用“走线”》“调整单走线长度”来添加蛇形走线到较短的走线,使这些走线的最终长度与最长的数据线长度一致。

编辑:jq

-

电阻

+关注

关注

85文章

5037浏览量

169616 -

阻抗

+关注

关注

17文章

893浏览量

45358 -

计算器

+关注

关注

16文章

425浏览量

36496 -

KiCAD

+关注

关注

4文章

44浏览量

8578

原文标题:如何进行差分对走线(以KiCad中对USB布线为例)

文章出处:【微信号:DBDevs,微信公众号:数据分析与开发】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何计算集成放大器ADC失调误差和输入阻抗?

示波器探头的小阻抗和幅值解析

解析完成计算差分阻抗的过程

解析完成计算差分阻抗的过程

评论