本文将介绍如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真。

Icarus Verilog

Icarus Verilog极其小巧,支持全平台Windows+Linux+MacOS,并且源代码开源。通过tb文件可以生成对应的仿真波形数据文件,通过GTKWave可以查看仿真波形图,支持将Verilog转换为VHDL文件。

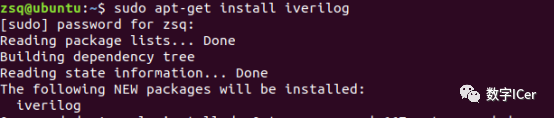

1.安装iverilog:

sudo apt-get install iverilog

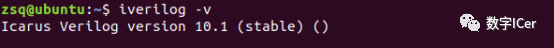

安装完成查看版本

iverilog -v

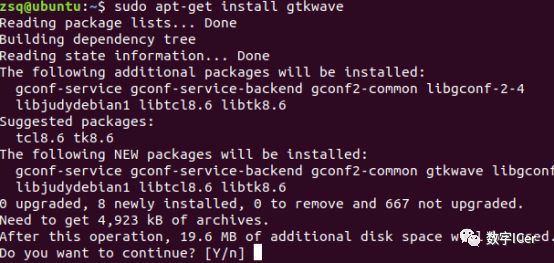

2.安装gtkwave:

sudo apt-get install gtkwave

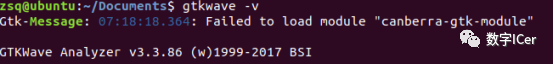

安装完成查看版本

gtkwave -v

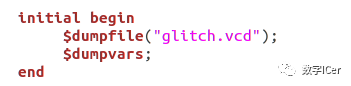

Tb中添加

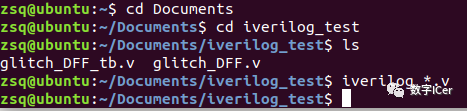

3.编译:

进入文件目录,输入命令:

iverilog *.v

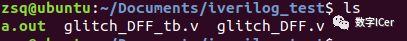

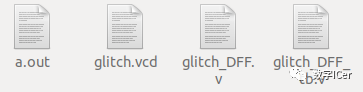

编译完成出现.out文件

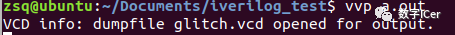

生成.vcd文件

vpp a.out

执行后产生的文件如下:

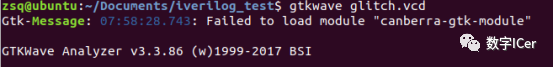

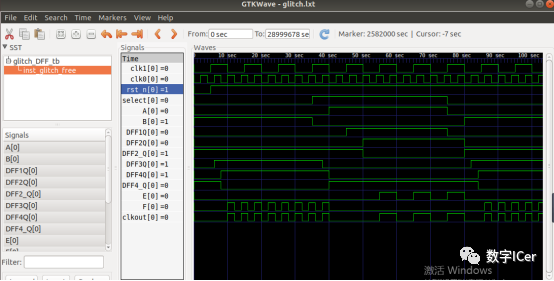

4.用GTKWave打开VCD文件:

gtkwave glitch.vcd

执行完成后,弹出界面

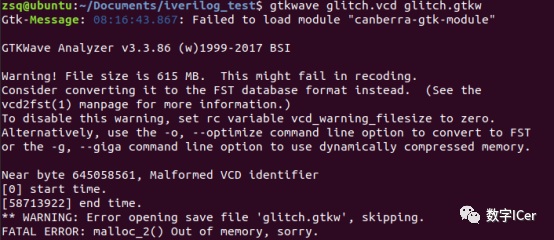

添加波形的时候卡死

glitch.vcd文件太大???

解决:

gtkwave,icarus支持vcd,lxt,lxt2 dump.

vcd通用但vcd dump太大,gtkwave不能很好的查看波形,导致崩溃。所以最好之前用lxt或将vcd转化为lxt格式。lxt格式是gtkwave的专用格式。

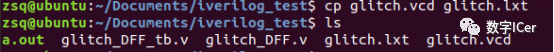

cp glitch.vcd glitch.lxt

添加波形

5.Verilog转换为VHDL

将glitch.v文件转换为VHDL文件glitch.vhd

iverilog -tvhdl -o glitch.vhd glitch.v

编辑:jq

-

仿真

+关注

关注

50文章

3871浏览量

132132

原文标题:开源verilog仿真工具iverilog+GTKWave初体验

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

verilog inout用法与仿真

使用nuclei stuio将软件程序编为.Verilog,在vivado中仿真出现的问题求解

为什么按照demo_nice的例子编译时候无法生成.verilog文件呢?

NICE自定义指令如何被编译生成汇编文件和.verilog二进制文件?

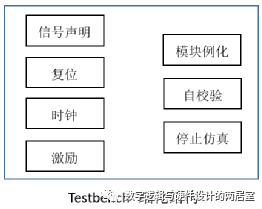

Verilog Testbench怎么写 Verilog Testbench文件的编写要点

Verilog代码封装后门访问

介绍下Verilog系统完整的8种编译指令

从仿真器的角度理解Verilog语言2

从仿真器的角度理解Verilog语言1

如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真

如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真

评论