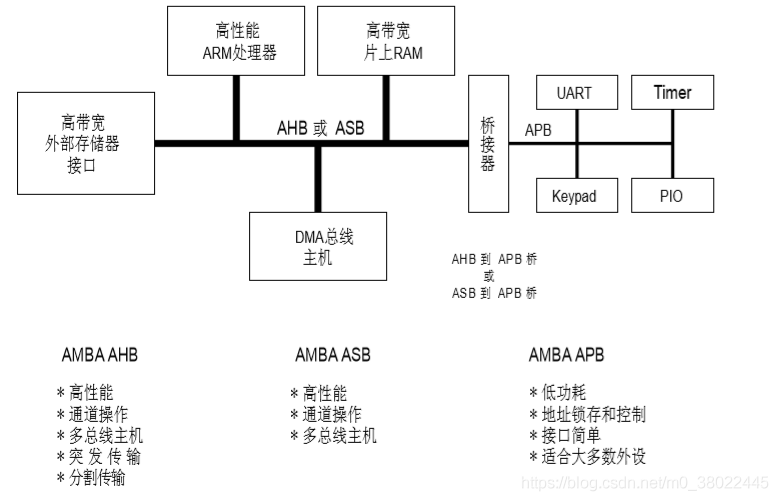

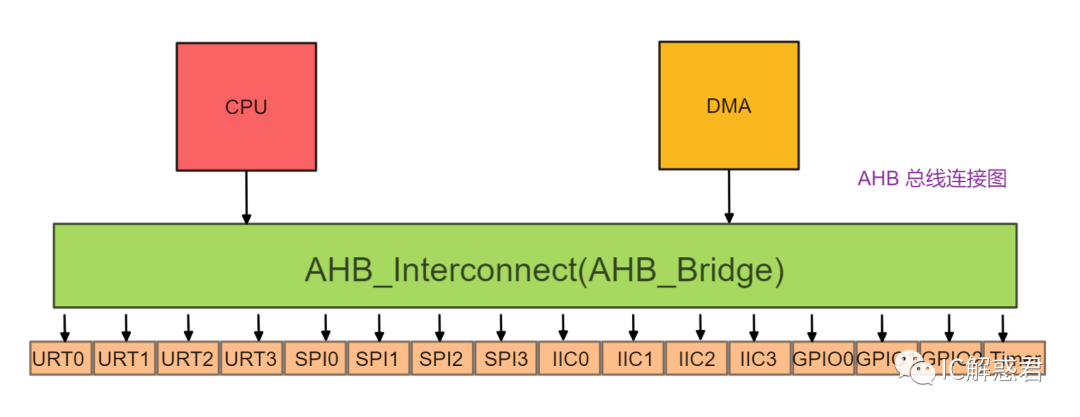

AHB(高级高性能总线):用于高性能高时钟频率的系统模块,AHB 担当高性能系统的中枢总线。AHB 支持处理器,片上存储器,片外存储器以及低功耗外设宏功能单元之间的有效连接。

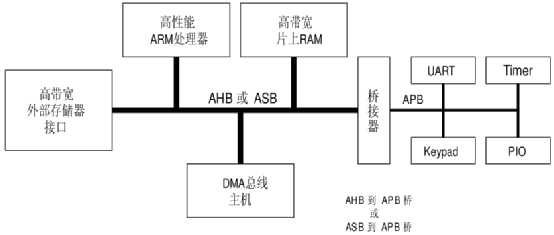

下图为典型AMBA系统:

AHB总线特征:

流水线操作/支持多个主线总设备(EMI/APB_bridge/DMA/CPU/DSP/LCDC)/上升沿触发操作

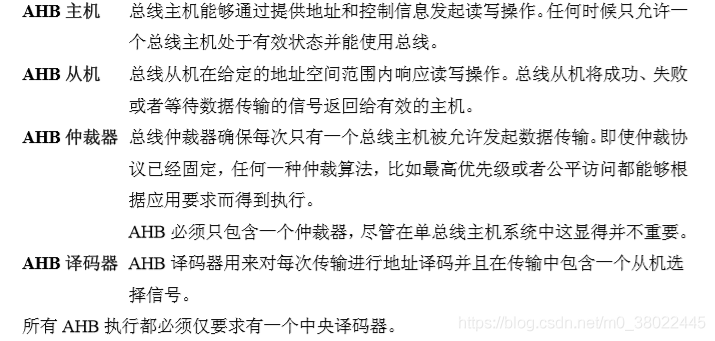

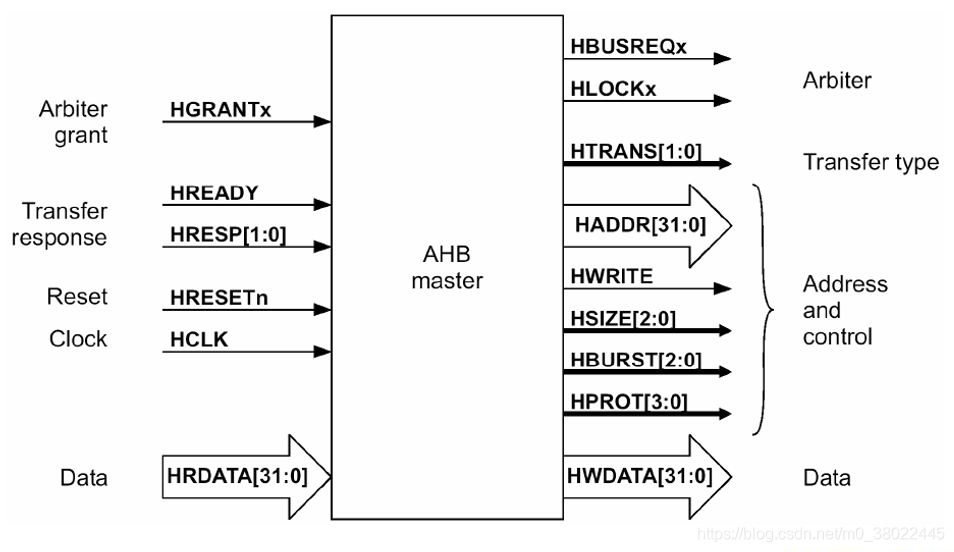

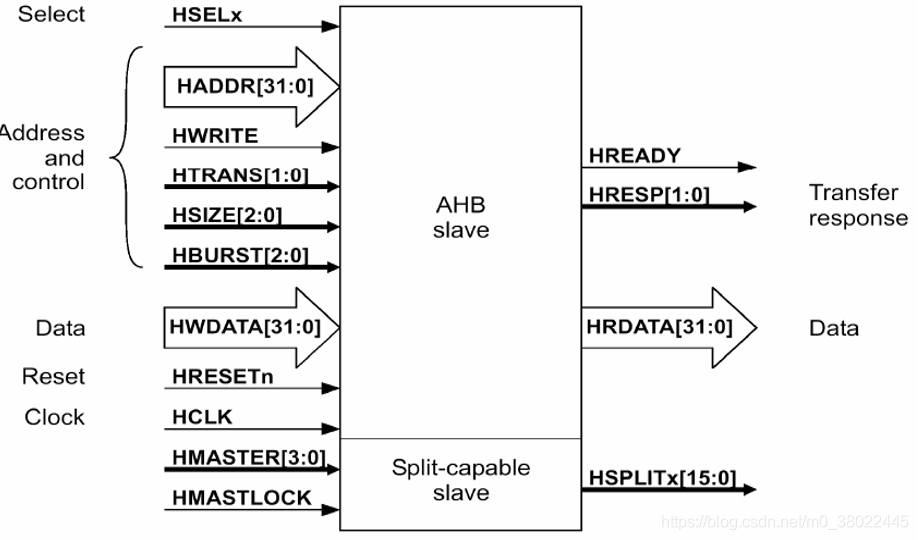

典型AHB总线包含:

AHB信号列表:

AHB主/从设备端口:

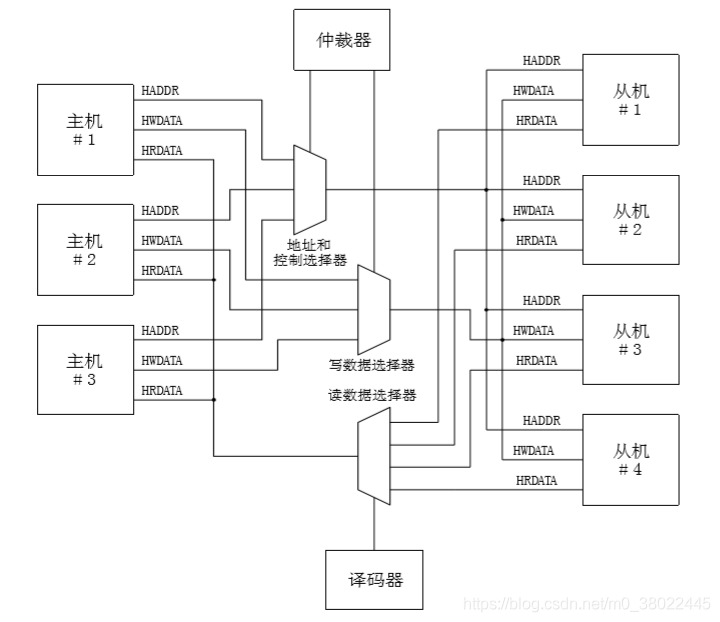

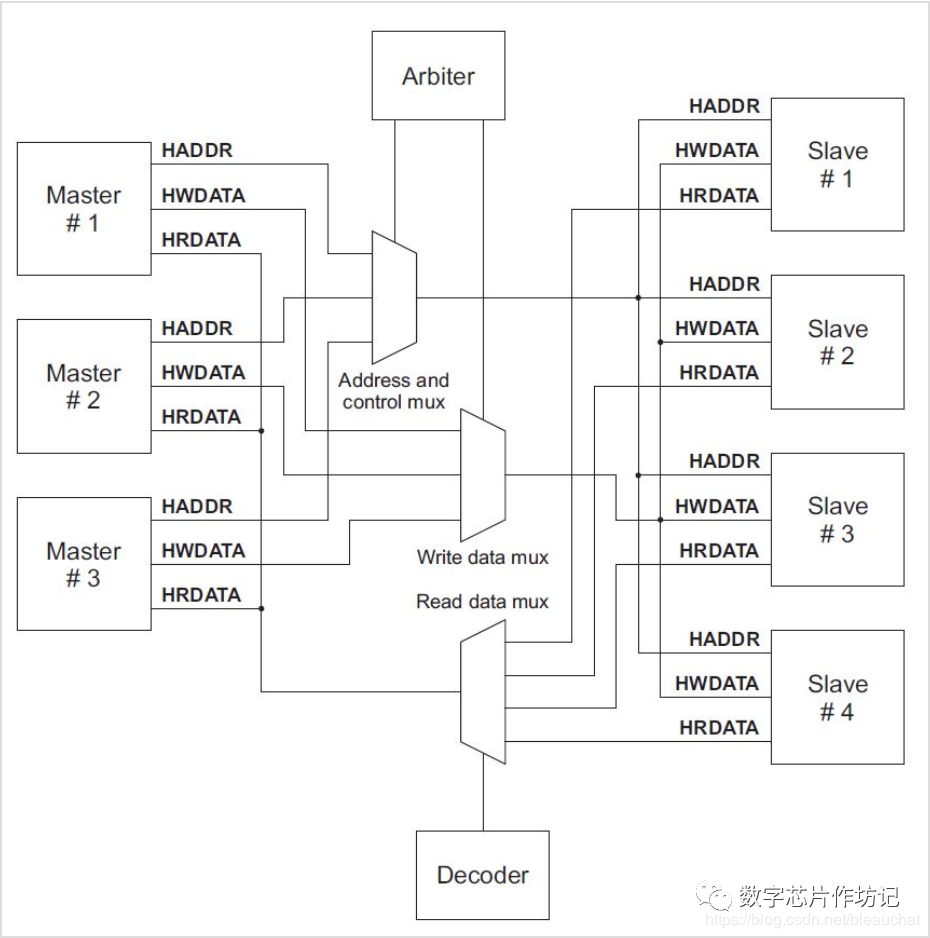

AHB结构:

AHB中,写数据总线用来将数据从主机传输到从机上,而读数据总线用来将数据从从机传输到主机上。

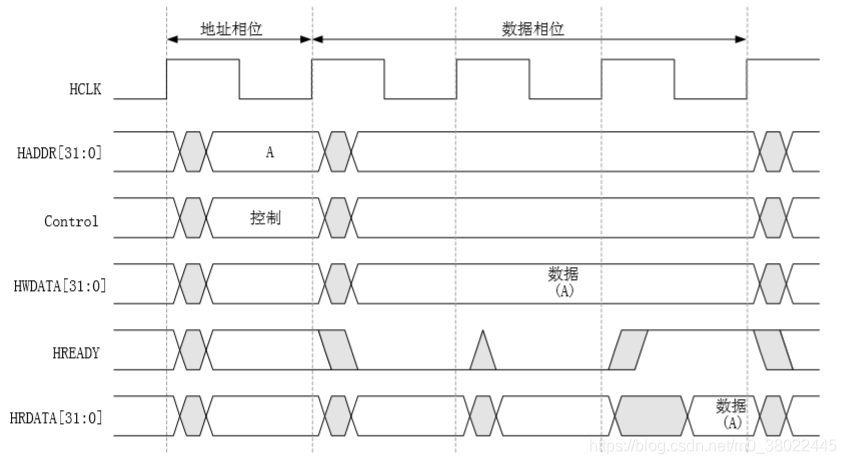

AHB简单传输分析:第一个HCLK上升沿后将地址和控制信号驱动到总线上,第二个上升沿到来,由于HREADY为1则数据写,HWDATA存在一定延时,再过一段延时后数据到达HRDATA

AHB等待传输 :HREADY=0表示从机让主机等待,等恢复1后进行传输

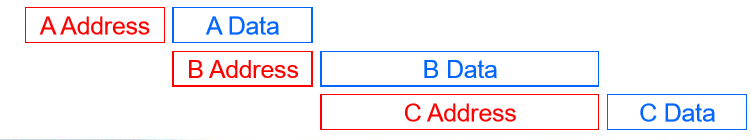

AHB的流水线传输:到地址A和C都为无等待传输,到地址B由于HREADY=0为一个等待状态,传输到地址B的扩展数据相位对传输到地址 C 的扩展地址相位有影响,因为C的地址信号写入和B数据写入在同一周期。

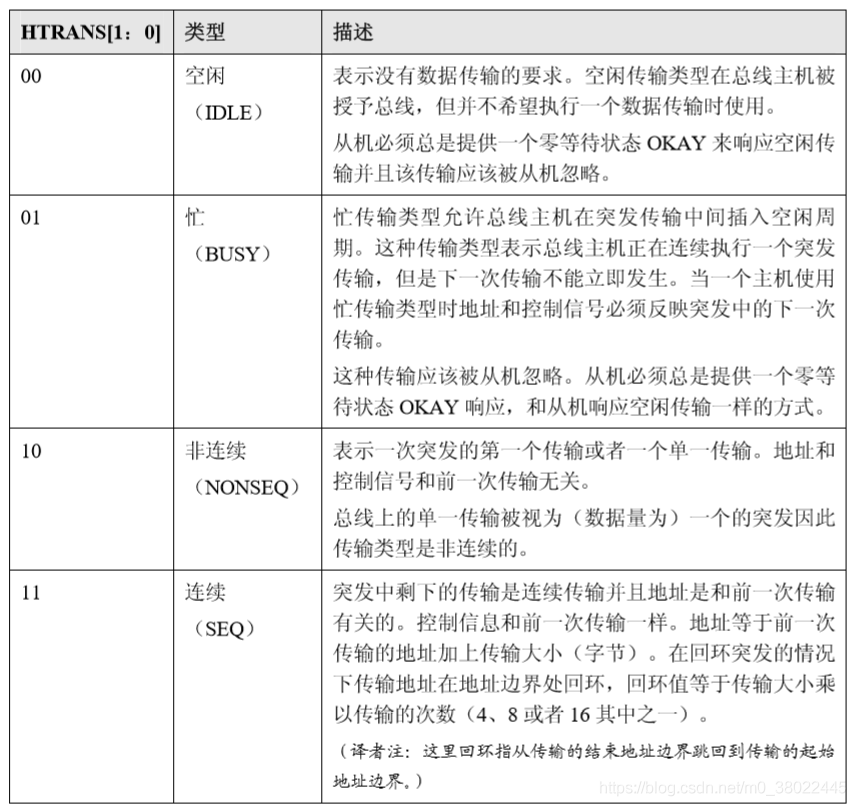

AHB传输类型可以分为4类:

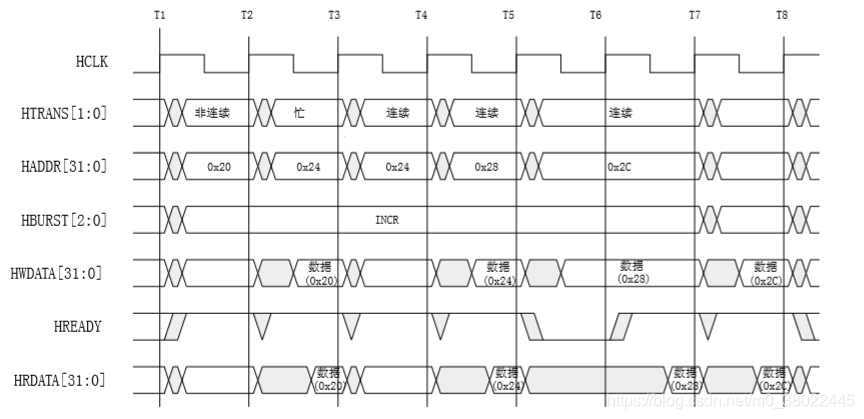

传输类型实例分析:

T1开始一个非连续传输,T1中将地址和控制信号写入;T2开始数据传输,T2原本有地址和控制信号写入过程,但是由于BUSY信号主机让从机等待一周期;第二个地址和控制信号顺延至T3,开始连续传输,T4开始第三个地址及控制信号/第二个数据信号传输,T5本来是进行第四个信号的地址和控制信号传输,由于HREADY为低,从机让主机等待一周期,主机信号保持,在T7后进行第四个数据信号传输

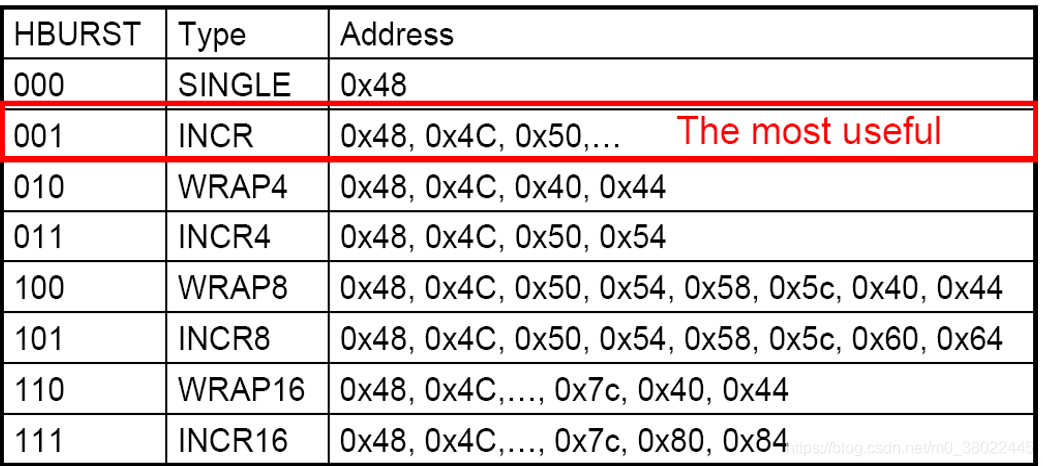

AHB中的突发操作,增量突发访问连续地址并且突发中的每次传输地址仅是前一次地址的一个增量;对于回环突发,如果传输的起始地址并未和突发(x 拍)中字节总数对齐那么突发传输地址将在达到边界处回环。例如,一个四拍回环突发的字(4 字节)访问将在 16 字节边界回环。因此,如果传输的起始地址是 0x34,那么它将包含四个到地址 0x34、0x38、0x3C 和 0x30;突发信息通过HBURST[2:0]进行判断:

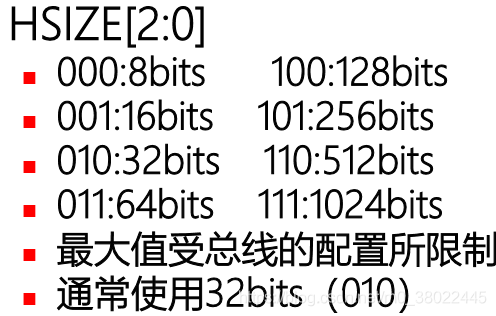

一次突发传输的数据总量可以用节拍数(1/4/8/16)乘以每拍数据的字节数来计算,每拍字节数由 HSIZE[2:0]指示:

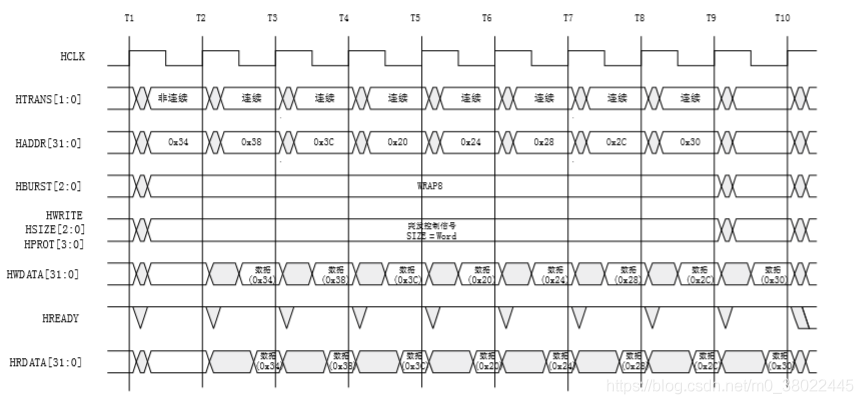

八拍回环突发传输时序(HSIZE=010):

8拍4字节,32为边界,时序图可见0x3C后回卷至0x20

AHB传输方向:HWRITE为高,该信号表示一个写传输并且主机将数据传输到写数据总线HWDATA[31:0]。当该信号为低时将会执行一个读传输并且从机必须产生数据到读数据总线HRDATA[31:0]

HPROT[3:0]信号:,提供总线访问的附加信息并且是给那些希望执行某种保护级别的模块使用的,用于表示传输是否为一次预取指/特权模式访问或用户模式访问,对于带有存储器管理单元的总线主机来说这些信号也表示当前访问是带高速缓存(cache)还是带缓冲的(buffer)。并不是所有总线主机都能产生正确的保护信息,因此建议从机在没有严格必要的情况下不要使用 HPROT 信号。

文章出处:【微信公众号:FPGA之家】

责任编辑:gt

-

处理器

+关注

关注

68文章

18257浏览量

222079 -

soc

+关注

关注

38文章

3742浏览量

215650 -

总线

+关注

关注

10文章

2703浏览量

87204

原文标题:SoC设计之AMBA总线-AHB总线详解

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

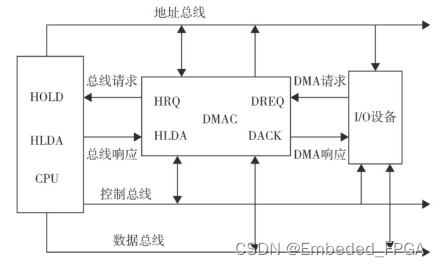

AHB与DMA详细解读

AMBA3.0 AXI总线接口协议的研究与应用

PrimeCell高性能矩阵(PL301)技术概述

PrimeCell AHB DDR和NAND内存控制器(PL244)技术参考手册

PrimeCell彩色LCD控制器(PL110)技术参考手册

多端口内存控制器(GX176)技术参考手册

PrimeCell AHB SRAM/NOR存储器控制器(PL241)技术参考手册

Arm AMBA 5 AHB5:加速嵌入式和物联网世界

剖析AHB2、AHB-Lite和AHB5区别

SoC设计AHB高级高性能总线的详细介绍

SoC设计AHB高级高性能总线的详细介绍

评论