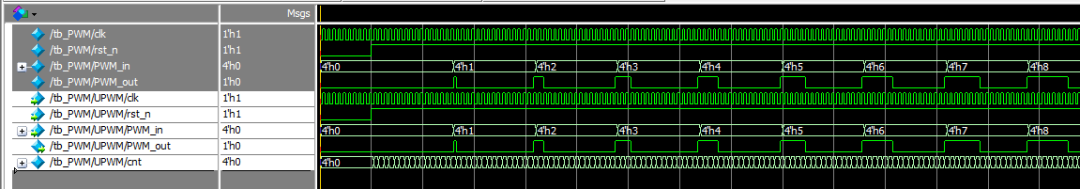

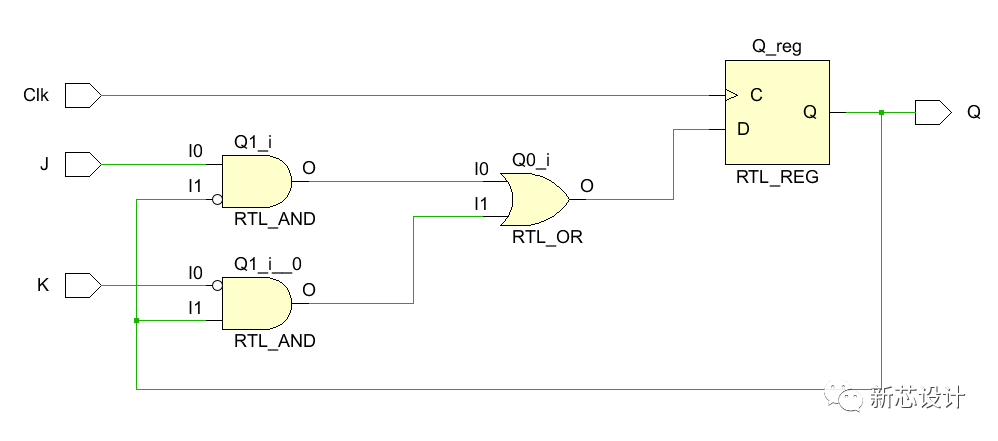

PWM 采用任意宽度的输入值,并创建只有一位宽度的输出。使用自由运行计数器的 PWM,这是能做的最简单的 PWM。

module PWM( input clk, input rst_n, input [3:0] PWM_in, output PWM_out);

reg [3:0] cnt;always @(posedge clk or negedge rst_n) if(!rst_n) cnt《=0; else cnt 《= cnt + 1‘b1; // free-running counter

assign PWM_out = (PWM_in 》 cnt)?1’b1:1‘b0; // comparatorendmodule

选择了一个4位的 PWM 这里,所以 PWM 周期是16。输入可以从0到15,因此 PWM 输出比从0% 到15/16 = 93% 。如果需要能够达到100% ,输入需要有一个额外的bit位。

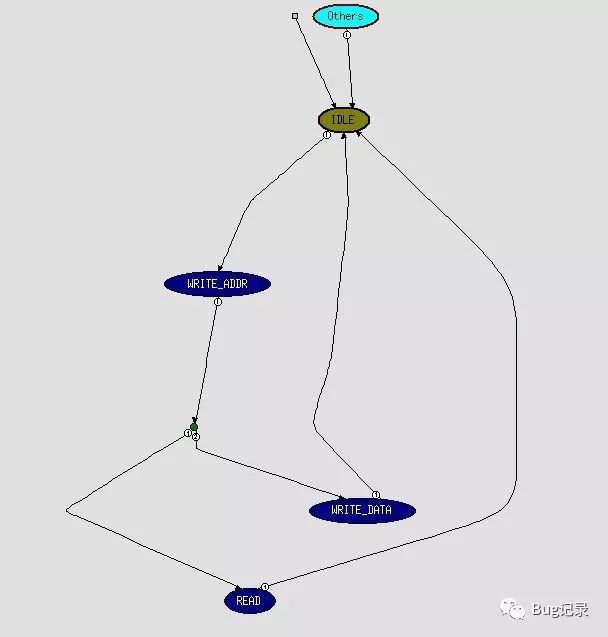

这段代码工作得很好,尽管当前形式的代码有点幼稚,因为输入必须是固定的(或者只有当计数器溢出 = 返回到0时才会更改)。否则输出将出现故障。因此,很可能需要一些额外的逻辑(通常是在正确的时间捕获输入的闩锁)

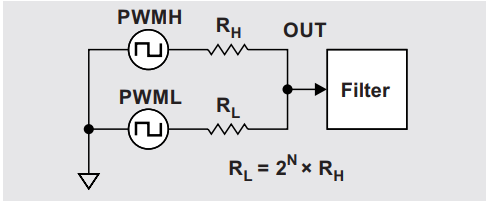

使用可加载的上下计数器的 PWM,这是一个稍微复杂一点的设计。

module PWM2( input clk, input rst_n, input [3:0] PWM_in, output PWM_out);

reg [3:0] cnt;reg cnt_dir; // 0 to count up, 1 to count downwire [3:0] cnt_next = cnt_dir ? cnt-1’b1 : cnt+1‘b1;wire cnt_end = cnt_dir ? cnt==4’b0000 : cnt==4‘b1111;

always @(posedge clk or negedge rst_n ) if(!rst_n) cnt 《= 0; else cnt 《= cnt_end ? PWM_in : cnt_next;always @(posedge clk or negedge rst_n) if(!rst_n) cnt_dir《=1’b0; else cnt_dir 《= cnt_dir ^ cnt_end;assign PWM_out = cnt_dir;endmodule

它使用一个可加载的上下计数器,不需要输出比较器。有趣的是,它并不完全等同于第一个设计,因为输出周期有17个状态而不是16个(输出从1/17 = 6% 到16/17 = 94%)。

编辑:jq

-

PWM

+关注

关注

114文章

4887浏览量

209837 -

比较器

+关注

关注

14文章

1523浏览量

106471 -

计数器

+关注

关注

32文章

2121浏览量

92903

原文标题:verilog 实现PWM DAC

文章出处:【微信号:leezym0317,微信公众号:FPGA开源工作室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

verilog语音实现浮点运算

在NuEdu,pwm_dac示例程序中,让pwm来供电,为什么pwm产生的是输出假象的电压?

WTN6系列语音芯片:PWM与DAC音频输出在PCB设计中的优势

如何提高PWM-DAC的输出精度

浅析基于verilog如何实现PWM DAC

浅析基于verilog如何实现PWM DAC

评论