作者:仲智刚,冯根宝,郁正庆

下一代网络(NGN- Next Generation Network)是以IP为核心,可以同时支持语音、数据和多媒体业务的融合网络,是通信网络的发展方向。传统的以电路交换为核心的设备正逐渐被以IP为核心的网络设备所替代。在这种演变过程中,设计一种能够提供PSTN与NGN无缝连接的网关设备,从而实现以较低的成本向NGN网络平滑过渡是目前各通讯设备制造商的重要研究课题。本文重点介绍了网关接口设备中核心器件,即NGN网关接口芯片的设计方法以及在Xilinx的Spartan3 XCS1000中的实现。

方案介绍

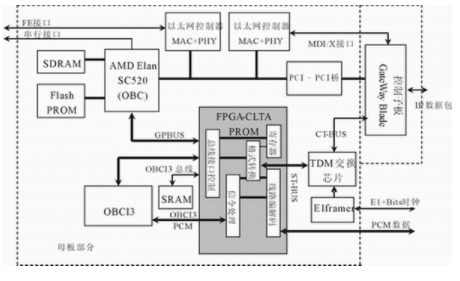

在本方案中,网关接口设备的主要功能是由网关接口板IP_GATEWAY所实现,包括母板与子板两部分,其中母板部分主要完成传统的语音和数据部分的格式转换以及信令处理,子板主要完成与媒体网关控制器MGC(Media Gateway Controller)的通信与控制功能,如H.248/Megaco 协议的处理、连接的建立与释放等。其基本结构如图1所示,母板部分主要包括CPU-AMD Elan520,专用处理芯片OBCI3、以太网接口芯片、FPGA控制芯片、PCI桥、交换芯片TDM、板上RAM/ROM,以及时钟、电源等模块;子板部分(Gateway Blade)主要包括CPU-BCM1122,以太网交换芯片以及两个DSP。限于篇幅,不做过多介绍。

如图1所示,FPGA控制芯片(CLTA)处于整个母板的核心地位,其主要功能包括:语音和数据格式转换,即将来自终端控制板的PCM格式语音和数据转化为适用于TDM芯片的ST_BUS总线格式; AMD-Elan520的CPU读写逻辑映射以及SRAM存取,DMA模式控制;OBCI3接口控制;线路端编解码功能。

图1 网关接口板功能结构图

设计描述

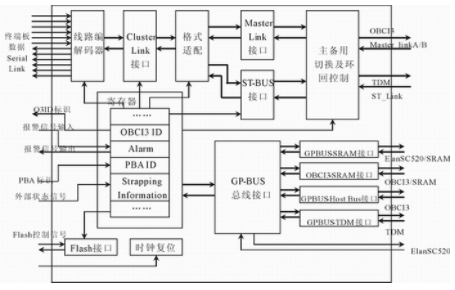

FPGA的主要功能模块如图2所示。处于框图上端的部分主要是数据流处理部分,主要完成数据格式转换以及信令提取和传递功能,同时还包括线路端的编解码功能;右边主要是控制部分,完成CPU对FPGA、OBCI3芯片以及片外SRAM的存取和控制功能;左下部分主要是FPGA寄存器模块以及如Flash保护,系统报警处理等辅助模块。

图2 FPGA内部功能结构图

数据流

从数据流角度看,FPGA包括与专用处理芯片OBCI3 相连的MasterLink[A,B],与终端控制板相连的Serial Link,与TDM芯片相连的ST_Link。为提高网关接口设备的可靠性,所有的数据流都包括A、B两路,分别来自主/备用设备,当其中一路发生故障时,系统自动切换到另外一路。以上行数据为例,从终端控制板来的Serial Link共分6路,其中每一路数据格式都是由A、B两路经过Manchester编码过的复用数据,A/B路复用数据在Coder/Decoder模块中经过线路端解码,恢复出A 、B两路Cluster Link数据,该数据采用PCM格式,其速率为4MHz,共分为32 个PCM 信道,每个信道16位,其中CH0 用于同步信道,CH16 用于信令信道,其它信道可以承载语音和数据,又叫SPATA 信道。16位的SPATA 信道包含了8位的语音编码和协议位,CH0包含同步编码,如表1所示:其中PP 是协议比特,当有告警时PP=11,否则为00,A=1时表明存在软件或硬件告警,M=1 时表明存在摘挂机事件。其中,13 、12以及7 “4为同步位,当上下游接口芯片以每125ms的间隔固定检测到同步码的时候,整个系统处于完全同步状态,否则,对端芯片会在CH16发出远端告警,用于通知网关设备进行故障处理。

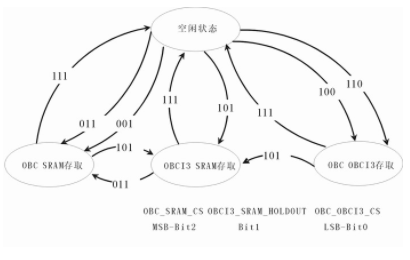

图3 控制状态机

CH16 是16位宽的控制信道,用于发送控制命令包或接收反馈包,用于控制终端控制板的操作。MasterLink 只承载同步和信令信道,不包括SPATA 信道,MasterLink 也包含A B两条链路。ST_Link是与TDM芯片相连的TDM 链路,满足标准ST-BUS 的接口要求,只承载8位的语音信道。FPGA将前述Serial Link经过Manchester解码后分离的A/B路数据分别进行8位数据提取,然后按照ST_BUS总线的格式分别放到各自对应的通道中,共12路ST_link数据。具体实现上,采用2个双口RAM,进行数据缓存后,按照ST_BUS格式按序读出。反之,FPGA进行ST_BUS到Serial Link的扩展。

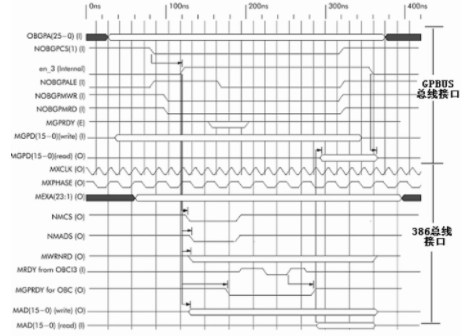

图4 GPBUS与386总线映射关系

由于CH0中包含报警以及摘挂机信息,因此,6路Serial Link中的CH0被按位或运算后发送给OBCI3,由OBCI3进行相应的检测和处理。反方向则将MasterLink 中来自OBCI3的CH0 广播到同组各个Serial link中的CH0,以提供同步功能。另一方面,MasterLink 上的两个CH16 用于控制远端终端控制板,CPU产生的控制信令通过OBCI3芯片,传送到MasterLink的CH16 信道上,并由FPGA广播到相应Serial Link 的CH16 中,相反方向,Serial Link的CH16信道中来自远端终端控制板的反馈响应,通过FPGA转发到MasterLink 的CH16 中,由OBCI3 接收,交给CPU处理。因此,最终ST_BUS上只包含SPATA的负荷,MasterLink只包含信令消息。通过TDM芯片,ST_BUS上的SPATA 信道进行一级交换后进入子板进行语音压缩、IP成包等后续处理。

控制流

如图1所示,母板上采用了AMD公司的Elan520,由于该CPU采用的是专用的GP_BUS总线协议,与片外SRAM通讯需做一定处理。另外,OBCI3是我们自行设计的专用处理芯片,其CPU总线接口采用Intel-386总线协议格式,因此,FPGA必须提供两组总线读写操作之间的逻辑映射。同时,OBCI3本身支持DMA模式存取SRAM,因此,FPGA还必须提供DMA接口的控制功能。

图3是在FPGA具体实现中所采用的状态机,系统共有4个状态,状态翻转的信号见图3右下侧,低为有效。当CPU没有总线操作时,系统为空闲状态;当CPU需要进行SRAM操作时,SRAM片选信号有效,系统进入OBC SRAM 存取状态,在此状态下,FPGA将CPU的操作映射为标准的SRAM时序,从而完成SRAM的读写操作。FPGA同时监测OBCI3的DMA请求信号,当状态为OBCI3 SRAM 存取时,如果CPU授权DMA请求,FPGA则激活OBCI3的HOLD_OUT信号,使OBCI3获得系统总线控制权,并启动DMA模式直接存取片外SRAM,从而大大加快了系统处理的速度。当CPU需要与OBCI3进行通讯的时候,系统进入OBCI3 存取状态,在该状态下,FPGA将异步的GPBUS总线逻辑的读写操作映射为同步的Intel-386接口时序,见图4。图中上半部分是GPBUS的读写时序,而下半部分则是经过FPGA映射后输出的标准386 CPU接口时序。图中箭头标明了两组总线控制信号之间的时序关系。

设计实现

本设计采用Xilinx的Spartan3-XCS1000实现。Spartan3系列器件采用90nm工艺,具有丰富的内部资源,包括17280个逻辑单元,120Kbit的分布式RAM和432Kbit的Block RAM,并提供了丰富的引脚接口类型。设计利用Synplify Pro 7.7进行综合,在ISE8.1中完成布局布线。经过系统验证,完全符合系统要求,现在已经进行批量生产。

结语

为顺利向下一代网络结构过渡,本文设计了NGN网关设备中的接口芯片,该芯片能够提供设备所需要的多种逻辑功能,极大地简化了电路板的设计。同时,设计本身采用可扩展的设计结构,可以满足系统扩展的要求。采用Spartan3系列FPGA实现,经过系统测试,完全符合设计需求。

责任编辑:gt

-

FPGA

+关注

关注

1600文章

21281浏览量

592853 -

芯片

+关注

关注

446文章

47705浏览量

408853 -

接口

+关注

关注

33文章

7616浏览量

148377

发布评论请先 登录

相关推荐

spartan3 xc3s400 bit文件转mcs

NGN协议发展现状和业务接口的成熟状况

测量spartan3静态功耗

iMPACT如何检测斯巴达设备?

Isthis Flash与Xilinx Spartan3 FPGA兼容吗?

请问我的Spartan3 / AN上的FPGA上有这个IP核功能吗?

是否有适用于SPARTAN3的VIVADO附加软件包?

QDR SRAM与Spartan3 FPGA的接口设计

基于Spartan3 XCS1000实现NGN网关接口芯片的设计

基于Spartan3 XCS1000实现NGN网关接口芯片的设计

评论