传统电信网络是个同步网络,电信局间和各局内部都要保持同步状态。因此必须有一个同步分配系统来保证经过线路传输的信号仍然可以保持原始的同步关系。在一个 PDH网络中,从T1或E1线路上恢复出时钟信号,同步供给单元(SSU)或楼宇综合定时供给(BITS)是网络同步中常用的一种方式,它主要是由主时钟为同步网络中的下一级设备提供时钟。BITS主要用于北美地区,在其他地方主要使用SSU。本文利用Dallas Semiconductor公司的DS26502为BITS/SSU应用或者使用T1/E1传送定时信息的系统提供一个完整的前端解决方案。

网络同步的基本概念

目前绝大多数电信网络都是同步网络,无论是2G的GSM、3G的CDMA还是目前热门的WiMAX网络,它们的运营和发展都必须首先解决同步问题。同步是指信号之间的频率或相位保持某种特定关系,即在相对应的有效时刻内以同一速率出现。对一个电信网络的所有时钟进行同步,是为了确保发送和接收节点以同样的速率对数据进行采样,防止数据传输丢失。一个公用电话交换网络(PSTN)能够正常工作需要同时实现比特同步、帧同步和网同步。

网络的同步以时钟分层结构为基础,如图1所示。顶层是主参考时钟(PRC)或主参考源(PRS),时钟精度最高,可以达到10-11。 PRC/PRS可以通过一个铯原子钟产生,或者通过GPS、GLONASS接收。接下来一层为同步供给单元(SSU)或楼宇综合定时供给(BITS)。 SSU/BITS具有保持性能,当它失去与PRC/PRS的同步后,可以产生一个短时间内精度高于其固有自由振荡精度的时钟。SSU/BITS通常采用由铷时钟驱动的数字锁相环(DPLL)来实现,可以是只具有时钟功能而不进行数据传输的独立产品。第三层是SDH设备时钟(SEC)或SONET最小时钟 (SMC)。SEC/SMC也具有保持性能,但其保持和自由振荡精度性能低于对SSU/BITS的要求。SEC/SMC通常采用由恒温晶体振荡器 (OCXO)或温度控制晶体振荡器(TCXO)驱动的DPLL来实现,可以是网络产品的一部分或某块单板。分层结构中的第二层及以下各层,只要其到 PRC/PRS的路径不中断,就可以拥有与PRC/PRS相同的时钟精度。

图1 网络同步时钟分层结构

目前有两个主要的标准组织负责制定网络时钟要求,Telcordia发布的GR-XXX-CORE主要面向北美地区,而ITU则通过ITU-T G.XXX系列文档面向全球其他地区。中国已建成的数字同步是建立在PDH环境下,即利用PDH电路传递定时信号。随着传输网由PDH向SDH的发展,传输所又制定了《SDH网传送同步网定时的方法》。中国采用2048kb/s和2048kHz两种信号,做为同步网标准的接口信号。2048kHz信号符合 G.703建议,而2048kb/s则同时符合G.703和G.704建议。

DS26502的基本功能

在早期利用PDH传送同步时钟时,由于没有专用的时钟恢复器件,通常的做法是利用集成成帧器(FRAMER)的单片T1/E1收发器,例如 DS2155的线路恢复时钟RCLK,来做为同步的接收。采用这种方案可以完成同步时钟的传送,但是它同样存在一些缺点,因为单片收发器不是专用时钟恢复芯片,所以首先会有很多管脚闲置,导致资源浪费,设计复杂,在一些无关的处理上造成不必要的功率消耗。此外,在时钟配置方面由于没有特别的处理,因此无法实现ANSI/ITU-T关于同步时钟信号的某些特殊要求。

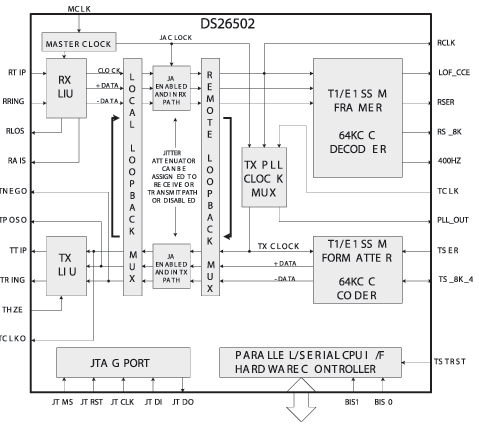

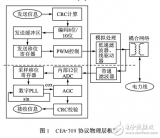

DS26502是Dallas Semiconductor公司推出的SSU/BITS专用时钟恢复器件,系统结构如图2所示。它的接收端可以从T1、E1、64kHz复合时钟 (64KCC)和6312kHz同步定时接口恢复出时钟,在T1和E1模式下,还能恢复同步状态消息(SSM)。发送部分可以直接连接到T1、E1或 64KCC复合时钟同步接口,在T1和E1模式下也能够提供SSM。在DS26502支持的输入和输出同步时钟频率内,它能够实现频率的任意转换。另外, DS26502还具有单独的输出,用来提供6312kHz时钟信号。

图2 DS26502的系统结构

在物理特性方面,DS26502可以通过软件设置,同时支持长距和短距,无须更改硬件就可以匹配75/100/110/120等不同线路接口;在进行冗余设计时,为了方便进行保护切换,通过器件引脚可以实现发送端输出的快速关断;芯片内部的抖动衰减器既可以放在发送侧也可以放在接收侧,并且具有旁路模式;当线路出现LOS、AIS和LOF等状态时,有硬件管脚输出指示,通过连接LED灯可以方便查找发现问题;控制方式多样,可以通过并行、串行或者硬件控制器端口进行读写,采用8位并行控制端口时可以选取Intel或Motorola两种总线模式,串行方式时采用通用的SPI接口。在协议方面, DS26502符合ANSI关于T1和ITU-T关于E1的所有指标,符合G.703 2048kHz同步接口和64kHz中心化(选项A)和同向定时接口,符合G.703附录II中64kHz和6312kHz日本同步接口。

DS26502的应用

DS26502有两种主要的工作模式:软件模式和硬件模式,它们主要的区别是器件的控制方式不同。软件模式时,微控制器使用串行或并行总线与图2中 DS26502内部的控制寄存器连接,由这个外部控制器对DS26502进行初始化、数据读写等操作;在硬件模式中,原来的串行或并行通信接口引脚被重新赋予功能,通过这些引脚新的逻辑定义,就能在没有外围处理器的情况下直接控制DS26502的内部工作。这是硬件模式的优点之一。实际设计中,是否采用硬件模式要取决于具体应用的特殊要求。设计当中需要重点考虑目标应用是否会用到一些只能在软件模式下使用的功能,这也是采用硬件模式的一个局限性,有些功能在此模式下无法使用,或者有些功能无法像软件模式那样进行设置,比如软件复位、中断屏蔽以及状 态寄存器的读写等都无法进行。

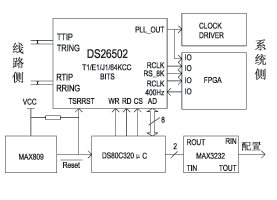

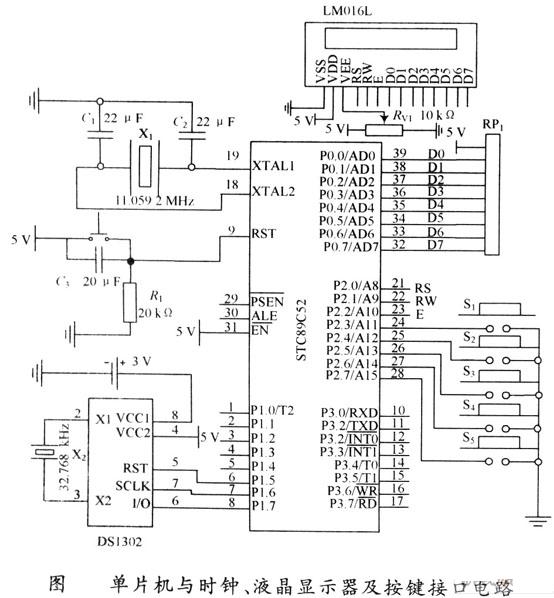

为了充分利用DS26502的特性,在设计中采用软件方式进行设计,如图3所示。选取高速八位单片机DS80C320作为主控制器,整板采用MAX809来做复位控制。

图3 DS26502的应用框图

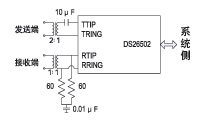

DS26502的线路侧设计与标准T1/E1电路设计完全相同,图4为接口电路。它的LIU接口可以在T1/E1/64KCC/6312kHz网络间通过软件切换,无须改动外部设计。这里的64kcc是指符合 G.703的64kHz同步接口,此时64kHz时钟信号通过编码内含8kHz和400Hz两个频率。LIU的发送和接收完全独立,这意味着发送端可以与 T1(E1)电路相连,而接收端采用E1(T1)模式。需要注意的是,在G.703规范中关于如何进行6312kHz的脉冲成形并没有明确规定,所以 6312kHz和其他模式略有不同。接收时,6312kHz与其他模式相同,通过RTIP和RRING进行接收,但发送时它只是TCLKO管脚输出的一个 0~3.3V的信号,并不通过TTIP和TRING送到线路上输出,需要由外部滤波器来实现6312kHz的正弦波形。

图4 DS26502的接口电路

当线路接口需要连接到一个监测端口时,由于E1/T1线路端接电阻和监测端口的隔离电阻分压的关系,此时线路中存在阻性衰减,所以需要E1/T1接收线路能够提供不同的接收增益。DS26502针对这种应用,可以提供接收侧的监控应用模式,通过设置MM0和MM1两个寄存器,DS26502可以提供最高32dB的接收增益,补偿分压后信号幅值降低的问题。需要注意的是,这种纯阻性的损耗和增益与E1/T1传输线路上的电缆损耗特性不同。

DS26502的输出端就是需要从线路中提取的2M同步时钟。这个时钟一路送入FPGA进行处理,这样可以提高灵活性,方便改变单板的管脚配置,另一路送入时钟驱动器供本板其他器件使用。DS26502除了可以从线路中提取时钟外,也可以接收ITU G.703第10部分中规定的2.048MHz的同步方波时钟。

同步状态信息SSM(Synchronization Status Message)用于在同步定时链路中传递定时信号的质量等级,使得SDH网和同步网中的节点时钟通过对SSM的解读获取上游时钟的信息,对本节点的时钟进行相应操作(例如跟踪、倒换或转入保持),并将该节点同步信息传递给下游。它采用4bit编码,共16种信号,反映不同的质量等级。由于2Mb/s信号传输距离长,又有同步状态信息(SSM)功能,因此在同步网络中优先采用2Mb/s信号。DS26502可以在T1和E1模式下方便的提取插入SSM信息,同时它支持2Mb/s信号。在E1电路中,Sa位用来发送和接收同步状态信息,最基本的Sa/Si位读取方式可以基于CRC4多帧方式,也可以基于双帧方式,通过DS26502的软件接口,可以读写到接收和发送的Sa/Si位。在T1模式下,DS26502通过BOC控制器直接读写同步状态信息。

软件流程

图3单板的系统初始化和配置如下:DS26502在上电后会马上自动复位,清除所有可写的寄存器空间,等待复位完成后,可以通过查询寄存器检测器件的ID号。上电复位后LIRST(LIC2.6)寄存器需要从0置为1,来对线路接口电路进行复位,这将初始化时钟恢复电路的状态机,对抖动衰减器重新进行中心定位,这一过程大概需要40ms。除了上电复位外,单板可以在任何时候通过拉低TSTRST管脚硬件复位,或者通过模式寄存器中的SFTRST位软件复位,复位过程 中所有操作将会中断。复位完成后,系统开始配置时钟,容许时钟系统适当调节后,开始对寄存器空间初始化,包括寄存器保留位的写入。因为复位后系统默认关闭所有中断,所以需要对中断控制寄存器中特定的位写1来打开相应的中断,因此按照具体应用初始化中断寄存器,打开不同的中断位,此时系统就可以正常工作,等待处理中断和锁定的各种状态信息。当出现中断时,系统首先读取中断信息寄存器来判断是哪个状态寄存器产生了中断,然后通过检查这个状态寄存器来最终确定真正的中断源。

结论

本文针对目前同步网络的现状,采用BITS接口芯片DS26502设计了一个前端接口电路,实现了ANSI/ITU-T等标准组织关于网络时钟的各种要求。

责任编辑:gt

-

芯片

+关注

关注

446文章

47705浏览量

408886 -

收发器

+关注

关注

10文章

2966浏览量

104708 -

振荡器

+关注

关注

28文章

3508浏览量

137614

发布评论请先 登录

相关推荐

基于DS3231的高精度时钟接口设计

基于DSP和DS12CR887时钟芯片实现微机保护装置的接口设计

DS26504 pdf datasheet(时钟恢复器件芯片

DS26502的硬件控制模式

DS2155 and DS26502 Software Co

时钟芯片接口分析与DS1302典型原理电路图

ds1302是什么接口,DS1302时钟芯片接口分析详解

DS26502LN+ - (Maxim Integrated) - 时钟/计时 - 专用

DS26502L+ - (Maxim Integrated) - 时钟/计时 - 专用

基于DS26502时钟恢复芯片实现前端接口电路的应用设计

基于DS26502时钟恢复芯片实现前端接口电路的应用设计

评论