1 改装系统简介

飞机航空电子系统的改装,就是把功能相对独立的子系统逐步走向综合,例如将雷达、惯导、GPS和机载计算机联合,组成新型航空图导航系统。通俗点讲,就是将那些“傻、大、粗、笨”的仪器仪表,集成为“少而精”的智能仪表,减轻飞行员的操作难度。

系列多机型改装时的多功能显示器,它将原来分散显示的信息和数据集中在一台多功能显示器上。替换掉原来“老死不相往来”的各种导航仪表,不再需要领航员大量记忆枯燥的数据,减少了仪表种类,节省了宝贵的空间,极大减轻了领航员工作强度。图1中除了地图视频采用LVDS外,其它仪表通信都采用ARINC429总线。显然,解决多通道的ARINC429通信成为本次改装的瓶颈。

传统的ARINC429通信设计中,大多采用HARRIS公司的HS3282或Device Engineering公司的DEI1016。但在此则极不经济,完成多通道429通信,需要多个芯片和更多的布板空间,功耗也线性增加。

特别地,传统的多通道的429需要更加多的CPU中断请求线,需要外部复杂的逻辑设计。TS68C429A则是目前解决多通道429通信最为有效的途径。和传统的“两收一发”的芯片相比较,它是“八收三发”,“一片顶四片”。

2 TS68C429A的主要特征

ATMEL公司的TS68C429A是高性能、多通道、低功耗的CMOS型429接口,亦能满足类似的时分多路串行数据通信。

整个芯片只需单5V工作电源。它具有8路接收、3路发送。所有的接收通道和发送通道都是彼此互独立,可同时并行工作。8个接收通道之间也是独立的并行接收,可以直接连接到ARINC429总线,而不需电平转换。数据字长是标准的32-bit,25-bit的并不支持。

主要特征有如下几点:

8个独立的接收通道;3个独立的发送通道;和所有的TS68K系列的微处理器接口兼容;16-bit数据总线;符合ARINC2429接口,归零制编码(Return Zero Code);支持所有的ARINC429数据传输率,最高可达2.5Mbit/s,传统的ARINC429芯片的速率只有2种可选;多标号能力,传统的芯片要么不检查标号,要么就接收一个指定的标号;校验控制(奇校验、偶校验、无校验,中断能力);RX、TX的数据率可独立编程;每个发送通道有8个信息单元的FIFO;向量式中断;可组成菊花链中断;所有的寄存器都是可直接寻址的;具有自测试能力;工作频率为20MHz;低功耗:400mW。

3 硬件设计

TS68C429A接收和发送通道都成倍增加,但毕竟不是通道的简单叠加,不是传统接口的线性扩展,在相关器件选型和设计中需要仔细推敲。

3.1 基本硬件接口

基本硬件接口就是和嵌入式CPU的接口电路。根据ARINC429数据特点,至少要选16-bk数据总线以上的CPU。TS68C429A和所有的TS68K系列的CPU接口兼容,像TS68000、TS68020都可以只需要增加非常简单的接口逻辑。特别是TS68302完伞可以“无缝连接”。无缝连接就是两个复杂芯片不需要“粘合逻辑”,对应信号直接相连。

在设计基本电路时需要注意以下几点:

3.1.1 嵌入式CPU选型。

CPU的数据总线至少应该是16bit的,否则在硬件上要增加字节转发电路,设计复杂度上升。如果在中断响应时想迅速判断中断源,CPU存中断响应时应该能够发出中断响应(IACK)信号,由TS68C429输出中断向量,由CPU回读后硬件判断,直接进入对应中断服务例程,节省软件响应时间。除TS68K系列外,符合这个要求的还有最广泛使用在PC机上的X86系列,如Inte180486等。显然,TS68C429的中断响应机制,完全类似X86系列中的8259 中断控制器时序,可以直接无缝连接。值得指出的是,X86系列的中断请求是高有效,中断请求信号需要反相。

3.1.2 时钟

传统的ARINC429芯片只有一个时钟,人多数是1MHz,用以控制收发速率。速率有2种选择,即速率是时钟的十分之一或八十分之一,亦即100K或12.5K。在这里,TS68C429需要2种时钟,系统时钟和ARINC429收发时钟。系统时钟CLKSYS用来控制CPU接口时序,应该和CPU时钟相同,在这里直接使用TS68302的输出时钟CLK0。在使用其它型号的CPU时,CLKSYS可以直接和CPU时钟连接在一起。CLK429使用了定时器输出TOUT1,用来决定429串行数据传输速率。存使用其它型号的CPU时,也可以设计一个独立的时钟做CLK429。

3.1.3 高、低字节访问

处理器对TS68C429每次访问都应该是16Bit的,除了这里和TS68302的无缝连接,还可以把高字节选通信号(/UDS)和低字节选通信号(/LDS)一起直接接地。CPU一般足字节编址的,所以应该足A9…A1对应TS68C429的A8…A0。

3.1.4 存储器周期

无论是读周期还是写周期,TS68C429都要用/DTACK应答CPU。TS68K系列中的/DTACK,即数据传输周期应答(Data Transfer Acknowledge),本质上就是许多CPU的READY信号。如果使用别的型号CPU,READY属于高有效,需要对/DTACK进行反相。

3.2 中断菊花链电路

对于大多数应用来讲,一片TS68C429基本可以满足多通道429通信要求。当要求更多通道时,TS68C429A可以采用菊花链的彤式设计。

菊花链(Daisy Chain)是一种阻塞式级联结构,排在前面的优先级高于其后的所有单元。在任一时刻,高优先级若果发出中断,就禁止了比它自身优先级低的中断。共有U1、U2…Un个单元,其中U1具有最高优先级,Un优先级最低。当某一单元需要发出中断时,首先要判断前面是否有高优先级的中断,即判断传递下来的中断使能信号/IEIxx,当其为低电平时,可以发出,当其为高电平时禁止发出。禁止中断发出时,要一直等待到前面中断响应完成后再发出。最极端的情况就是,某些低优先级的中断单元永远没有机会发出中断,设计菊花链电路时,要综合平衡各通道的数据流量。

4 软件设计

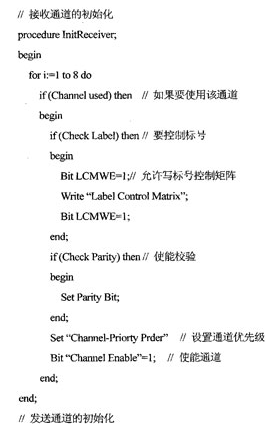

上电复位后,软件应在正式工作前初始化TS68C429。传统的芯片只需要要写一次控制寄存器,但多通道的初始化要复杂一些。

4.1 寄存器映像

在传统的ARINC429只有一个控制寄存器,由于通道少,每个通道分配专用的选通信号,硬件简单译码即可。在多通道的芯片中,不可能继续采用这种办法。整个芯片只有一个总的片选(/CS),然后由地址A8..A0来寻址片内寄存器。系统的初始化,本质就是正确配置这些寄存器。

8个接收通道,每个都有自己的4类专用寄存器区。

4.1.1 接收控制寄存器(receive control register)

这是一个可读可写的寄存器,它控制本通道的中断优先级、校验、标号、测试模式以及通道使能等配置。如果有2个通道的中断优先级相同,就有一个永远发不出中断。如果设置本通道处于测试模式,则第三发送通道的数据在内部回环到本通道。这个特征是用来做通道自检的。

4.1.2 间隙寄存器(gap register)

间隙寄存器是一个只写寄存器。写入值是以CLK429时钟周期为单位的计数值,实际是定义了相邻两个429数据的最小间隙。在传统的芯片中,最小间隙是固定的。在这里,必须显式地设置这个寄存器,决不能隐含使用复位缺省值。

4.1.3 数据缓冲区(message buffer)

数据缓冲区是2个16bit的只读寄存器,存放接收到的ARINCA29数据。采用中断接收时,主要就是读这2个寄存器。高16bit(most significant word,MSW)存放在低地址,低16bit(least significant word,LSW)存放在高地址。读数据时先读MSW,再读LSW。

4.1.4 标号控制矩阵(label Control matrix)

这是一个256×1bit的存储器区。许多人不理解这个区的含义,不会配置,以致系统不能正确运行。众所周知,ARINC429规范的低8bit属于标号区(label),标号代表了数据类型,例如72H代表高度数据,73H代表角速度等。这样总计有256个标号。标号控制矩阵的某地址设置为“1”,就允许该通道接收对应标号的数据,清除为“0”,就禁止该标号的数据。硬件复位之后全部清“0”,也就是禁止接收一切数据,这就是系统不运行的原因。

3个发送通道,每个都有自己的3个专用寄存器。

4.1.5 频率寄存器(Frequency Register)

这是一个只写的寄存器,写入值是发送速率的除数因子。

发送速率=CLK429/FR除数因子

根据这个公式,用户可设定选择的速率。传统的ARINC429没有这个功能,只有2种固定的速率。

4.1.6 发送控制寄存器(Transmitter Control Register)

和接收控制寄存器类似,这是一个可读可写的寄存器,它控制本通道的中断优先级、校验、是否作为测试模式的发送、以及通道使能等配置。其中的发送间隙是控制连续发送的两个32bit的AKINC429信息之间最小间隙,防止接收方覆盖溢出。

4.1.7 发送FIFO

FIFO,即“先进先出”(First In First Out),基本元素可以认为是2个16bit的寄存器。软件必须先写入MSW,再写入LSW,这和接收通道顺序是一致的。FIFO深度为8个ARINC429信息。存写入之前,必须验证FIFO未满,否则写入数据被丢弃。在FIFO只要满队列的FIFO发送了一个元素,此时FIFO虽然未空,但也未满,就可以写入后一个数据。

除了接收通道和发送通道的专用寄存器,还有儿个通用的寄存器,如通道状态寄存器、中断屏蔽寄存器,中断向量基址寄存器等,不再赘述。

4.2 复位初始化

上电复位之后,所有寄存器清“0”,各通道处于禁止状态,需要软件显式初始化。下面给出接收通道和发送通道的初始化流程。

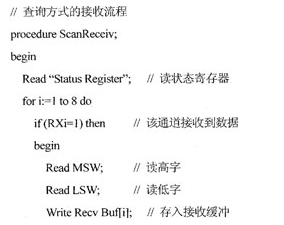

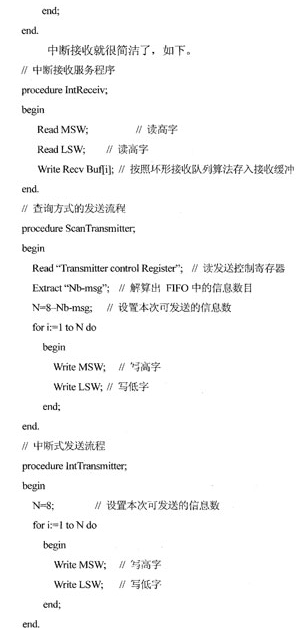

4.3 ARINC429数据的接收与发送

系统工作后,初始化的通道就可以接收发送了。一般的,因为不可预测接收数据何时到达,正式工作后接收采用中断驱动,发送采用查询,这样既可以不丢失数据,又可以掌控发送节奏。查询接收的办法,一股使崩在系统初期硬件调试阶段。在上篇文章中,介绍了中断采用环形接收队列,这个方法非常有效。在此不再赘述环形队列访问算法。下而给出查询/中断收发流程。

TS68C429集成度高,是改装原来分散的ARINC429设备的一种合理有效的选择。我们已将上述设计应用在多个不同种类的航空电子系统中,证明是十分有效的。随着航空电子系统的更新换代,TS68C429的应用将更加广泛。

责任编辑:gt

-

CMOS

+关注

关注

58文章

6186浏览量

241574 -

显示器

+关注

关注

22文章

5130浏览量

143639 -

接口

+关注

关注

33文章

9444浏览量

156136

发布评论请先 登录

基于USB的ARINC429总线接口模块设计

基于PC/104设计与实现ARINC429接口模块

怎么设计便携式ARINC429总线通信设备?

基于DSP的ARINC429通信板设计

航空用ARINC429总线收发系统设计与实现

基于USB的ARINC429总线接口模块设计

基于HI-8582的ARINC429总线设计

USB的便携式ARINC429总线通信设备技术

PCI总线ARINC429通信卡实现方法

一种PCI总线ARINC429通信卡实现方法

如何使用FPGA实现ARINC429接口和总线数据接收

arinc429模块卡

基于CMOS型429接口TS68C429A实现ARINC429通信的应用设计

基于CMOS型429接口TS68C429A实现ARINC429通信的应用设计

评论