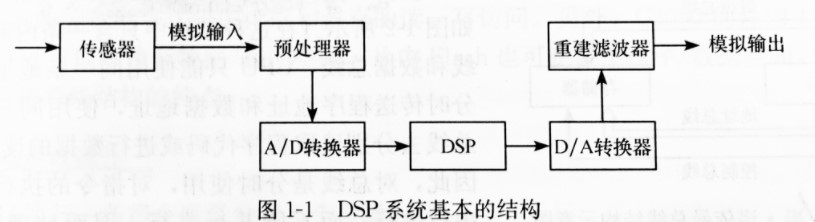

软件无线电是利用大规模集成电路技术,把DSP芯片或通用CPU芯片作为无线通信的基本硬件平台,将尽可能多的无线通信功能(如调制技术、跳频、纠错及加密等)用软件实现。软件无线电技术可以用软件升级来改变无线功能参数,可以按要求的条件编程实现无线通信功能,使系统升级基于软件,其代价小,灵活性强。用TI公司的TMS320C5420DSP芯片成功设计出一种兼容2FSK,DPSK,QAM等多种调制解调方式的JH5001通信原理实验系统,下面以 2FSK为例,详细介绍用DSP软件实现他的原理。

2FSK调制的DSP软件实现

2FSK调制的数字振荡器设计

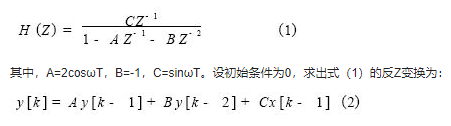

频移键控FSK调制是用数字基带信号来控制高频载波频率的变化,调制后的载波信号频率代表了要传送的数字信号。二进制FSK(2FSK)是用2个高频载波f1和f2来表示2个数字信号“1”或“0”。2FSK调制的常用方法是将f1和f2的正弦值预先计算出来,制成一个表,DSP工作时仅做查表运算即可实现。在这里采用数字振荡器方法,用迭代方法产生正弦信号。其原理如下:一个传递函数为正弦序列sinkωT的Z变换为:

这是一个二阶差分方程,对其求单位冲击响应便可得到正弦信号sinkXT。利用单位冲击函数x[k-1]的性质,仅当k=1时,x[k-1]=1,得到下列递推式:

k=0时y[0]=Ay[-1]+By[-2]+0=0

k=1时y[1]=Ay[0]+By[-1]+C=C

k=2时y[2]=Ay[1]+By[0]+0=Ay[1]

k=3时y[3]=Ay[2]+By[1]

……

k=n时y[n]=Ay[n-1]+By[n-2]

在k》2以后,y[k]能用y[k-1]和y[k-2]计算出来,这样通过迭代就能得到一系列的y[k]值。所设计的数字振荡器产生16kHz和 32kHz的正弦信号,分别代表数据0和1,设置采样频率为96kHz,通过确定上面递归差分方程系数就可求得16kHz和32kHz正弦信号的系数(下标为0的系数是16kHz正弦信号的系数,下标为1的系数是32kHz正弦信号的系数)。

A0=2cosω0T=2cos(2π×16000/96000)=1

B0=-1

C0=sinω0T=sin(2π×16000/96000)=0.86602540

A1=2cosω1T=2cos(2π×32000/96000)=-1

B1=-1

C1=sinω1T=sin(2π×32000?96000)=0.86602540

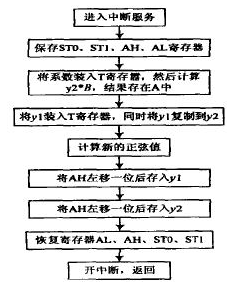

DSP程序在初始化时先分别计算出产生16kHz与32kHz信号所需要的y[1]和y[2]值,然后开放定时器中断,以后每次进入定时器中断服务程序时,利用已计算出的y[1]和y[2]值重新计算出新的y[0]值,对其求单位冲击响应就可得到16kHz和32kHz的正弦信号。

2FSK调制的定时与中断设计

为了保证96kHz的采样频率,需要用到TMS320C5420的中断与定时器。定时器主要由3个寄存器组成,分别是定时器寄存器TIM,每计数一次自动减1;定时器周期寄存器PRD,当TIM减为0后,CPU自动将PRD的值装入TIM;定时器控制寄存器TCR。

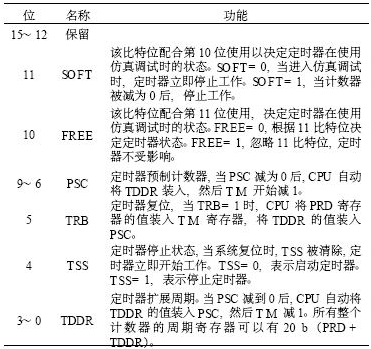

定时器控制寄存器TCR各个比特位的具体定义如表1所示。

表1定时器控制寄存器TCR的定义

TMS320C5420的定时器工作原理是:当CLKOUT信号时钟沿到来时,触发PSC。PSC是一个减1计数器,CLKOUT信号时钟沿使PSC减 1,直到PSC为0,然后用TDDR重新装入PSC,同时将TIM减1,直到TIM减为0,这时CPU发出TINT中断,同时在TOUT引脚输出一个脉冲信号,脉冲宽度与CLKOUT一致,然后用PRD重新装入,重复下去直到系统或定时器复位。

当系统复位或定时器单独复位时,TIM和PRD都置成最大值FFFH,TDDR位清0,定时器控制寄存器的停止状态位TSS被清零,定时器启动,并将定时器扩展周期TDDR中的值加载到定时器预置计数器PSC中,而且将定时器周期寄存器PRD中的值重新加载到定时器寄存器TIM中。

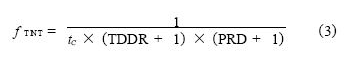

定时器中断的频率由式(3)决定:

其中,tC表示CLKOUT的周期,即TINT=95kHz。由式(3)可确定定时时间常数TDDR=0,PRD=333。

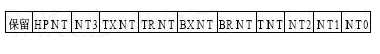

TMS320C5420的中断是通过中断屏蔽寄存器IMR来实现的。IMR是一个存储器映射寄存器,用于控制中断源的屏蔽和开放。当ST1寄存器中的INTM位为0时,全局中断允许。IMR中的某一位为1时,该中断开放。以下是IMR寄存器各个比特位的定义:

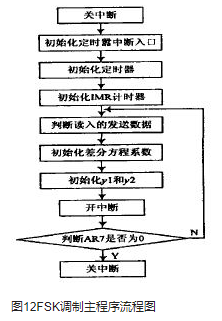

其中,HPINT表示HPI接口中断,INT3~INT0为外部引脚产生的中断;TXINT和TRINT为TDM串口的发送和接收中断;BXINT和BRINT为BSP串口的发送和接收中断;TINT为定时器中断。图1为 2FSK调制主程序流程图,图2为中断程序流程图。按图1和图2的流程编制程序即可实现2FSK调制功能。

图2中断程序流程图

2FSK解调的DSP软件实现

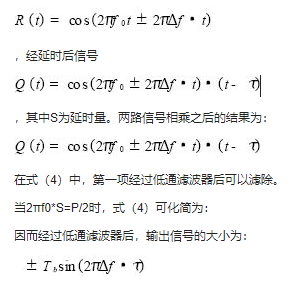

2FSK解调的方法有相干解调、滤波非相干解调、正交相乘非相干解调等多种方法,这里采用正交相乘非相干解调法。 输入信号为

,从而实现了FSK的正交相乘非相干解调。

从以上的分析可以看出,正交相乘非相干解调法关键在于正确选择τ。这里2FSK的采样率96kHz,每一个比特采样16个样点,基带信号的载频f0为24kHz,频偏量$f为8kHz。因而在DSP的处理过程中,延时取一个样值就可满足cos(2πf0*τ)=0的条件,从而保证信号通过低通滤波器后的值为±Tbsin(2π△f*τ)。当基带信号为1时,滤波后得到一个正值;当基带信号为0时,滤波后得到一个负值,最后判决时就可根据滤波后值的正负判断。

正交相乘非相干解调的另一个关键问题是低通滤波器的实现。为了将二倍频分量cos[4π(f0±△f)

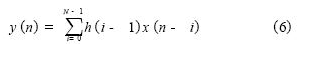

*t-2π(f0±△f)*τ]去除,需要将相乘后的值通过一个低通滤波器,留下cos2π(f0±△f)*τ]。为此设计了一个51阶FIR滤波器,采用汉明窗平方根升余弦滚降。FIR滤波器的差分表达式为:

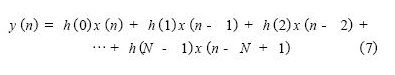

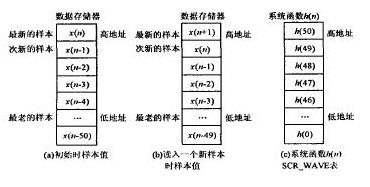

FIR滤波器没有反馈回路,是一个无条件的稳定系统。他的单位脉冲响应h(n)是一个有限长序列,当h(n)满足偶对称或奇对称,并且h(n)是一个实数序列时,FIR滤波器具有线性相位的特性。通过对FIR滤波器的结构和他的差分方程分析,可以看出FIR滤波器实际上是一种乘法累加运算,对不同时刻的输入乘以其加权系数,然后各项相加,不断地移位输出,这样就得到了滤波输出结果。将式(6)展开即得:

由此式可见,将最新的样本与h(0)相乘,次新的样本与h(1)相乘,依次类推,最老的样本与h(N-1)相乘,然后将这51个乘积相加就得到一个y (n)。然后又读入一个新样本,则原来最新的样本变为次新的样本,原来最老的样本则被淘汰。此法的示意图如图4所示。

图4FIR实现示意图

在编程时,将最新的x(n)的地址给AR4,51阶的h(x)放在SCR_WAVE表中。计算时,AR4递减,且将AR4地址的值与SCR_WAVE逐个相乘,这样就实现了上述设计思想。

结语

基于DSP实现的2FSK调制解调器在JH5001通信实验系统中得到成功的应用,在系统硬件不变的情况下只要修改DSP的软件处理部分就能实现无线参数的改变和增加新的功能,因此软件无线电技术灵活性很强,他将有着更广泛的应用前景。

责任编辑:gt

-

处理器

+关注

关注

68文章

18252浏览量

222079 -

dsp

+关注

关注

544文章

7681浏览量

344328 -

芯片

+关注

关注

446文章

47750浏览量

409043

发布评论请先 登录

相关推荐

数字信号处理器(DSP)简介

数字信号处理器DSP技术入门(附送算法设计与系统方案)

基于数字信号处理器TMS320F2812的逆变电路设计

利用FPGA怎么实现数字信号处理?

数字信号处理器的特点

数字信号处理器(DSP)

Builder数字信号处理器的FPGA设计

基于数字信号处理器实现JH5001通信原理实验系统的设计

基于数字信号处理器实现JH5001通信原理实验系统的设计

评论