1 概述

软硬件协同验证的概念已经提出多年,但是直到这些年随着SOC技术的发展,软硬件协同验证技术才得到更多的关注和重视,并得到发展。软硬件协同验证是一种在硬件流片封装之前,验证SOC系统硬件和软件是否能够正确工作的技术。协同验证又可以叫作虚拟原型技术,因为硬件部分的仿真虽然跟真实硬件的运行基本一样,但是硬件仿真其实是通过在工作站上的一个软件程序的运行来实现的。协同验证的基本框架如图1所示。

对比传统的验证方法,协同验证技术使得软件设计工程师能够在设计早期进行调试,可以较早的进行软硬件的整合,缩短上市时问(time-to-market)。另一方面,通过软硬件协同验证,可以为硬件设计工程师提供了一整套非常接近于现实的激励集,有利用于提高验证的质量。

协同验证系统由一个硬件执行环境和一个软件执行环境组成,通过事件和命令,使用一些机制,在这两个环境间进行控制。软件的执行环境用于产生总线周期的序列,协同验证工具将总线周期转换成许多信号事件或者命令集,并驱动这些信号事件命令进入硬件执行环境,然后对总线周期响应进行硬件环境取样,这一响应又被传送回软件环境。同时,保持硬件及软件环境问的同步以便硬件或软件环境都可发现由于错失响应而导致有误的情形。

软硬件协同验证中,软硬件部分都是通过建模的方式实现。其中硬件建模方式有如下几种:采用FPGA原型或模拟系统;采用HDL及逻辑仿真器;采用高级程序语言(如C/C++语言)编写的行为模型。软件也可通过几种方式执行:采用ISS(指令集仿真器)在CPU上运行;通过编译,并在运行仿真程序的主机上运行。在一般的SOC设计中,硬件建模一般用硬件描述语言来实现,软件一般需要编译成针对SOC硬件嵌入式核的目标代码,因此在本文中,将采用指令级模拟器加逻辑仿真器(ISS with logicsimulator)的方法来构建协同验证环境。

2 进程间通信

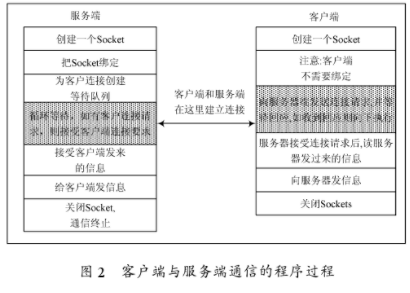

软硬件仿真器之间的通信是协同验证中的关键技术。由于软件仿真和硬件仿真使用独立的两个进程,因此可以使用Unix下的进程间通信(Inter Process Communication,IPC)技术来实现软硬件仿真器之间的信息交互。常用的几种Unix IPC有无名管道,有名管道(FIFO)和Unix套接字(Socket)。无名管道是Unix中最常用的IPC方式,优点是非常简洁,弱点是他只能在相关的,有共同祖先的进程间使用;有名管道(FIFO)和无名管道的区别在于他是持久稳定的,而且可以让无任何关联的进程问交换数据;套接字是一种抽象数据结构,用以创建一条在没有关联的进程间发送、接收消息的通道(连接点),一旦通道建立之后,被连接起来的进程就可以通过普通的文件系统存取例程来进行通信了。在通信的两方中,一方称为客户程序(client),另一方称为服务程序(server)。建立过程如图2所示。对比上述3种通信方式的特点,这里使用UnixSocket来实现两个进程间的通信。

3 消息传递

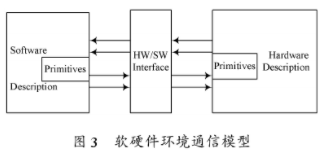

在本环境中,软硬件间的通信可以看作是一个消息传递的过程,在软件环境和硬件环境中添加数据传输函数,并通过接口实现信息交互,如图3所示。

在两个进程消息传递的过程中,消息可以分为3类:同步的数据传输;异步的数据传输;无数据传输的同步信号。同步的数据传输是指在一种机制下,保证在发送端进程发送数据时,接收端进程处在正确的状态;如果发送端进程发起一次数据传输时,接收端不处在合适的状态,发送端则阻塞这次传输直到接收端准备好。异步的数据传输是指发送端进程在发送数据时,不考虑这次数据或者前一次的数据是否被接收端接收到,数据没有缓冲,每次新发送的数据都会覆盖前一次的数据,因此,在一次传输中,数据可能被接收多次或者接收不到。通常这种传输用来传递状态信息。无数据传输的同步信号,用来同步两个进程的状态,没有数据的交换。一个进程可使用同步信号来通知另外一个进程开始一次任务或者等待其完成一次任务。

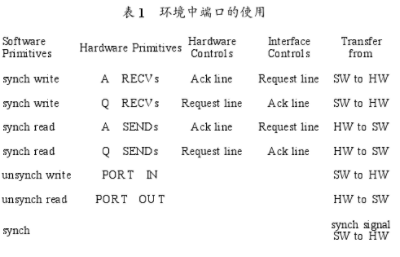

软件环境和硬件环境中数据传输函数与接口间的通信方式是不同的。在软件环境中,数据传输函数只包括简单的读写操作,读写操作分为同步和异步两种模式。在硬件环境中,需要定义一些端口来控制数据传输,每一个端口使用不同的协议。进行同步数据传输时,在硬件环境中使用握手端口,同时与软件环境中的同步读写函数配合。握手端口共有4个,分为两个SENDs(数据从硬件环境到接口)和两个RECVs(数据从接口到硬件环境)。每个SENDs,RECVs又根据硬件环境是请求方还是应答方分为Q_SENDs,Q_RECVs和A_SENDs,A_RECVs。进行异步的数据传输时,在硬件环境中定义两个端口PORT_IN和PORT_OUT,与软件环境中的异步读写函数配合进行传输。另外,需要定义一个EVENT端口,发送无数据传输的同步信号,用来同步软件环境和硬件环境的仿真时间。

表1中总结了在接口中端口的使用。在这个协同验证环境中,通过这些端口的使用,设计者可以忽略底层细节,有选择的使用以上端口来实现软硬件之间信息交互。

4 协同验证环境的实现

4.1 基本构架

整个环境的基本构架如图4所示,左右两个框分别表示软件仿真进程和硬件仿真进程,他们之间通过UnixSockets交换信息,Verilog PLI是他们交互的接口。下面对环境的各个部分进行介绍。

在软件环境中,指令级模拟器(ISS)是一种仿真CPU行为的程序,他在主机上运行,可以仿真软件程序的可执行镜像。把SOC软件编译成针对SOC硬件嵌入式核的目标代码后,即可在指令级模拟器上仿真。C的总线模型(C BFM)用来实现指令级到周期级的转换,并实现总线接口功能,与硬件环境相连接,同时还包含了Unix Sockets的服务程序。

硬件环境包含2部分。一部分是Verilog PLI Inter-face。他是软件和硬件交互的接口,一方面通过UnixSockets的客户程序与软件环境交互信息;一方面通过一些任务函数,根据Sockets传递过来的信息,向硬件发出请求或者应答信号。另一部分是待验证的硬件模型,用Ver-ilog描述,他的外围是一段控制程序(verilog controlstub),在仿真的每一个时刻调用PLI中的函数,通过端口与Verilog PLI Interface交互信息。

4.2 功能实现

图5给出了软硬件环境通过A_RECV端口实现通信的例子。

当软件需要向硬件写入一个数据时,首先通过Socket将数据发送给PLI;PLI接收数据,同时拉高请求线,向硬件发出请求;硬件模型得到清求后,通过Verilog ControlStub接收数据,传递给内部寄存器,并拉高应答线,向PLI发出应答。PLI得到应答后拉低请求线,同时发出同步信号给Socket,硬件模型得到拉低的请求后,拉低应答线,一次传输结束。当软件需要进行下一次写操作时,首先需要通过Socket读取同步信号,有同步信号时即可开始下一次操作。其他的端口握手过程与此类似。

4.3 协同模拟同步

指令集模拟器以指令为单位进行模拟,时钟每次推进一个指令周期,指令周期长度则随指令的不同而不同。硬件模拟器通常采用事件驱动模拟算法,他以事件为调度对象,硬件模拟器按照事件发生的时间进度推进时钟,时间单位一般由用户的设计指定,例如纳秒,微秒等。因此必须采用一定的机制对二者进行同步,并且他们之间能否同步将直接影响到协同模拟的正确性。指令集模拟器和硬件模拟器之间通常采用Lock-step方式进行同步。采用该同步方式必须首先确定同步点,保证在两个同步点之间的时间间隔内不发生软硬件交互事件。如前文所述,Verilog PLIInterface是软硬件模拟器之间的信息交换界面,所以同步点会因为交互信息的不问而不同。而硬件模拟器是以事件发生的时间顺序推进时钟,要保证其时钟不会越过同步点,就必须引入同步信号,即时间为同步点的信号,硬件模拟器完成一个事件后,需要向Verilog PLI Interface发回一个同步信息,说明硬件模拟器的时钟己推进到同步点。

5 结 语

设计验证是SOC设计的关键技术之一,贯穿整个SOC技术,随着SOC技术的发展,软硬件协同验证技术得到了更多的关注和重视。与过去把整个环境当作单一的一个进程处理的方法不同,本环境将软硬件仿真的过程分离开来,使用Unix Sockets来实现软硬件之间的通信,更接近实际情况。同时,由于两个仿真过程并行执行,仿真速度更快,效率更高。在该环境中,软件用编程语言来编写,硬件用硬件描述语言来建模,符合一般软硬件工程师的习惯,较早的进行软硬件的整合。在此环境中,软硬件之间通信的吞吐量是影响仿真速度的瓶颈,下一步作者将针对协同模拟同步及优化进行研究。

责任编辑:gt

-

FPGA

+关注

关注

1602文章

21307浏览量

593113 -

仿真器

+关注

关注

14文章

988浏览量

82987 -

模拟器

+关注

关注

2文章

816浏览量

42695

发布评论请先 登录

相关推荐

基于指令级模拟器加逻辑仿真器实现协同验证环境的搭建

基于指令级模拟器加逻辑仿真器实现协同验证环境的搭建

评论