引 言

1 概 述

SCC2619是Philips公司推出的高集成、低能耗的全双工通用异步收发器 UART。该芯片的接收与发送速度可以分别定义,接收器采用三倍缓冲方式,在中断驱动系统中大大减少了CPU处理中断的次数。SCC2691在收、发双方之间提供了一种握手方式,当接收方的缓冲区已满时,能自动使远程发送方的发送失效。除此之外,SCC2691还具有以下特性:

△可编程的数据格式为5~8位数据位;可选择的奇偶校验位;可编程的停止位。

△16位可编程的计数器/定时器。

△收发器的波特率可分别按以下方式定义:从50~115.2K共18种固定的波特率;由计数器/定时器驱动的非标准自定义的波特率;外部时钟的1倍或16倍频。

△奇偶校验、帧错误、溢出错误检测。

△可编程的通道方式。

△7个中断源,但同时仅有一种中断输出。

2 引脚定义

SCC2691采用SO、PLCC、DIP等形式封装。主要引脚功能定义如下:

D0~D7:数据总线。在CPU和UART之间所有的数据、命令、状态信息等都是通过数据总线进行传递的。在CEN信号是有效低电平时,发送的方向由WRN和RDN两个读写控制决定;当CEN为高电平时,数据总线三态。

CEN:芯片使能引脚,低电平有效。低电平使能时,在CPU与UART之间通过D0~D7传递的数据受WRN、RDN和A0~A2等引脚控制;高电平时,使UART与CPU隔离。

WRN:写选通,低电平有效。当CEN为低电平时,WRN上的低电平使数据总线D0~D7上的数据被送往由地址A0~A2选中的寄存器中。

RDN:读选通,低电平有效。当CEN为低电平时,RDN上的低电平将被地址A0~A2选中的寄存器的内容送往数据总线D0~D7。

A0~A2:地址输入端。选择执行读写操作的UART寄存器。

RESET:复位输入端,高电平有效。复位时将清除UART中的状态寄存器(SR)、中断屏蔽寄存器(IMR)、中断状态寄存器(ISR),设置方式指针指向方式寄存器1(MR1),使发送和接收失效,并且引脚TxD置为高电平。

INTRN:中断请求输出端,低电平有效。可从七个中断源中选择一个作为UART的中断输出。CPU可以读中断状态寄存器(ISR),以判断七个中断源的状态。该引脚是漏极开路输出,需要接上拉电阻。

X1/CLK:晶体连接或外部时钟输入端。通常采用3.6864MHz的晶体。

X2:晶体连接端。若未连接晶体,最好使该引脚悬空。

RxD:串行数据输入端。

TxD:串行数据输出端。当发送器空闲、不使能或者UART工作在本地循环状态下,该引脚输出高电平。

MPO:多功能输出端。通过对辅助控制寄存器(ACR)进行编程,可以选择以下8种功能作为该引脚的输出。

① RTSN:请求发送,低电平有效。可通过编程命令寄存器(CR)使该引脚使能,也可以设置方式寄存器(MR),当发送方结束发送或接收方的接收缓冲区已满时自动复位。

② C/TO:计数/定时器输出。

③ TxC1X:发送器频率的1倍频输出。

④ TxC16X:发送器频率的16倍频输出。

⑤ RxC1X:接收器频率的1倍频输出。

⑥ RxC16X:接收器频率的16倍频输出。

⑦ TxRDY:表示发送器保存寄存器(THR)空。低电平有效(漏极开路输出)。

⑧ RxRDY/FFULL:标识接收器缓冲区非空或已满。低电平有效(漏极开路输出)。

MPI:多功能输入引脚。该引脚可定义为以下3种功能:

① GPI:通用引脚。该引脚上的跳变或电平状态可以作为中断源反映到中断状态寄存器(ISR)的相应位。

② CTCLK:计数器/定时器的外部输入时钟。

③ RTCLK:接收器或发送器的外部时钟输入。设置时钟选择寄存器(CSR)可选择输入的1倍频或16倍频作为接收和发送的频率。

3 主要功能

(1)中断控制

以下内部事件的发生可以使能中断输出引脚(INTRN):发送保持寄存器(THR)准备好;发送转移寄存器(TSR)空;接收保持寄存器(RHR)准备好或已满;接收到break信号的开始或结束;计数器达到定义的计数值;MPI端脚的跳变;MPI端脚的电平状态。

与中断控制相关的寄存器是中断屏蔽寄存器(IMR)和中断状态寄存器(ISR)。IMR用于从以上七个中断源中选择一种作为触发INTRN的条件。CPU可以读取ISR来获得所有中断源的状态。ISR不受IMR的影响。

(2)操作控制

UART的控制逻辑单元接收来自CPU的命令生成相应的信号来支配内部各器件进行操作。控制逻辑单元通过地址译码和读写控制使CPU与UART相互通信。地址译码与读写控制之间的关系见表1。

表1 寄存器地址表

方式寄存器1(MR1)和方式寄存器2(MR2)通过一个辅助指针来访问。当上电复位或通过命令寄存器(CR)执行复位命令时,指针指向MR1,以后对MR1的任何读写操作都使指针指向MR2,并一直指向MR2,直到再次执行复位命令。

(3)计数器/定时器

计数器/定时器的工作方式和输入时钟源的选择,可以通过编程辅助控制寄存器(ACR)从八种方式中选择。计数器/定时器的输出可以设置为多功能输出口MPO,定时器的输出也可以作为生成波特率的选择之一。

① 定时方式:定时器的输出是一个方波,其周期是寄存器CTUR和CTLR中值的2倍。定时器溢出时,中断状态寄存器(ISR)中的计数器准备好(counter ready)置位。当发布一个中断计数器命令时,定时器不会终止,仅影响ISR中的counter ready位。当接收到一个开始计数/定时器命令时,定时器会终止当前的操作,以新的CTUR和CTLR开始一个定时周期。

② 计数方式:计数器接收到开始计数命令后,将计数值送入CTU和CTL。当计数值达到预定的存入CTUR和CTLR中的值时,ISR中的counter ready位置1,计数操作不会停止,直到接收到结束计数命令为止。CPU可以在任何时候设置寄存器CTUR和CTLR,但是该值仅有当结束本次计数并开始下一次计数命令时才有效。

(4)接收和发送

发送器接收来自CPU的并行数据,将其转换为串行数据流送往TxD端口,串行数据流被以一个开始位、可编程个数的数据位、可选择的奇偶校验位和可编程个数的停止位的组合形式发送出去。发送结束后,若没有新的数据被送往发送保持寄存器(THR),则TxD端脚保持高电平,并且状态寄存器(SR)中的位TxEMT置1。当CPU将一个新的数据送往THR后,TxEMT位清零,发送操作继续。发布一个开始break命令,可以使发送器发送一个break信号(持续的低电平)。发送器接收到一个终止发送的命令时,若其正在发送数据或THR中仍有数据,发送器会继续发送直到THR为空截止。

接收器从RxD引脚接收串行数据,检测其开始位、奇偶校验位、终止位,若有错误则设置状态寄存器(SR)中的相应位。接收器将数据送往接收保持寄存器(RHR),等待CPU以查询方式或以中断方式读取数据,并且将SR中的RxRDY和中断状态寄存器(ISR)的RxRDY位置1。

接收保持寄存器(RHR)是一个可容纳3个字符的先进先出队列(FIFO)。接收器将从 RxD接收到的数据送往FIFO的开始位置,并将SR中的RxRDY置1。RxRDY=1,表示FIFO中有接收字符;而FFULL=1,表示FIFO已满。在方式寄存器1(MR1)中,可以选择RxRDY或FFULL作为接收中断源。读RHR可以将其中的数据连同在SR中的相应状态位一起从FIFO中弹出。

4 寄存器

寄存器是CPU与UART之间进行操作的桥梁。CPU通过编程寄存器来支配UART操作,另外,各种状态寄存器的变化也体现了命令的执行结果。

5 应 用

(1)硬件电路

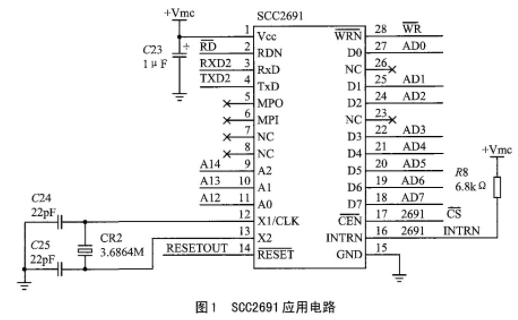

图1是使用SCC2691设计的扩展串口电路。其中AD0~AD7接CPU(亿恒 C164CI)数据总线;A12~A14与CPU地址线相连;、分别与CPU的读写信号相连;RESET接CPU的RESETOUT;2691_CS是 SCC2691的片选信号;INTRN接CPU的中断输入端。

(2)测试程序

测试程序采用Tasking C集成环境开发,具体程序见网络补充版。

责任编辑:gt

-

收发器

+关注

关注

10文章

2965浏览量

104706 -

封装

+关注

关注

123文章

7236浏览量

141025 -

定时器

+关注

关注

23文章

3144浏览量

112004

发布评论请先 登录

相关推荐

通用异步收发器有什么功能?

通用同步异步收发器(USART)

UART通用同步异步收发器的相关资料分享

USART通用同步异步收发器介绍

USART通用同步异步收发器介绍

具有±80V故障保护的全双工RS-485收发器,省去了外部保

USART全双工通用同步异步串行接口收发模块的C语言程序免费下载

全双工通用异步收发器SCC2619的性能特性、功能及应用

全双工通用异步收发器SCC2619的性能特性、功能及应用

评论