引言:晶振是数字电路设计中非常重要的器件,时钟的相位噪声、频率稳定性等特性对产品性能影响很大。本文基于可编程晶振SI570,就Xilinx FPGA收发器输入参考时钟的硬件设计及FPGA软件设计给出设计案例,供大家参考。通过本文,可以了解到:

Xilinx FPGA收发器参考时钟设计要点

可编程晶振SI570设计方法

1.Xilinx FPGA收发器参考时钟设计要求

1.1参考时钟接口要求

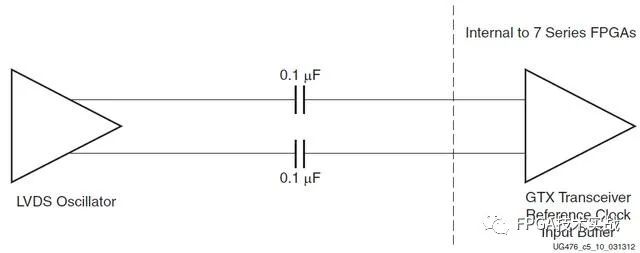

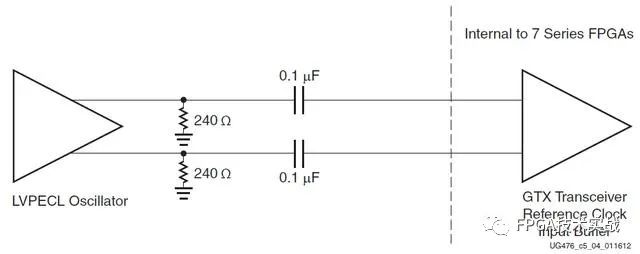

FPGA收发器GTX/GTH参考时钟接口提供两种连接方式:LVDS(如图1所示)和LVPECL(如图2所示)。我们在选择晶振时,至少要支持其中一种接口输出电平标准。图2所示的电阻值为一般推荐值,实际偏置电阻值需要参考晶振手册。图1和图2中交流AC耦合电容作用:1)阻断外部晶振和GTX/GTH收发器Quad专用时钟输入管脚之间的DC电流,降低功耗;2)AC耦合电容和参考时钟输入端接构成高通滤波器,衰减参考时钟偏移;3)保持耦合电容两侧共模电压独立,互不干扰。

图1、LVDS晶振和7系列FPGA收发器参考时钟输入接口

图2、LVPECL晶振和7系列FPGA收发器参考时钟输入接口

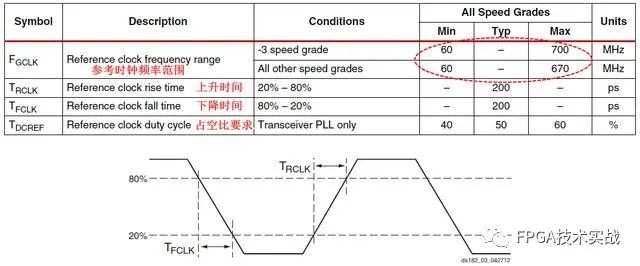

1.2参考时钟电气特性要求

FPGA收发器参考时钟开关特性和DC特性要求分别如图3和图4所示。

图3、FPGA收发器参考时钟开关特性要求

图4、FPGA收发器参考时钟DC特性要求

2.硬件电路设计

2.1晶振选型

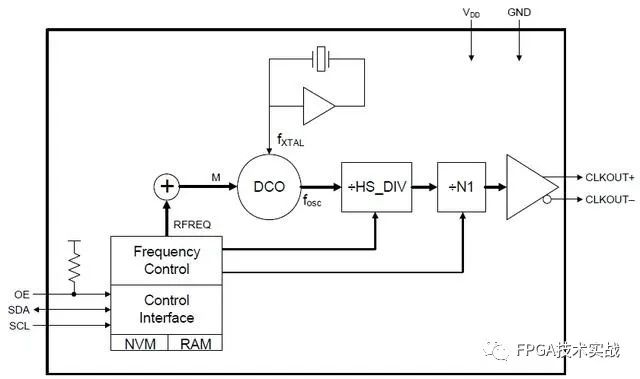

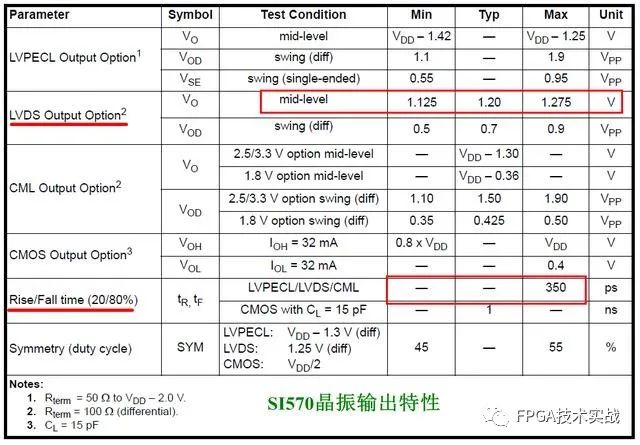

按照章节1中FPGA收发器参考时钟要求,我们选择Silicon labs公司的si570系列可编程晶振,该晶振典型应用SONET/SDH、10G以太网通信、时钟恢复等场合。该晶振输出特性如图6所示。

图5、SI570晶振内部功能框图

图6、SI570晶振输出特性

2.2原理图设计

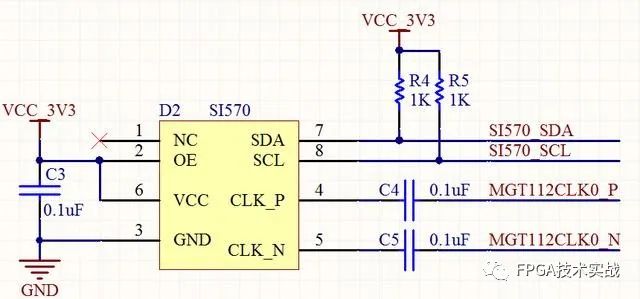

FPGA收发器参考时钟晶振SI570原理图设计如图7所示。

图7、SI570原理图设计

3.SI570 FPGA软件配置及结果测试

3.1 SI570晶振配置方法

从图5中,可看到SI570控制接口采用I2C接口。我们在配置该晶振时要按照以下操作步骤进行:

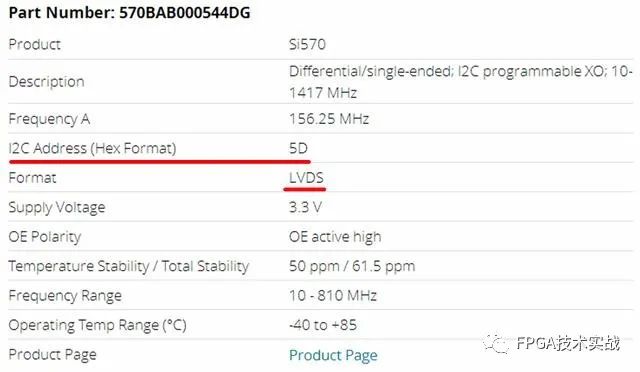

1.SI570根据家族类别,器件地址都不同,故首先需要去Silicon官网查找项目选型的晶振型号对应的器件地址。举例SI570晶振型号:570BAB000544DG,该型号参数如图8所示。在该图中,我们可以得到可编程晶振的重要参数,如器件的I2C地址(0x5D),出厂默认输出频率(156.25MHz),频率范围等等。

图8、SI570出厂参数信息

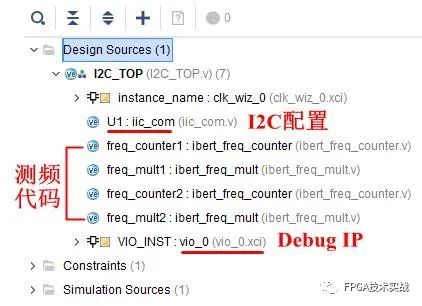

2.编写FPGA软件,读出晶振SI570内部出厂默认寄存器配置字。FPGA实例工程如图9所示。

图9、SI570测试例程工程

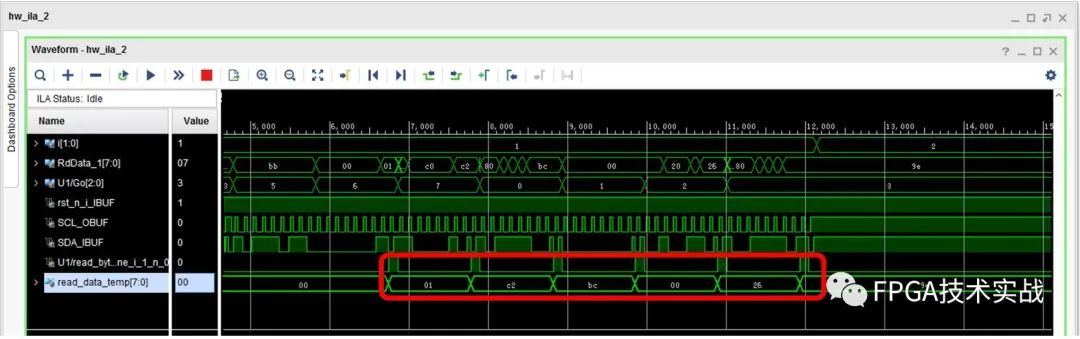

3.根据读出的SI570内部寄存器默认配置值,FPGA I2C总线读时序图如图10所示。

图10、FPGA I2C总线读时序图

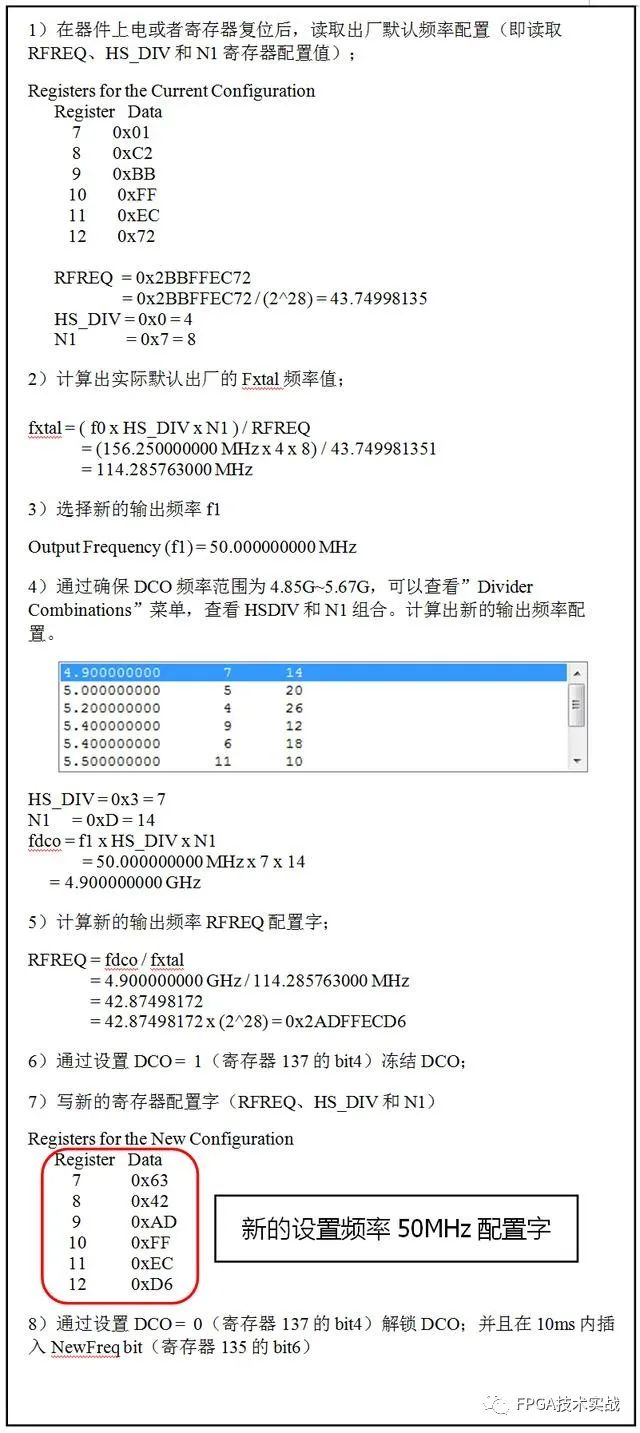

4.利用Silicon官方Programmable Oscillator Calculator软件计算出要求出频率所需的配置寄存器值。如图11所示,本设计将SI570输出频率设置为50MHz。

图11、计算SI570配置寄存器流程步骤

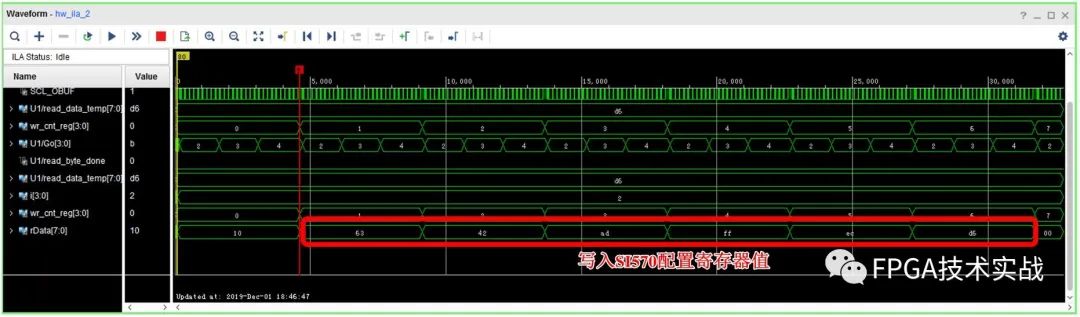

5.写SI570寄存器配置值。FPGA I2C总线写时序图如图12所示。

图12、FPGA I2C总线写时序图

3.2 SI570配置结果测试

在图5SI570测试例程工程中,我们还加入了SI570输出频率测试代码,以通过FPGA在线逻辑分析仪测试SI570输出频率是否达到50MHz设计输出要求。测试结果如图13所示,可以看到晶振输出结果符合设计要求。

图13、SI570输出频率测试结果

编辑:lyn

-

收发器

+关注

关注

10文章

2967浏览量

104750 -

晶振

+关注

关注

32文章

2467浏览量

66842 -

数字电路

+关注

关注

192文章

1392浏览量

79738 -

Xilinx FPGA

+关注

关注

1文章

29浏览量

7138

原文标题:Xilinx FPGA收发器参考时钟设计应用

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

stm32f4xx的CAN对ID配置有要求吗?CAN收发器是什么型号的?

工业级光纤收发器和商业级光纤收发器有什么区别呢?

光纤收发器ab端如何区分 光纤收发器a与b可随便放吗

什么是单纤收发器,什么是双纤收发器呢?他们有什么区别?

光纤收发器怎么分ab端 光纤收发器ab端的区别 光纤收发器ab端放哪里

基于FPGA的Aurora 8b10b光通信测试方案

Xilinx FPGA的GTx的参考时钟

Xilinx FPGA时钟资源概述

利用IBERT核对GTX收发器板级测试

XILINX FPGA IP之MMCM PLL DRP时钟动态重配详解

XILINX FPGA IP之Clocking Wizard详解

Xilinx FPGA收发器参考时钟设计要求与软件配置及结果测试

Xilinx FPGA收发器参考时钟设计要求与软件配置及结果测试

评论