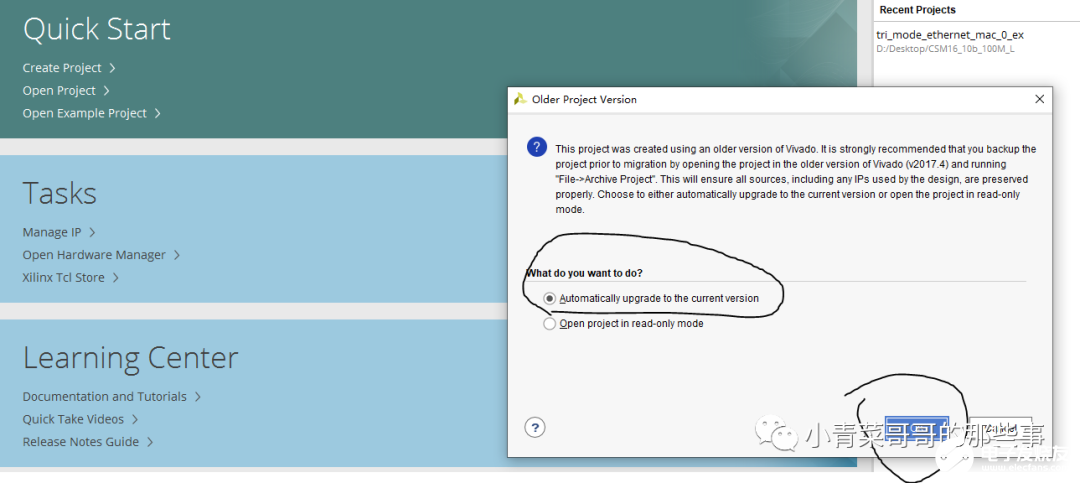

打开旧版本的vivado工程后,会弹出如下图窗口要求用户选择(图1)。如果用户需要重新修改工程的话,就选择第一种,反之如果只需要查看工程,并不做修改,就选择第二种。

图1

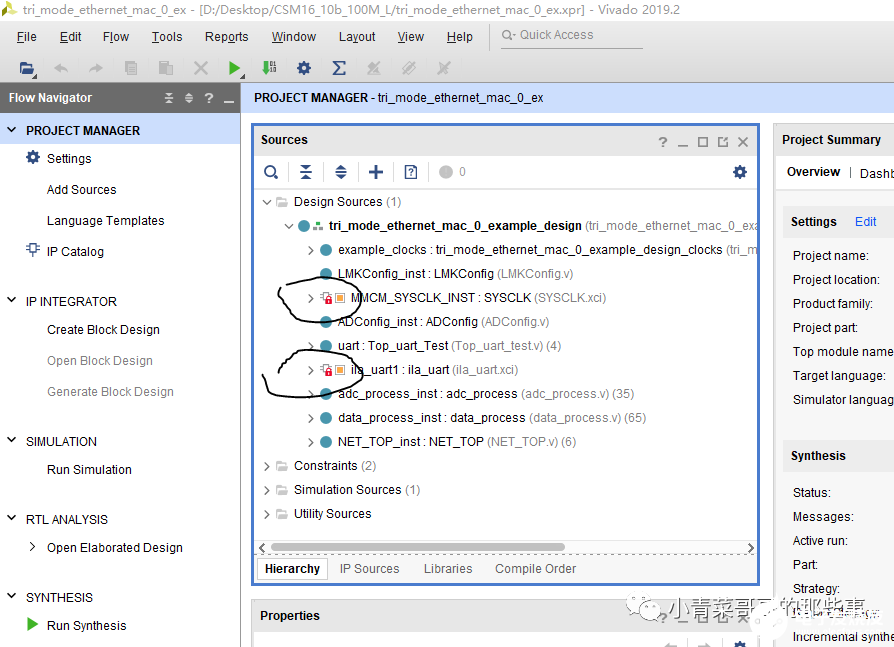

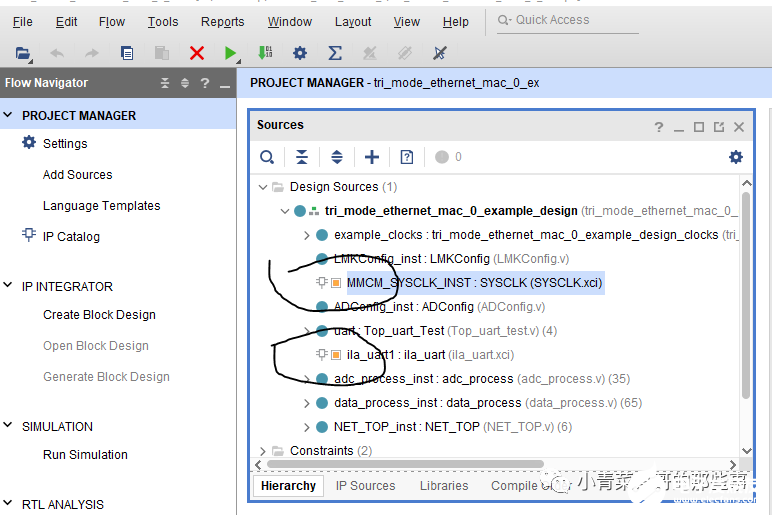

我们选择第一种方式来实现IP核的更新和可修改操作。打开工程后会出现如下图所示的工程,工程中的IP核会标红并有一个锁的标志(图2),此时该IP核不可以被更新和编辑。

图2

更新IP核的方法有两种:

方法一:

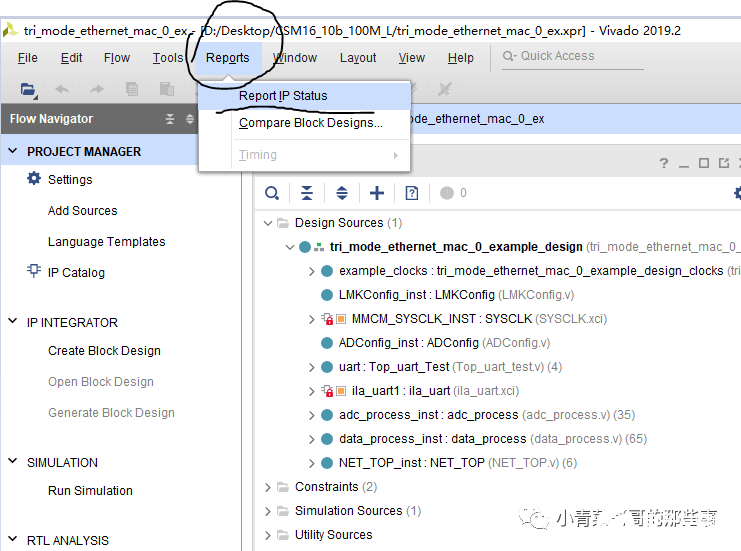

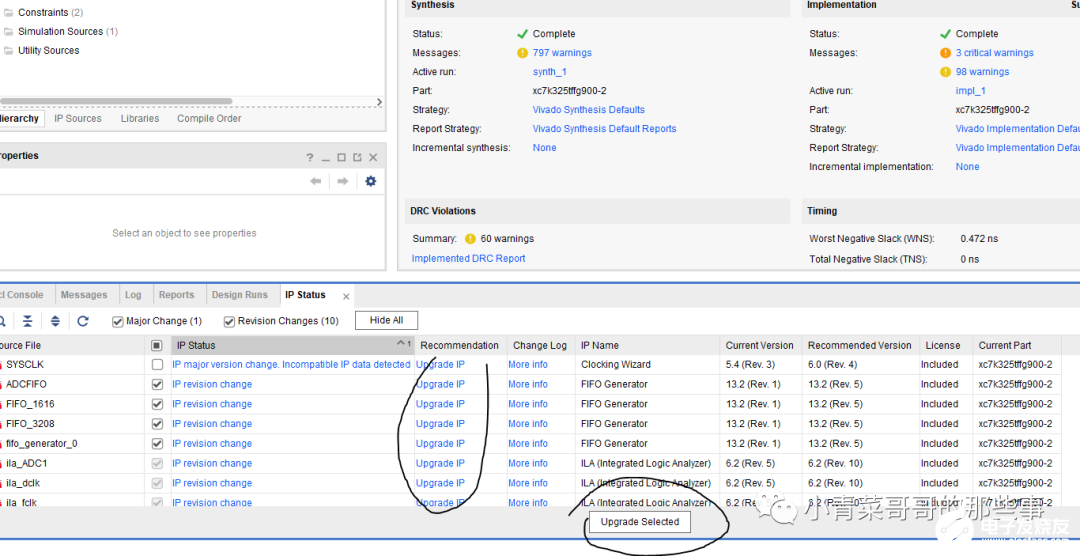

查询IP核的状态报告 菜单栏:Reports-》 Report IP Status(图3),在vivado的底部窗口会弹出工程所有的IP核的状态(图4),选择需要更新的IP核即可。更新完成后,被锁住的IP就可以正常配置了。

图3

图4

方法二:

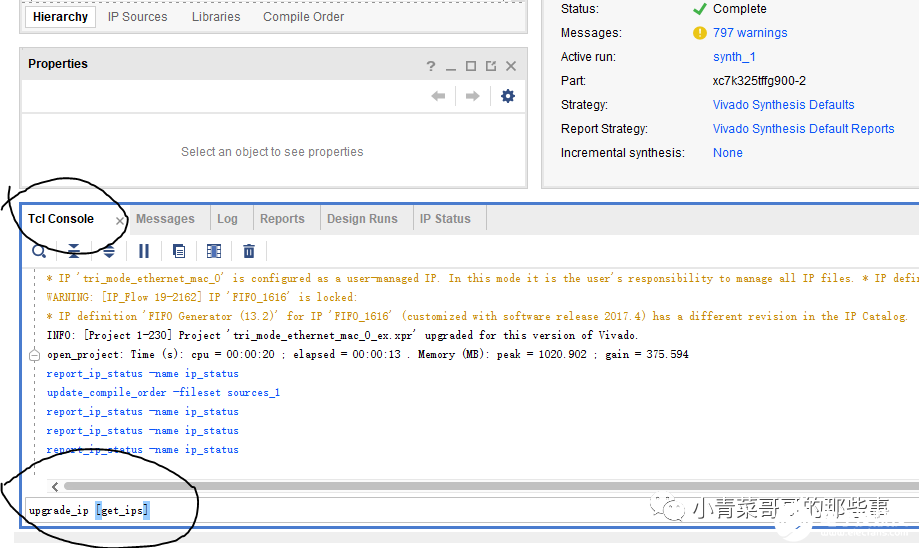

在 Tcl console中 执行如下一条命令即可:upgrade_ip [get_ips]。按下回车键即可同时更新工程所有的IP核图(5)。

图5

通过上述两种方法更新后的IP核状态如下图6所示:双击已经能够正常编辑,红色锁也消失了。

编辑:lyn

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

IP

+关注

关注

5文章

1401浏览量

148267 -

Vivado

+关注

关注

18文章

789浏览量

65091

发布评论请先 登录

相关推荐

晶振失效三大原因及解决办法

晶振失效三大原因及解决办法 晶振失效是指晶体振荡器无法正常工作,造成电子设备不能正常运行的情况。晶振在电子设备中起到非常关键的作用,它是产生时钟信号的核心元件。晶振失效会导致设备的计时不准确甚至

FPGA实现基于Vivado的BRAM IP核的使用

文章是基于Vivado的 2017.1的版本,其他版本都大同小异。 首先在Vivado界面的右侧选择IP Catalog 选项。

Vivado中BRAM IP的配置方式和使用技巧

FPGA开发中使用频率非常高的两个IP就是FIFO和BRAM,上一篇文章中已经详细介绍了Vivado FIFO IP,今天我们来聊一聊BRAM IP。

PCBA加工焊点拉尖产生的原因及解决办法

一站式PCBA智造厂家今天为大家讲讲什么是PCBA加工焊点拉尖?PCBA加工焊点拉尖产生原因及解决办法。接下来为大家介绍PCBA加工焊点拉尖产生原因及解决办法。

Vivado生成IP核

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸载过Modelsim,用vivado打开过ISE工程,因为工程中很多IP核不能用所以在重新生成过程中发现了这个问题,还请

发表于 04-24 23:42

关于Vivado版本升级导致的IP锁定的俩种解决办法浅析

关于Vivado版本升级导致的IP锁定的俩种解决办法浅析

评论