在过去几年里,由于数据输入/输出的要求不断提高,使用户对数据总线带宽提出更高的要求,由此产生了很多基于高速序列构架的传输标准。包括PCI Ex-press,HyperTransport,InfiniBand,RapidIO和Star-Fabric等。

2002年第2季度PCISIG组织发布了PCI Express1.0规范,定位于设计成一种系统互连接口。该组织又于2005年第3季度发布PCI Express规范在工业控制领域的规范PICMG EXP.0 CompactPCI Express Specification R1.0,被称之为CompactPCI Express(在下文中简称为CPCIe)规范。

CPCIe系统可以兼容CPCI模块,具体的实现方法是在系统中加入CPCIe到CPCI的桥接模块,该模块被称为混合桥接模块。

进行混合桥接电路的设计主要实现以下内容:

(1)PCI部分接口的设计实现;

(2)PCIe总线接口设计实现。

1 设计原理

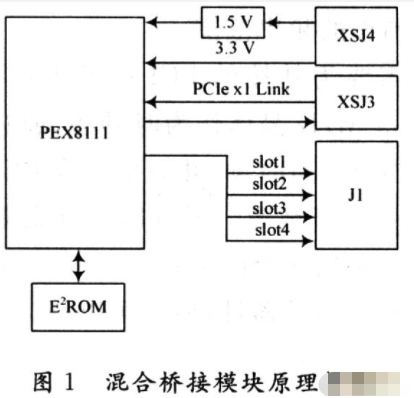

如图1所示,该模块由XSJ4连接提供3.3 V电源,在板上使用DC-DC电压转换模块,将3.3 V电压转换为1.5 V电压,提供给PEX8111使用。PEX8111的上行端口(Upstream)为x1的PCI Express接口,下行接口(Downstream)为32位/33 MHz的PCI总线,该PCI接口可以实现PCI总线的Host功能。

2 实现方法

2.1 主要原器件选择

在该设计中采用成熟技术,选用常用、可靠的控制芯片,结合一些常用的外围电路和专用电路实现全部的功能,即选择PEX8111作为接口芯片,利用功能芯片实现硬件逻辑。

PEX8111是PLX公司推出的专门用于PCI Ex-press和PCI总线之间桥接的芯片,它包含1个x1的PCI Express端口和1路32位PCI接口。它的外围电路少,设计简单。

2.2 PCI Express硬件接口实现

每个PCI Express的端口包括两部分信号,端口控制信号和通信信号。端口控制信号包括热插拔控制信号、时钟使能信号、电源使能信号等。通信信号主要由lane 信道组成,每个lane信道包含收发差分信号对各一个,每个PCI Express的端口包含的lane信道数是可以伸缩配置的,也就是说包含lane信道的数目是可变的,在该模块中单个端口包含1个lane信道。在 lane信道上传输的是高速差分信号,在每个信号差分对上信号的最高的传输速率可以达到2.5 Gb/s。在两个设备之间互连的lane信道需要加入电容隔离直流信号,考虑到传输信号的频率,电容的封装尺寸一般为0402,小的尺寸可以降低电容的串联等效电感,提高电容在高频信号区域的使用性能。

2.3 时钟设计

发送器以2.5 Gb/s的速率定时输出数据。实现该速率的时钟必须精确在中心频率±300 ppm内,它最大允许每1 666个时钟偏离1个时钟。设备获取时钟输入的方式有两种:采用本板时钟和使用外部输入时钟,该设计使用外部时钟。如果使用扩展频谱定时(Spread Spectrum Clocking,SSC)功能,一般都要求链路上的发送器和接收器必须使用同一参考时钟,SSC是一种用于缓慢调制时钟频率的技术,以便降低时钟中心频率处的EMI辐射噪音。有了SSC,辐射的能量就不会产生2.5 GHz的噪音尖峰信号,因为辐射能量被分散到2.5 GHz周围小的频率范围。

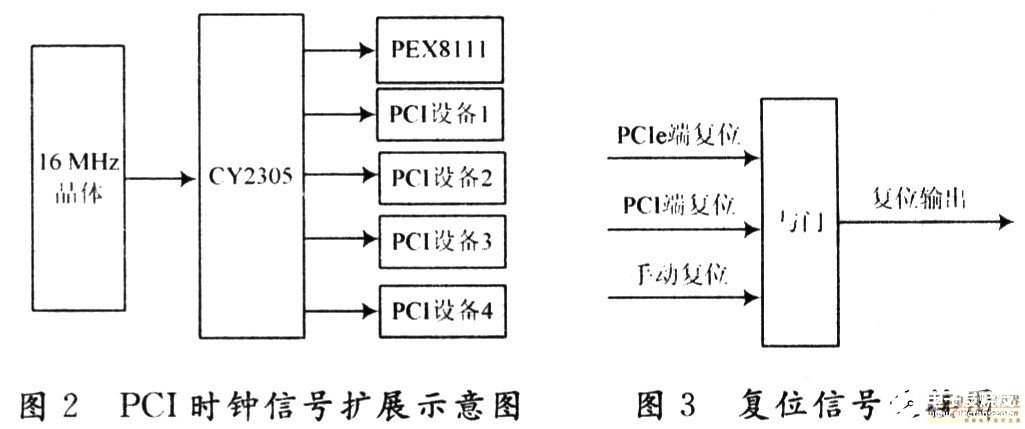

本模块需要为外接的PCI设备提供时钟信号,如图2所示。33 MHz晶体作为时钟源,通过零延时缓冲器CY2305输出5路时钟,并分别作为PEX8111和4个外接PCI设备的时钟源。零延时缓冲器是一种可以将一个时钟信号扇出多个时钟信号,并使这些输出之间有零延时和很低偏斜的器件,所以可以认为4个外接PCI设备工作在同一时钟下。

2.4 PCI接口设计

该PCI接口实现的功能为PCI的HOST功能,包含总线信号和仲裁信号。在进行该模块设计时需要注意连接器J1的信号定义与标准的J1接口有一些差别。因为如果将PCI总线信号完整的引出需要两个连接器J1,J2配合使用,但是因为高速连接器XSJ3处于原本J2的位置上,因此在缺少部分信号针的情况下无法实现完整PCI host功能,采取使用了特殊的CPCIJ1连接器的方法解决这个问题,这种连接器比普通J1连接器多出15个信号引脚,可以使用这些多余的引脚引出 REQn,ACKn信号。

2.5 电源设计

PEX8111芯片需要用到3种电源。其中PCI总线信号为5 V,I/O供电电压为3.3 V,串行收发器的电源电压为1.5 V,所以本模块需要提供5 V,3.3 V和1.5 V三种电压源。

5 V, 3.3 V电压由系统提供,1.5 V由3.3 V电压转换获得,选取国家半导体公司的LP2992作为3.3~1.5 V电压转换模块。该模块具有90%以上的转换效率、简单的外围电路、更小的封装、2.5%以下的纹波电压等特点。

2.6 复位设计

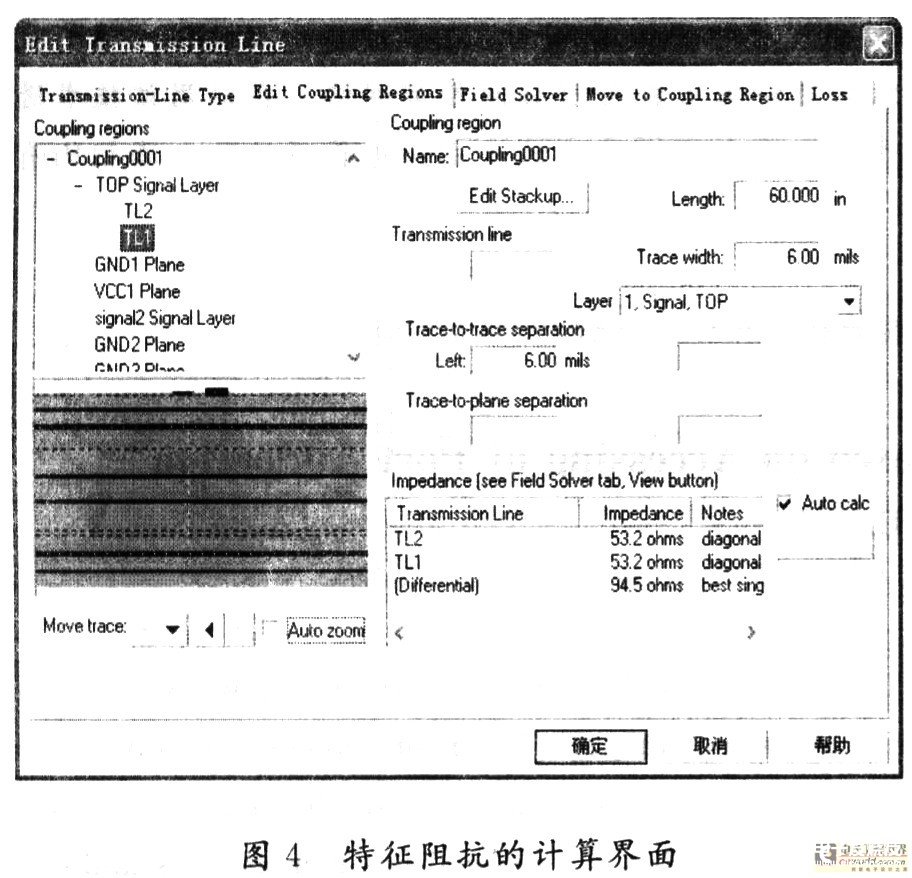

复位输入有三个,来自PCIe端的复位,来自PEX8111复位输出,手动复位信号,保证在主机侧出现冷复位和要求本板单独复位的情况下,可以将复位信号向下传递,如图3所示。

3 高速电路设计

基于CPCIe总线的电路属于高速电路,在电路设计之初就采用仿真工具进行验证,并根据仿真结果不断调整自己的设计。

对所设计的电路进行仿真是该设计的关键点。PEX8111芯片信号的种类和数目都比较少,在芯片外围没有复杂的逻辑设计,在电路设计上对时钟和电源的要求也比较简单,但是对传输在PCB上高速差分信号的质量有很高的要求,这个要求也是当前所有高速设计面临的共性问题。由于高速PCB设计需要考虑的因素很多,比如介质、平面分割、信号的等长等,传统的设计准则已经不再准确,所以需要依靠仿真工具来提供设计依据。在该设计中采用的仿真工具是Mentor公司 Hyperlynx GHz,Hspice仿真模型,由器件的生产厂家提供。

仿真的过程主要包括前仿真和后仿真,以下叙述两种仿真的具体内容。

3.1 阻抗控制

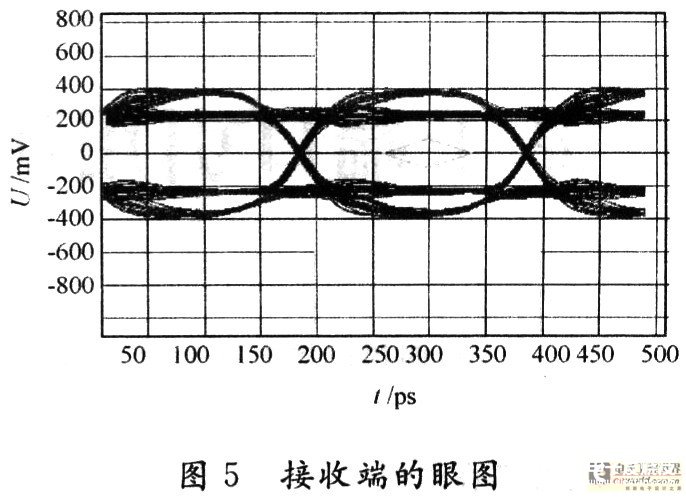

PCI Express规范要求走线阻抗为100 Ω,差分阻抗、单端阻抗为50 Ω。阻抗主要由线宽、线间距、铜皮厚度、介质层厚度、介质材料等决定。特征阻抗的计算界面如图4所示,经计算特征阻抗为94.5 Ω,满足要求。

PCI信号的特征阻抗为75 Ω,为了同时满足PCIe和PCI的阻抗要求,可以采用两种手段,首先可以将两种信号线的宽度设置为不同宽度;其次是将两种信号放置在不同信号平面上。两种方法各有优劣,前者由于制作工艺限制线宽有下限,所以需要将PCIe信号线宽设置得比较宽,不利于走线。后者需要增加信号层,直接增加成本。采取什么方法需要综合考虑。

3.2 后仿真的实现

后仿真主要是在PCB绘制完成后,在前仿真的基础上将PCB相关的数据导入后再进行的仿真。由于PCI部分的信号电路设计已经非常成熟,有大量的经验法则可以借用,并且信号的速度比较慢,因此不对这部分信号进行仿真,只对PCIe差分信号对进行仿真。图5给出导入PCB参数后,接收端眼图的仿真结果。可见,所有时间点上的信号电压均在接收器可以识别的范围之内。

4 结 语

随着技术的发展。基于CPCIe总线接口的模块会被越来越多的使用,但是从成本考虑,CPCI接口的模块不会被立即完全的替换,CPCIe模块和CPCI模块在机箱中共存的情况将长期存在,混合桥接模块是将两者联系起来的纽带,它将作为一个重要的插件模块在工业控制计算机系统中广泛应用。

责任编辑:gt

-

电源

+关注

关注

182文章

16543浏览量

244669 -

芯片

+关注

关注

446文章

47746浏览量

409040 -

总线

+关注

关注

10文章

2702浏览量

87203

发布评论请先 登录

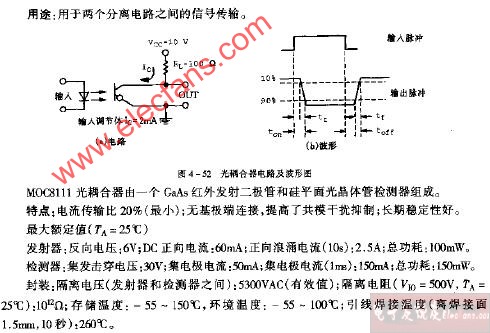

相关推荐

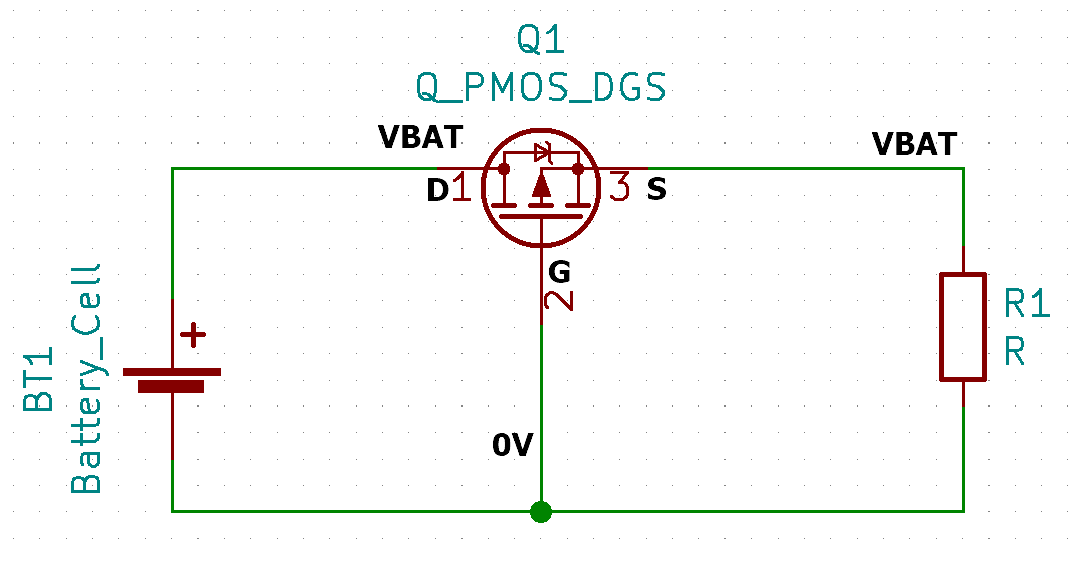

基于MOS管的电源防反接电路设计

realtek 8111c找不到

全桥逆变电路又是什么原理呢

PEX8111 pdf datasheet

SD卡总线拓扑及连接电路图

基于FPGA的PEX8311的LBS控制器的实现

CPCIe-BP6606硬件使用说明书

基于PEX8111芯片和CPCIe总线实现混合桥接电路的设计

基于PEX8111芯片和CPCIe总线实现混合桥接电路的设计

评论