作者:李小贝,陈东进,沈小丰

1 数字视频监控系统简介

视频监控近年来得到了迅速的发展,应用范围不断地扩展。以往国内使用的视频监控系统主要是模拟系统,到了20世纪90年代末,随着网络宽带、计算机处理能力和存储容量的迅速提高,以及各种实用视频信息处理技术的出现,视频监控从模拟视频监控进入了数字化的网络时代,即数字视频监控系统。数字视频监控系统将摄像机获得的模拟信号转变成数字信号,便于计算机处理,或者由数字摄像机直接输出数字视频信号。在计算机显示器上显示或者在监视器上显示多路实时活动图像的同时,还可以将各路信号分别存储于计算机的硬盘内,或者在网络上进行传输。

数字视频监控系统是以计算机或嵌入式系统为中心,视频处理技术为基础,利用图像数据 压缩的国际标准(JPEG、MPEG1或MPEG4),综合利用图像传感器、计算机网络、自动控制和人工智能等技术的一种新型监控系统。

数字视频监控系统除了具有传统闭路电视监视系统的所有功能外,还具有远程视频传输与回放、

自动异常检测与报警、结构化的视频数据存储等功能。

数字视频监控系统输入模拟视频信号,数字化后进行图像压缩,然后进行存储、传输及相关控制。他主要包括3个部分:

数字视频录像(Digital Video Recorder,DVR)将视频图像采集并保存在硬盘里面,这种设备称为数字视频录像机,或硬盘录像机。

数字视频服务器(Digital Video Recorder,DVS)将图像通过网络传输到远方的其他计算机终端。

数字视频控制(Digital Video Control,DVC)数字视频控制系统将控制指令送往受控设备,如控制云台的上下左右、摄像机的聚焦、远近和变焦等。

与数字视频监控系统相关的主要技术:视频数据的压缩、视频的分析与理解、视频流的传 输与质量控制。

2 数字视频监控系统中的DVR技术

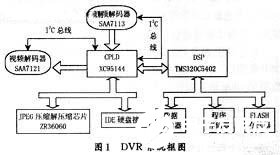

目前大多数的数字视频监控系统是通过图像采集卡将模拟摄像机传输过来的模拟视频图像转换成数字视频图像的,因此数字视频采集卡是数字视频监控系统中的关键技术。但是大多数的数字视频采集卡都是基于PC机技术的,这样就限制了视频采集的局限性和移动性。随着DSP技术和嵌入式技术的发展,可以用性价比高的DSP芯片代替传统的PC机,来控制整个DV R的工作和完成图像探测功能。整套DVR系统的组成如图1所示。

2.1 DVR系统控制

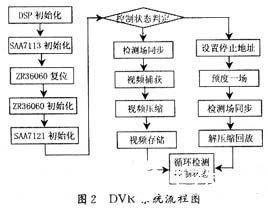

该系统中采用了TI公司推出的高性能数字信号处理器TMS320VC5402。其采用程序空间与数据空间完全独立的哈佛总线结构,指令的执行采用流水线结构,内部有一到多个处理内核,带有片上硬件乘法器,其指令执行速度最快为几十纳秒,处理能力为100 MIPS。这些为DSP在高速大数据量的数据采集处理系统中提供了广阔的应用空间。片内共有8条总线(4条程序存储器总线、1条数据存储器总线和3条地址总线)、片上存储器和片上外围电路等硬件,有高度专业化的指令系统,具有功耗低、高度并行等优点。系统设计中在DSP的外部扩展了64 k*16 b的程序存储器和256 k*16 b的数据存储器,DSP的运行程序由4 Mb的FLAS H ROM来加载程序。整套DVR系统的工作过程由DSP来控制完成,其流程图如图2所示。

2.2 视频采集技术

可编程视频解码芯片采用SAA7113;该芯片是可编程视频处理芯片,采用CMOS工艺。通过简单的I2C总线可以对其实现编程控制;内部包含两路模拟处理通道,能实现视频源的选择、抗混叠(去假频)滤波、模/数变换、自动增益控制、时钟产生、多制式解码及亮度、对比度和饱和度控制。他将不同制式的模拟信号统一成为相同的数字标准,采用ITUR B T601格式,采样时对亮度信号和两个色差信号分别编码,对不同制式信号采用单一的取样频率,而且和任何模拟系统的彩色副载波频率无关,因此在分量系统中不再包含任何副载波。取样频率定为13.5 MHz,他也是对亮度信号Y的取样频率,由于色度信号的带宽远比亮度信号的带宽窄,因而对色度信号U和V的取样率较Y减半,为6.75 MHz。每个数字有效行分别有720个亮度取样点和360*2个色差信号取样点。对每个分量的取样点进行均匀量化,对每个取样进行8 b的PCM编码。

由于DSP没有I2C总线接口,本系统采用CPLD辅助DSP模拟I2C总线的控制方式,在CPLD内部I2C的控制功能用Verilog语言编写,其主要代码如下:

在本系统中通过在CPLD内部设置I2C总线的地址和寄存器的方法来完成DSP用数据模拟I2 C总线的任务,使用起来十分方便。

2.3 JPEG压缩技术

在实际应用中,采用ZORAN公司的单片JPEG压缩/解压缩芯片ZR36060,其内部结构如图3所示。

ZR36060的特点如下:

(1)单片结构,片上集成了JPEG压缩/解压缩所需全部模块。

(2)运动JPEG压缩/解压缩功能,能够处理高达25 帧/s的方象素及CCIR PAL或30 帧/s的方象素及CCIR NTSC实时视频信号。

(3)多种模式数据率控制,可以很方便地改变压缩比。

(4)视频数据输入端口支持多种视频解码器(A/D变换器),如Philips,Brooktree,Samsung等。

(5)视频总线宽度可以是8 b或16 b。

(6)同步发生器可工作于主或从模式。

(7)控制端口支持标准微处理器操作。

(8)提供多种片上视频处理:视频混合(mix)、尺度变换(scale)、剪切(crop)及背景色输出等。

(9)压缩数据可以主方式从压缩数据端口或以从方式从控制端口输出,两种方式都有握手功能以便进行数据流控制。

ZR36060其数据端口有3个:

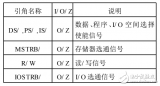

控制端口用来完成对ZR36060的初始化,当芯片工作于数据从方式时,还用于输出或输入压缩数据。视频端口压缩时输入原始视频数据,解压缩时输出解压后的视频数据,除数据线外还有行场同步、时钟等必要信号线,同步可工作于主方式或从方式,可直接与视频解码器或帧存储器接口完成实时的运动JPEG处理。

压缩数据端口用于数据主方式时输出或输入压缩数据。

压缩数据流压缩时数字Y,C信号由Y,C总线进入ZR36060,经视频接口进入条存储器(St rip Memory)缓存,之后进入JPEG处理机进行压缩,压缩后的JPEG数据进入一个长度为512的先入先出寄存器(FIFO)缓存,再经数据(数据主方式)或控制端口(数据从方式)输出。

在数据主方式下,ZR36060输出CCS信号指示数据有效,并输出CWR信号作为数据选通,外部设备若来不及接收数据可向ZR36060的BUSY引脚发BUSY请求,ZR36060停止向外输出数据,暂时将数据压入FIFO,若FIFO溢出,则JPEG处理机停止压缩,视频数据暂时压入条存储器。当外设撤消BUSY请求后,ZR36060继续压缩、输出数据,如果外设速度太慢导致条存储器也溢出,则ZR36060将给出错误指示并在中断允许的情况下发出中断请求。在数据从方式下,由外设向ZR36060读数据,BUSY引脚改由ZR36060驱动输出,若ZR36060内部FIFO无数据可读,B U SY将变为有效以通知外设,此时外设应等待BUSY变为无效。若外设读数据速度太慢也将导致出错,数据压满FIFO和条存储器,其过程与主方式相同。由于采用FIFO和条存储器,瞬时速度很高的JPEG数据得以缓存,外设可以平均速率访问ZR36060,可降低对外设的要求。

2.4 硬盘接口技术

IDE接口的硬盘驱动器提供了2种数据传输模式:PIO模式和DMA模式。由于PIO模式控制相对容易,提供了一种编程控制输入/输出的快速传输方法。该模式采用高速的数据块I/O,以扇区为单位,用中断请求方式与CPU进行批量数据交换。在扇区读写操作时,一次按16 b长度通过内部的高速PIO数据寄存器传输。通常情况下,数据传输以扇区为单位,每传输一扇区数据产生一个中断。由于本系统图像压缩数据的最大速率只有20 kb/s,采用PIO写盘速度可以达到192 kb/s,完全可以满足本系统的要求。

2.5 视频编码技术

视频编码器选用Philips公司的SAA7121,在DSP的控制下将JPEG解压缩后的数字YUV视频数据编码为PAL模拟视频信号输出。SAA7121也是由I2C总线来控制,其控制方法同SAA7113。

3 本系统的实际工作性能

(1)输入信号格式:标准视频信号,PAL制或NTSC制。

(2)画面大小:352*248(也可是352*288)。

(3)每秒录制或播放25帧,每帧2场,共50场,隔行扫描。

(4)每场图片压缩后大小平均为10 kB,0.5 MB/s,1.8 GB/h,可根据需 要配接10“80 G的硬盘,实现5”40 h的连续录像。

(5)对于用于监控场合时,可以每秒录制25帧25场,回放时每秒25帧50场,这样可以节约一倍的硬盘空间,把码率降为0.25 MB/s,也就是2 MB/s。用80 G硬盘能录80多个小时。

4 结语

本系统用MJPEG的压缩方法虽然码率比较大,但效果确实很好,实测时录制了一段电视节目,观看的主观感受比基于MPEG 1的VCD要清晰,毫无色块现象,和原信号基本没有差别。另外本系统能够脱离PC机独立运行,同时由于采用DSP控制整个系统,其成本比使用ARM控制的监控系统要低,有较大的经济价值,特别是应用在车载视频监控系统中有很大的发展空间。

责任编辑:gt

-

处理器

+关注

关注

68文章

18202浏览量

221925 -

芯片

+关注

关注

446文章

47685浏览量

408809 -

视频监控

+关注

关注

17文章

1682浏览量

64189

发布评论请先 登录

相关推荐

MAX121/TMS320VC5402的高速数据采集接口设计

怎样去设计TMS320VC5402与模拟芯片TLC320AD50C的接口?

TMS320VC5402 的Flash并行Bootloade

基于TMS320VC5402 的DSP基本系统的设计

TMS320VC5402通用I/O资源及其应用

基于DSP芯片TMS320VC5402的HPI通信设计

TLC320AD50C介绍及与TMS320VC5402连接分析

TMS320VC5402 DSP与串行AD73360 A/D转换器的接口设计

TMS320VC5402 数字信号处理器

基于DSP TMS320VC5402芯片实现数字视频监控系统的设计

基于DSP TMS320VC5402芯片实现数字视频监控系统的设计

评论