AMD即将发布基于7nm Zen3架构的第三代霄龙7003系列数据中心处理器(代号Milan),但是没想到,第四代的猛料也被抖了出来,而且惊喜还在继续。

据一贯专注硬件的推特博主@ExecutableFix,代号Genoa的四代霄龙将采用台积电5nm工艺、Zen4架构,最多96核心192线程,支持12通道DDR5-5200内存、128条PCIe 5.0通道(双路对外160条),热设计功耗最高320W(可上调至400W),接口换成SP5 LGA6096。

今天又有一份关于Zen4核心的曝料出现,显示有超过64个核心,每核心双线程,支持57位虚拟内存寻址(最大容量128TB)、52位物理内存寻址(最大容量4TB)。

更惊喜的是,Zen4将会支持AVX-512、Bfloat16等新的指令集!

尤其是AVX-512,也得到了@ExecutableFix的确认。

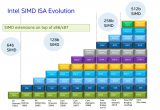

AVX-512也就是AVX3,也就是“高级矢量扩展”,第一代AVX出现于Sandy Bridge二代酷睿,第二代AVX2诞生于2011年的四代酷睿(Haswell),最新的第三代则发布于2013年,最早用于至强产品线,目前已经下放到Ice Lake 10代酷睿、Tiger Lake 11代酷睿。

AVX、AVX2此前已得到AMD处理器的支持,AVX-512则一直是Intel的“专利”(尽管应用并不多),而接下来的AMD Zen4终于加入AVX-512,Intel无疑将失去已达独特优势。

当然,Intel说不定到时候已经有了第四代AVX-1024,毕竟不太可能让死对手就这么追上自己。

另外,Bfload16指令集也相当重要,是人工智能、机器学习的一个基础,Intel Cooper Lake三代可扩展至强和未来的Sapphire Rapids四代可扩展至强都支持。

责编AJX

-

处理器

+关注

关注

68文章

18250浏览量

222049 -

amd

+关注

关注

25文章

5190浏览量

132631 -

数据中心

+关注

关注

15文章

4178浏览量

69930

发布评论请先 登录

相关推荐

什么是RISC-V?RISC-V指令集的优势

【米尔-全志T113-i开发板试用】使用ruapu探测CPU指令集信息

【RISC-V开放架构设计之道|阅读体验】汇编语言和扩展指令集

【RISC-V开放架构设计之道|阅读体验】RISC-V基础整数指令集

【RISC-V开放架构设计之道|阅读体验】RV64指令集设计的思考以及与流水线设计的逻辑

【RISC-V开放架构设计之道|阅读体验】RISC-V基础整数指令集RV32I

risc-v标准指令集如何扩展?

翼辉信息已正式加入对申威SW64自主指令集架构的支持

请问ADSP-21469的汇编指令集ISA/VISA中有没有专门用来进行浮点数和定点数转换的指令?

同样是大小核,英特尔、AMD和Arm玩法有何不同?

AMD Zen4将支持AVX-512等新的指令集

AMD Zen4将支持AVX-512等新的指令集

评论