在ISSCC 2021国际固态电路会议上,台积电联席CEO刘德音公布了该公司的最新工艺进展情况,指出3nm工艺超过预期,进度将会提前。

不过刘德音没有公布3nm工艺到底如何超前的,按照他们公布的信息,3nm工艺是今年下半年试产,2022年正式量产。

与三星在3nm节点激进选择GAA环绕栅极晶体管工艺不同,台积电的第一代3nm工艺比较保守,依然使用FinFET晶体管。

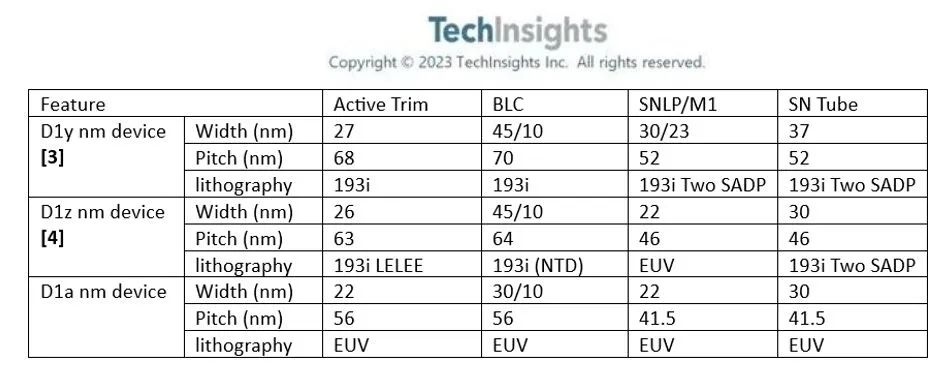

与5nm工艺相比,台积电3nm工艺的晶体管密度提升70%,速度提升11%,或者功耗降低27%。

不论是5nm还是3nm工艺,甚至未来的2nm工艺,台积电表示EUV光刻机的重要性越来越高,但是产能依然是EUV光刻的难题,而且能耗也很高。

刘德音提到,台积电已经EUV光源技术获得突破,功率可达350W,不仅能支持5nm工艺,甚至未来可以用于1nm工艺。

按照台积电提出的路线图,他们认为半导体工艺也会继续遵守摩尔定律,2年升级一代新工艺,而10年则会有一次大的技术升级。

责任编辑:PSY

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

台积电

+关注

关注

43文章

5264浏览量

164784 -

EUV

+关注

关注

8文章

574浏览量

85578 -

3nm

+关注

关注

2文章

220浏览量

13707

发布评论请先 登录

相关推荐

台积电3nm工艺迎来黄金期,苹果等巨头推动需求飙升

为加速其AI技术的突破,苹果计划在今年显著提升对台积电3nm晶圆的采购规模。即便苹果已独占台积电全部3nm产能,其订单量预计仍将较去年激增50%。

三星电子澄清:3nm芯片并非更名2nm,下半年将量产

李时荣声称,“客户对代工企业的产品竞争力与稳定供应有严格要求,而4nm工艺已步入成熟良率阶段。我们正积极筹备后半年第二代3nm工艺及明年2nm

台积电第二代3nm工艺产能颇受客户欢迎,预计今年月产量达10万片

据悉,台积电自2022年12月份起开始量产3nm工艺,然而由于成本考量,第一代3纳米工艺仅由苹果使用。其他如联发科、高通等公司则选择了4nm工艺

台积电3nm工艺预计2024年产量达80%

据悉,2024年台积电的第二代3nm工艺(称为N3E)有望得到更广泛运用。此前只有苹果有能力订购第一代N3B高端晶圆。经过解决工艺难题及提升产量后,台积电推出经济实惠的3nm版型,吸引

2nm意味着什么?2nm何时到来?它与3nm有何不同?

3nm工艺刚量产,业界就已经在讨论2nm了,并且在调整相关的时间表。2nm工艺不仅对晶圆厂来说是一个重大挑战,同样也考验着EDA公司,以及在

全球首颗3nm电脑来了!苹果Mac电脑正式进入3nm时代

前两代M1和M2系列芯片均采用5nm制程工艺,而M3系列芯片的发布,标志着苹果Mac电脑正式进入3nm时代。 3nm利用先进的EUV(极紫外

发表于 11-07 12:39

•326次阅读

什么是3nm工艺芯片?3nm工艺芯片意味着什么?

的大部分时间里,用于制造芯片的工艺节点的名称是由晶体管栅极长度的最小特征尺寸(以纳米为单位)或最小线宽来指定的。350nm工艺节点就是一个例子。

发表于 09-19 15:48

•5234次阅读

苹果拒绝为3nm工艺缺陷买单 台积电3nm按良率收费!

根据外媒报道,据称台积电新的3nm制造工艺的次品率约为30%。不过根据独家条款,该公司仅向苹果收取良品芯片的费用!

70%!台积电3nm按良率收费!

8月8日消息,据外媒报道,台积电新的3nm制造工艺的次品率约为30%,但根据独家条款,该公司仅向苹果收取良品芯片的费用!

Intel自曝:3nm工艺良率、性能简直完美!

Intel将在下半年发布的Meteor Lake酷睿Ultra处理器将首次使用Intel 4制造工艺,也就是之前的7nm,但是Intel认为它能达到4nm级别的水平,所以改了名字。

三星3nm GAA正式商业量产

一篇拆解报告,称比特微电子的Whatsminer M56S++矿机所用的AISC芯片采用的是三星3nm GAA制程工艺。这一发现证实了三星3nm GAA技术的商业化应用。

三星3nm良率已经超过台积电?

目前三星在4nm工艺方面的良率为75%,稍低于台积电的80%。然而,通过加强对3nm技术的发展,三星有望在未来赶超台积电。

台积电的3nm工艺价格为每片19150美元

尽管英特尔的第14代酷睿尚未发布,但第15代酷睿(代号Arrow Lake)已经曝光。新的酷睿系列产品将改为酷睿Ultra系列,并使用台积电的3nm工艺,预计会有显著的性能提升。

麻省理工华裔研究出2D晶体管,轻松突破1nm工艺!

然而,前不久麻省理工学院(MIT)华裔研究生朱家迪突破了常温条件下由二维(2D)材料制造成功的原子晶体管,每个晶体管只有 3 个原子的厚度,堆叠起来制成的芯片工艺将轻松突破 1nm。

台积电3nm工艺进度超前 EUV工艺获突破:直奔1nm

台积电3nm工艺进度超前 EUV工艺获突破:直奔1nm

评论