美光本周二公布其用于DRAM的1α新工艺,该技术有望将DRAM位密度提升40%,功耗降低15%。 1α工艺最初被用于生产DDR4和LPDDR4内存,未来或将但覆盖美光所有类型的DRAM。

同时,美光提到要实现DRAM的规模化仍很困难。鉴于EUV技术带来的性能优化还无法抵消设备成本和生产困难,美光近期不打算引入EUV光刻技术,考虑在未来的1??工艺中应用EUV技术。

一、美光1α工艺位密度或提升40%

到目前为止,美光已经将其DRAM生产的很大一部分转移到其1Z制程,该制程为生产存储器提供了更高的位密度和性能,可以有效地降低成本。因此,目前美光表示,它对利润率和产品组合感到相当满意。

美光的1α制程工艺预计将比1Z的位密度提高40%,这将相应地降低生产商的单字节存储成本。此外,该技术据称还能降低15%的功耗,以提高存储器性能。

在美光1α工艺提升的40%位密度中,大约有10%是由DRAM设计效率驱动的,这表明非EUV技术在当前生产过程中还有提升空间。

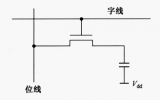

新的1α工艺将如同1Z工艺一样,继续使用6F2位线设计。目前美光已经实施了许多新的工艺制程,以适应小尺寸DRAM的制造。

美光DRAM工艺集成副总裁Thy Tran在被媒体采访时谈到,1α工艺的位密度能显著提高,是因为工艺制程的改进及设计效率的提升,这实现了矩阵效率的提高,也带来了10%左右的存储器性能提升。

美光对工艺技术改进了许多,比如大幅度缩小了位线(bitline)、字线(wordline)和网格(grid)。美光能够做到这一点,不仅因为对新工艺制程的积极,也因为它整合了全球各地最新、最好的材料,比如更好的导体材料和绝缘体材料。

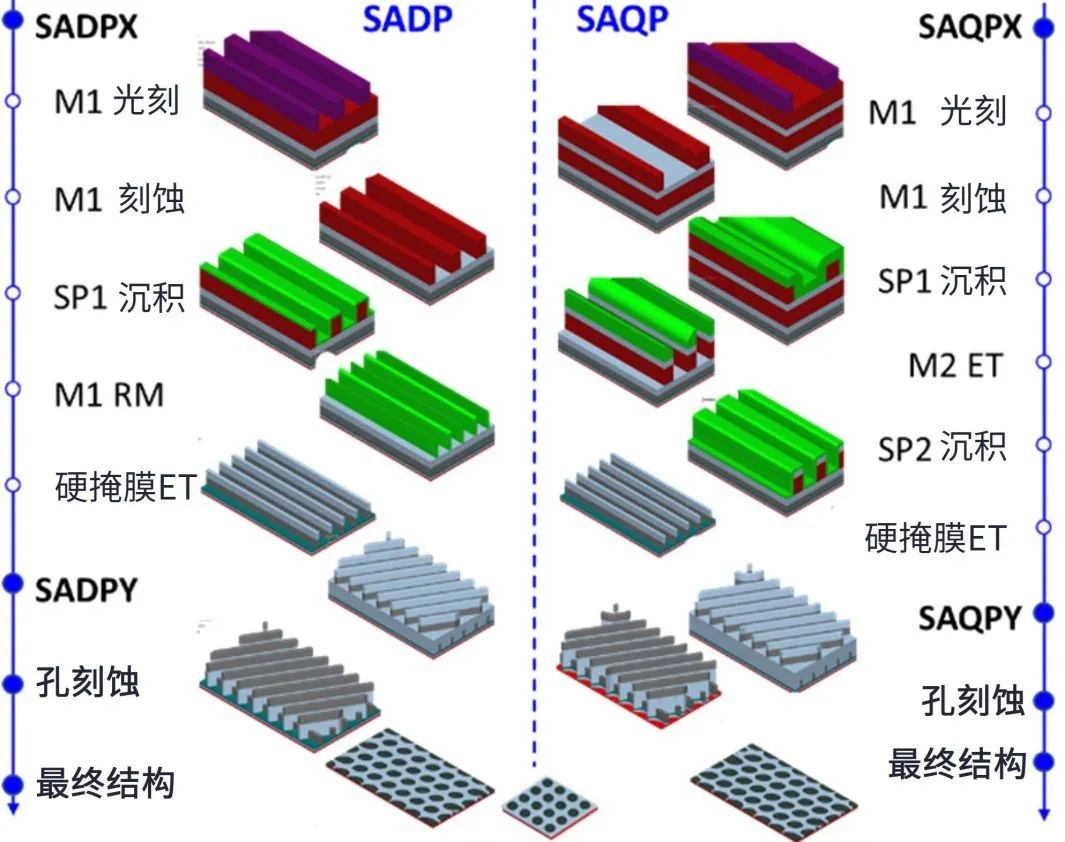

最后美光通过沉积、修改或选择性地蚀刻这些新材料来制作设备,缩小节距来使电池电容的容量更大。此外,美光还引入了先进的设备和技术,来改善图案层(patterned layer)。

DRAM 1α这项新工艺完成于美国爱达荷州博伊西的美光总部,但工艺制程的开发和制造过程涉及到了全球多个团队。

美光科技技术与产品执行副总裁Scott DeBoer称,采用了新1α工艺的DRAM器件在应用于数据中心、边缘AI和消费电子时,将解决很多问题。

一开始,美光会在其位于桃园和台中的晶圆工厂中,使用1α工艺生产8GB和16GB的DDR4和LPDDR4内存,最后该工艺将应用所有类型的内存。

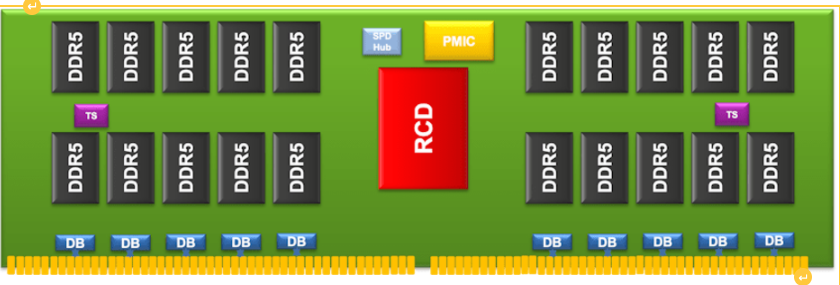

因为DDR5存储设备将具备更复杂的架构,像1α这样的工艺对于下一代DDR5存储设备格外重要。

Tran先生说:“我们的1α工艺将逐步部署在我们的产品组合中,并将在2022年成为主要工艺。同时晶圆厂也将逐渐升级,以配合生产,符合行业需求。”

二、存储器技术的升级对现有工艺制程将是巨大挑战

近年来,因为更高的性能需求,存储技术有了很大的发展。

其中具有代表性的DDR5和GDDR6X存储器,就会比之前DDR4、GDDR6存储器等复杂得多,这也是为什么DRAM技术需要升级的原因。

新存储技术的出现总会需要对现有工艺制程进行改造,像美光这样的存储芯片公司就需要在工艺技术的升级上投入更多的资金。

对此,美光技术开发高级副总裁Naga Chandrasekaran称,更高性能存储器的需求将会一直存在,美光有能力通过工艺和设计创新满足这一点。

比如新一代的DDR5虽然可以降低功耗,提供更高的带宽,但这种高性能的要求也对芯片尺寸提出了新的要求,单纯的尺寸缩放将无法满足生产需要。

而降低存储器成本的同时,还要满足更高的性能要求极具挑战性,这需要在工艺制程之外的多个领域进行创新。Chandrasekaran提到,美光就在满足了DDR5性能要求的同时,还考虑了成本因素。

这样的案例并不特殊,由于DRAM的处理技术开始变得更薄,美光这样的公司必须在成本、性能、质量和功耗之间找到合适的平衡。

Chandrasekaran说:“DRAM的扩展将变得更具挑战性,特别是当我们不得不与极其紧张的利润率作斗争时,还要优化存储器的部件成本、功耗、性能和质量。”

三、美光近期将不会使用EUV光刻技术

解决存储器几何尺寸缩放的方法之一是采用EUV光刻技术,但美光公司近期并不准备引入该技术,因为EUV并不能解决他们目前面临的很多问题。

美光接下来的三个DRAM节点将继续使用深紫外线(DUV)光刻技术,但他们正在考虑在1??工艺中使用EUV技术。

同时,即使没有EUV,美光也承诺改善下一代内存设备的性能和功耗。

“美光会在材料、工艺和设备上不断创新,以满足规模化的需求。”Chandrasekaran说,“我们正在研发相关技术。”

他还称EUV技术目前对美光并不是必需品,他们在多图案技术方面的专利和创新能够满足新技术下的性能和成本需求。

美光认为,未来几年,由于EUV技术还处于DRAM生产的早期阶段,其带来的工艺改进将被设备成本和生产困难所抵消。例如,美光最近展示的一张幻灯片表明,EUV技术成本过高,可扩展性优势忽略不计,关键尺寸(CD)均匀性不完美,而周期时间也并没有显着减少,因此目前EUV技术的生产效率仍然落后于DUV技术。

▲EUV技术可能在DRAM存储芯片生产上的时间节点

Naga Chandrasekaran称:“目前EUV技术在存储器方面的生产仍无法与先进的浸入式技术(immersion technology)相媲美。EUV也不一定是规模化生产的关键因素,美光现有技术足以保证产品性能。”

他还提到,虽然EUV技术正在进行改进,但其成本和性能仍落后于当前的生产模式。不过未来三年内,EUV技术可能会在成本和性能方面取得必要的进展。

所以美光也会一直推进对该技术的关注,并在符合要求的适当时间引入该技术。

这种情况下,正在开发中的1β和1??工艺将不会使用任何EUV设备。相反,该公司将继续使用现有生产技术,并指派其工程师设计在位密度、功耗和性能方面具有竞争力的DRAM器件。

美光大约每年都会引进一种新的制程工艺,根据外媒推算,它的1??工艺将在2024年或更晚的时候推出。这代表美光使用EUV技术可能落后全球最大内存制造商三星四年,这有利有弊。

届时美光将使用成熟的EUV设备、镀膜和抗蚀剂。相应的,它将不得不在没有用EUV技术进行大批量生产的经验时,跨多层使用EUV技术。

结语:美光的保守态度可能出于成本考虑

美光作为全球最大的存储芯片厂商之一,它一定程度上代表了存储技术的进步趋势,因此其在技术上的突破意义重大。

目前全球存储芯片市场垄断程度不断加剧,行业前三的龙头分别是三星、SK海力士和美光。DRAM市场大部分由三星、SK海力士和美国美光三家占据,而NAND Flash市场几乎全部被三星、SK海力士、日本东芝、闪迪(SanDisk)、美光和英特尔等六家瓜分,其中三星居垄断地位。

由于存储芯片的特殊性,它的设计相对简单,因此产品的线宽、产能、成品率与折旧是生产成本的核心。在这种情况下,美光对EUV技术采取保守策略也是有相应现实意义的。

责编AJX

-

芯片

+关注

关注

447文章

47769浏览量

409072 -

DRAM

+关注

关注

40文章

2176浏览量

181996 -

美光

+关注

关注

5文章

660浏览量

51008

发布评论请先 登录

相关推荐

美光科技: 纳米印刷助降DRAM成本

2024年DRAM投片量:一季度微增,下半年剧增

世界上首次商用D1Beta一代DRAM的诞生

SiC晶圆划片工艺:速度提升100倍,芯片增加13%

单芯片超过 100Gb,三星表示将挑战业界最高密度 DRAM 芯片

a17芯片提升多少 a17芯片与a16芯片的比较

为什么要提升芯片良率?良率为什么难提升?

8倍密度,像做3D NAND一样做DRAM

美光1αDRAM芯片工艺可提升密度40%

美光1αDRAM芯片工艺可提升密度40%

评论