超大规模集成电路设计进入到深亚微米工艺后,以时序驱动为主的开发方法使用更加普遍,面临的新挑战也随之而来:为了可制造性而要面临越来越多的金属层密度问题和天线效应问题,同时面积减小了,但由于连线延时效应影响,给布局布线带来了困难,以至于不得不根据布线后时序的结果回过头重新调整时序约束以保证后面布线后满足时序要求。这使得整个后端的时间进度压力加大,尤其对物理验证而言,作为后端设计人员将设计交给代工厂家前的最后一道程序,时间被压缩的很紧。因此有必要提出一套成熟的物理验证方法,来加快物理验证的速度,为加快芯片研发速度,尽快进入市场赢得时间。

1 物理验证及工具简述

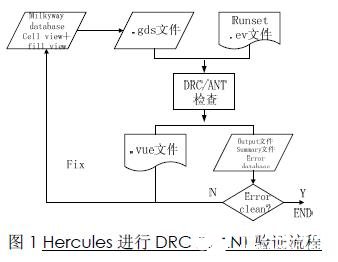

传统的物理验证主要包括设计规则检查(DRC),天线效应检查(ANT),版图一致性验证(LVS)和电气规则检查(ERC)四部分,本课题使用的工具是Synopsys公司的版图工具Astro和物理验证工具Hercules。Hercules拥有进行超深亚微米(UDSM)工艺验证的能力,可进行亿门级的微处理器和千万门级的ASIC的物理验证。通过更加高效的验证来缩短设计周期,并提供图形界面来帮助设计人员快速发现和改正违例错误。它可以和Synopsys公司的milkyway数据进行无缝连接,设计人员使用milkyway数据进行布局布线和版图优化。Milkyway是Astro工具的版图格式,它的设计单元称为cell,含有多种视图 (View),其中与物理验证关系密切的是CEL View和FILL View,CEL View含有实现逻辑功能的版图信息,FILL View含有进行可制造性设计(Design for Manufacturing,DFM)时插入的填充金属(metal filler)信息。本处的DFM是指对布线结束后的设计为了满足工艺制造性要求,根据天线效应规则、密度设计规则等进行的插入二极管,添加填充金属,放人fill单元等操作的总称。其中添加metal filler是为了满足覆盖密度要求而添加冗余的多晶硅或金属,结果是生成了对应cell的FILLView。FILL View在修复DRC错误及ANT错误后要及时进行调整,不然又会引入新的DRC问题。Astro进行物理验证时支持Hercules explorer和vue两种图形化界面工具,本课题使用的是vue界面,来对hercules发现的问题进行定位和修复。在脚本设置文件 (runset)文件中设定OPTIONS {CRE-ATE_VUE_OUTPUT=TRUE}生成.vue文件,在Astro中启动Hercules然后借助.vue文件就可以借助错误定位进行修改了。

在Hercules工具进行物理验证之前,可以使用Astro工具进行后端验证,先行检查Milkyway文件中存在的DRC和LVS错误并更正。Astro支持深亚微米工艺下在工艺文件中进行了定义的设计规则检查,使用命令geAdvDRC或者geNewDRC可以调用这一功能,工具会生成错误单元位置信息,在上面会标出可能出现问题的区域,便于更正。使用命令geNewLVS可以进行简单的LVS检查---连接性检查,可以发现版图中的断路或开路问题,同样也会生成一个错误单元位置信息方便改正。

2 物理验证组成

DRC,即设计规则验证,它要求设计的版图文件要满足多边形最小面积,同层以及不同层间多边形内部最小间距,外部最小间距,以及为了确保可制造性而进行的密度检查等。在物理验证阶段,为了消除DRC错误而进行手工改动时常常会引入新的错误。尤其是经过DFM后的设计,填充金属的引入会增加最小间距或最小面积等类型的错误,这些因金属填充产生的错误可在最后集中在FILL View中改完。

ANT是天线效应检查,这也是和电路制造过程有关的问题,为了防止太多的电子在铺金属层的过程中集中到导线上击穿栅极,必须保证同层的导线长度不能太长。解决天线效应问题有两种方法,一是在产生天线效应的走线上添加反向二极管,这样可以保护栅极;二是采用向更高层的金属进行跳线连接,这样在加工过程中就可以避免过多电子的积聚。在可制造性工艺之前,由于版图中没有加入填充用的金属,可以用第一种方法来加入二极管以消除天线效应,但在DFM之后的物理验证部分,已经很难再找到空闲的空间插人二极管,这时就应该使用第二种方法来解决天线效应问题。

就流程而言,DRC检查和ANT检查有相似之处,如图1所示。在使用Astro进行流文件输出得到CDSII文件后,根据实际设计的顶层模块名称和路径,对代工厂家提供的基于Hercules的DRC规则设置文件进行改动,如下例:

Header部分下面是检查时候一些选项的设置,还有层的定义以及规则的描述。设置好之后就可以运行He rcules进行DRC或ANT验证了。如果使用了正确的runset文件,得到的DRC错误一般是图形间距错误、宽金属间距错误,金属密度错误等,而ANT错误也会给出具体发生问题的走线名称,这样再在Astro里调用vue图形界面进行改错即可。

LVS是版图原理图一致性验证,用于比较两者晶体管级的连接是否正确,逻辑功能是否一致,其过程分两步:第一步,Hercules读入版图文件,从包含有器件及其相互间的连通性的版图数据库中提取出版图网表;第二步,Hercules读入版图网表和原理图网表,然后对照这两个网表的连接情况以确定它们是否一致。对照时,Hercules从电路的输入输出开始搜索,找到一个匹配节点后就给该匹配节点和器件赋以匹配状态值,当遇到不匹配的节点时,就停止该路径的搜索,直到所有的路径都搜索完毕,Her-cules将节点和器件的匹配结果写入输出文件,给出连接及匹配情况的报告,设计人员可以根据报告来改正不匹配的元件,LVS验证流程如图4所示。

进行LVS验证的设置较为复杂,除了与DRC类似的对foundry提供的runset文件进行设置外,还要提取verilog网表,进行网表转换(netTran)得到Hercules格式网表和对等文件(Equivalence File)。对等文件可以简化比较过程,比如文件中指定equiv dpram_8xlk=dpram_8xlk{}

Hercules在LVS比较的时候就直接比较用户指定的这些单元的版图和电路图的匹配性,而不比较其他的模块。运行Hercules生成结果后,查看结果文件并结合Astro进行改正。

3 物理验证流程

一般而言LVS与电气规则检查(ERC)的关系密切,ERC主要包括比如短路、开路、悬浮等,对于一个ERC检查通过的设计,LVS才真正可以检查出元件的连接问题。因此,ERC应该在LVS之前完成,需要注意的是Hercules的ERC检查可以集成在DRC和LVS检查中,以利于整体进行检查和改进。本课题所采用Smic18LG工艺的物理验证将ERC检查分别集成到天线效应检查和LVS的电气连接检查中。但一般而言,DRC,ANT与LNS则没有必然的先后顺序。根据工程经验,在修复ANT错误时,常常需要更改填充金属形状和位置,而这又会带入新的DRC问题,因此比较理想的做法是先修ANT错误,等检查通过后再进行DRC修复前面引入的设计规则违例,这样不但可以修复 DRC,而且可以为后面进行LNS尽可能的排除干扰,然后进行LVS,需要注意的是,LVS不涉及FILL View,即含有填充金属信息的版图层,而进行LVS时在提取版图参数阶段,如果含有填充金属信息会导致提取的参数文件过大,一致性比较时也会占用较多内存,因此可以使用不含FILL View信息的CDSII版图文件进行LVS初步检查,经比较并修改至检查通过时再使用含填充金属信息的GDSII文件提取参数并作最后的LVS,这时的结果会与前面类似,如果检查通过则可作最后的DRC检查,若结果显示没有违例则可进行最后的流片。物理验证流程如图5所示。

4 结论

本课题使用的服务器是浪潮服务器NL380G2,3.6G双核CPU,Xeon8G内存,进行验证的设计为二百万门级某型号调制芯片设计,工具为Her-cules2004.12。旧有的流程是按经验采用或先LVS或先DRC,而按照本文提出的流程在实际的设计中已经经过验证。

-

电路图

+关注

关注

10213文章

10645浏览量

510575 -

天线

+关注

关注

66文章

3037浏览量

139619 -

晶体管

+关注

关注

76文章

9049浏览量

135168

发布评论请先 登录

相关推荐

片上系统(SOC)设计流程及其集成开发环境

数模混合SOC芯片的可测性方案的实现

算法实现的VLSI结构

FPGA+CPU是顺应历史发展趋势吗?

SoC验证平台的FPGA综合怎么实现?

怎么利用CMOS工艺实现一个10位的高速DAC?

一种基于省时考虑的深亚微米VLSI的物理验证方法

VLSI设计的FPGA验证实验指导书

聚洵与琻捷电子强强联合,加快高端模拟芯片和车规级产品的研发

VLSI设计验证及其方法的重要性

基于深亚微米VLSI的物理验证可实现加快芯片研发速度

基于深亚微米VLSI的物理验证可实现加快芯片研发速度

评论