有的时候需要查找一些官网的例程进行学习和参考,但是总感觉无从下手,今天就教大家怎么利用官网和Vivado的Documention进行相关的操作。不清楚使用哪些IP或者不清楚需要参考哪个文档

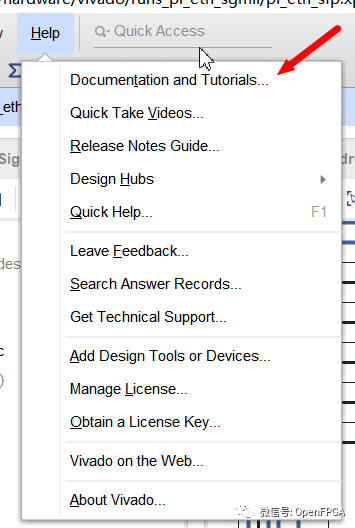

首先点击Help-->Documention and Tutorials就可以打开XIlinx Documention浏览器了。

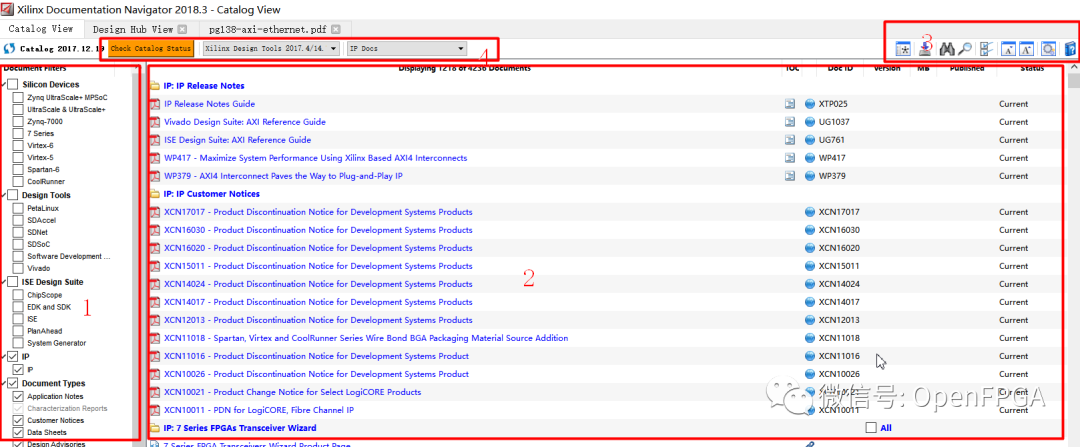

打开后如下:

主要分为:1、分类窗口;2、文件选择窗口;3、设置窗口;4、选择窗口;

可以在3窗口进行搜索。

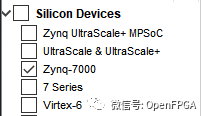

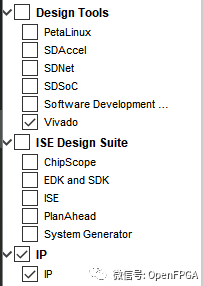

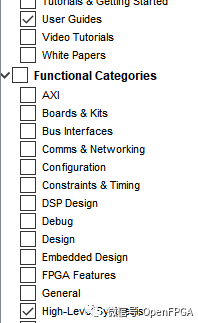

假如现在我需要查找一下7系列FPGA中关于HLS的使用,那么我可以通过1窗口进行分类选择,如下:

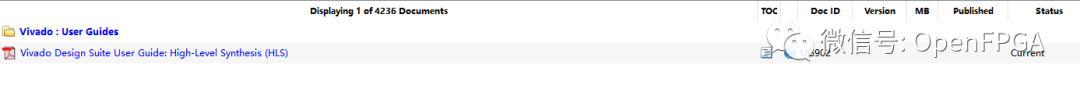

就可以在2窗口得到我想要的文档:

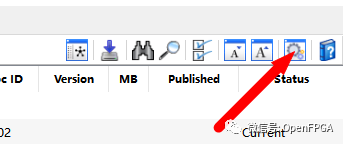

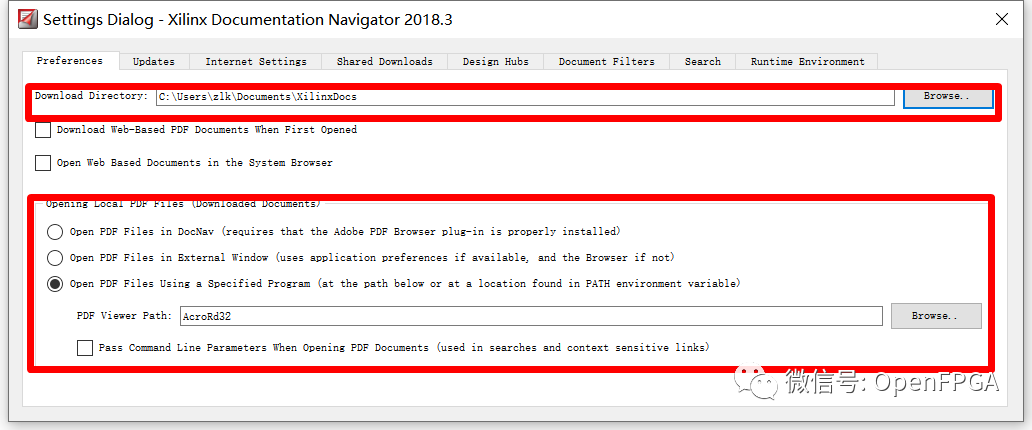

点击进去就可以阅读,如果想要下载也可以,这里可以进行两种设置,一是下载路径设置二是打开文档的阅读器设置,具体位置如下图所示:

可以按照自己的需求进行设置。找到了或者已知使用哪种或者哪个IP怎么下载例程

这里提供两种方式:

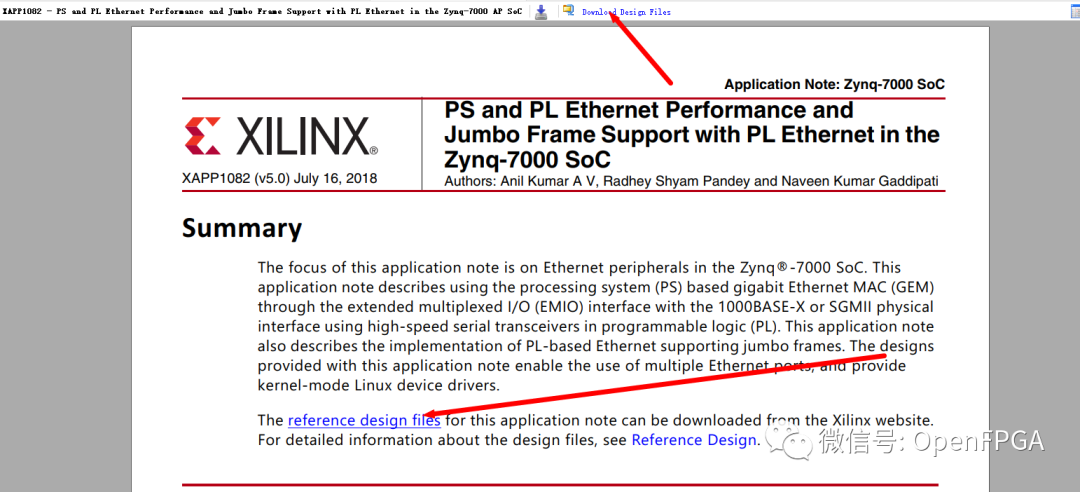

1、使用Xilinx Doc直接搜索相关的Doc,这里举例AXI ethernet,相关的应用手册是xapp1082(还有其他的参考,这里以比较常见的举例),直接搜索这个文档,打开后如下图所示:

这两个位置可以下载相关参考例程,直接点击下载即可,建议该文档直接使用Chrome打开,点击链接会知道跳转,其他PDF阅读器也可。

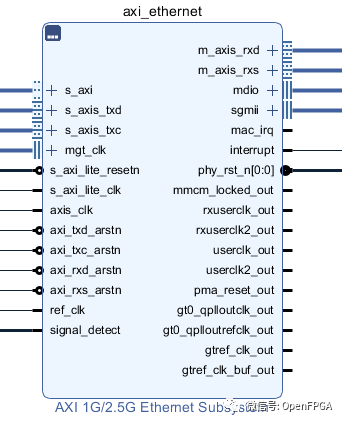

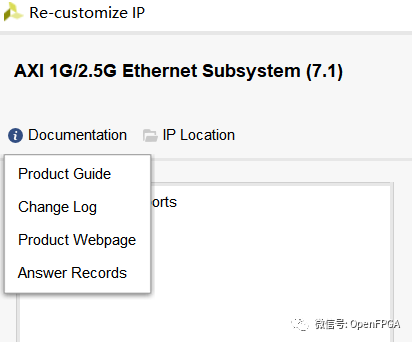

2、在IP管理器里找到该IP

双击进入

其中左上角的Documentation,有Product Guide等文档,其中Change Log(修改BUG记录)、Product Webpage和Answer Records都是比较重要的文档,对使用好该IP都有很重要的作用,因为与本篇文章不想关,这里就不展开描述了,点击Product Guide就能通过Xilinx Documentation打开这个文档,这个文档相当相当重要,包括整个IP的使用说明,每个参数的说明,时序相关,以及一些Debug,仿真相关说明,如果在使用该IP时出现问题,请仔细阅读该文档,同时该文档会提供参考示例链接(这个IP比较特殊,是两个IP结合在一起的,所以没有refence(疯狂翻车))。

怎么使用下载下来的参考设计

目前官网下载下来的参考例程异常“简单",主要通过TCL脚本提供,对于不熟悉使用该脚本的人可能会比较懵,但是不需要过于担心,只需要按照下面的步骤就可以轻松利用该脚本构建Vivado工程。

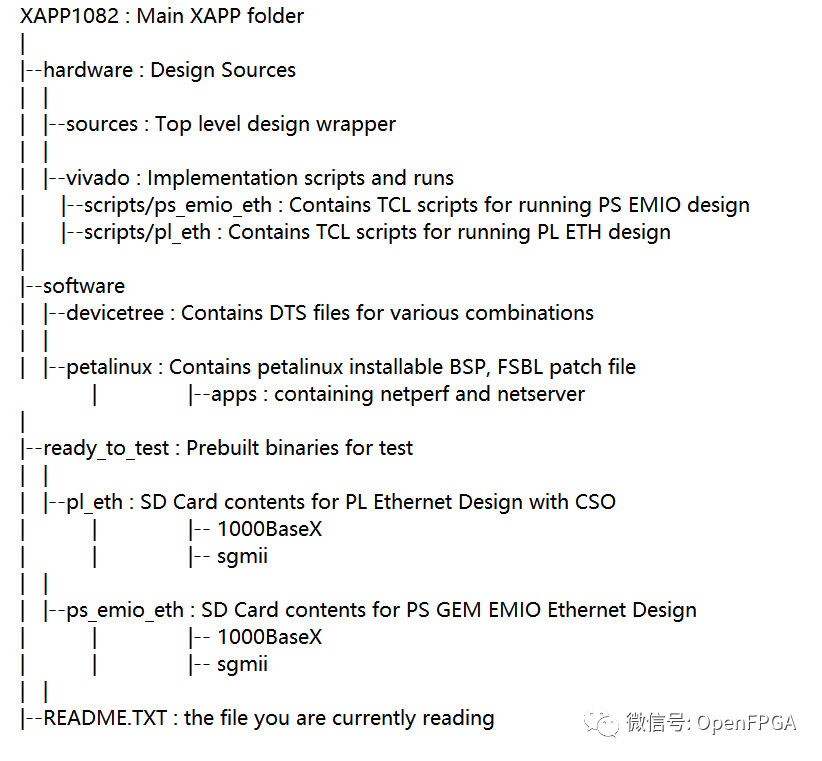

下载下来的参考文件一定要先阅读readme文件,里面包含了整个例程的作用和文件构成,以XAPP1082为例如下:

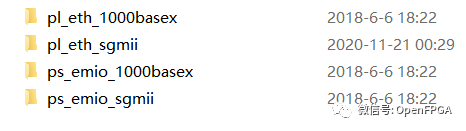

进入到xapp1082xapp1082_2017_4hardwarevivadoscripts文件夹下,可以看到四个例程:

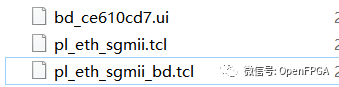

作用就不展开描述了,随便进入一个文件夹下:

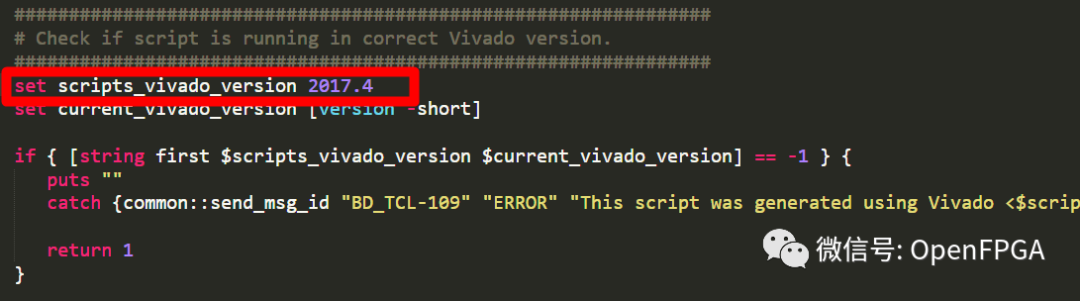

里面只用三个文件,总大小不足100k(要是一个完整的工程,至少要100M左右,所以TCL的作用不言而喻),进如这个文件夹主要想要确认下导出该脚本的Vivado版本(不确认的话,后期运行会报错),外层文件夹已经有相关的版本说明了(xapp1082_2017_4)打开pl_eth_sgmii_bd.tcl(记事本及相关文本阅读器都可以):

如果你的Vivado版本和这个一样,那么不需要修改,如果不一样请修改和你的版本一样,我使用的是Vivado2018.3,修改如下:

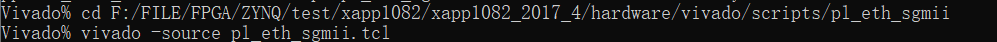

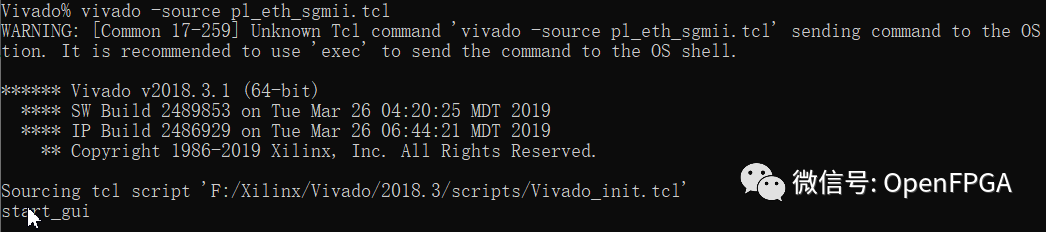

接下来打开Linux terminal or Vivado tcl shell in windows

通过CD命令进入历程所在的文件夹:

注意这里是“/”不是WIN系统常用的“”,之后执行:

vivado -source pl_eth_sgmii.tcl

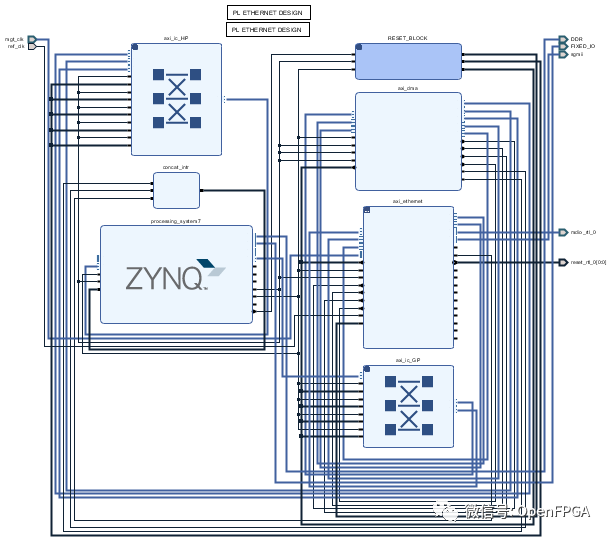

就可以打开Vivado并自动构建Demo了:

这里说明一下,我使用的Vivado版本和例程版本不相同所以构建完成后会有一些小Bug,按照提示修改即可。

构建的工程保存在如下路径:

责任编辑:xj

原文标题:【Vivado那些事】如何查找官网例程及如何使用官网例程

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

-

IP

+关注

关注

5文章

1399浏览量

148262 -

Vivado

+关注

关注

18文章

787浏览量

65089

原文标题:【Vivado那些事】如何查找官网例程及如何使用官网例程

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何禁止vivado自动生成 bufg

使用AD9914进行相位纠正功能的疑惑求解答

使用Vivado高层次综合(HLS)进行FPGA设计的简介

Vivado设计套件用户:使用Vivado IDE的指南

Vivado Design Suite用户指南:采用IP进行设计

Vivado使用指南

用 TCL 定制 Vivado 设计实现流程

Vivado综合参数设置

在Vivado中实现ECO功能

怎么利用官网和Vivado的Documention进行相关的操作

怎么利用官网和Vivado的Documention进行相关的操作

评论