前言

同事完成了一个PCB的设计,准备要发板了打样了,于是他组织了PCB评审会议,让硬件同事一起参加讨论,给出建议。评审开始后,大家纷纷开始讨论,各抒己见,有的提出了哪条线要如何如何走才好看,有的提出了这个器件布局不好,要怎么怎么放才好,有的提出了这个时钟线要做包地处理,有的提出来了这根线走得有点细,需要过大电流……

我的建议

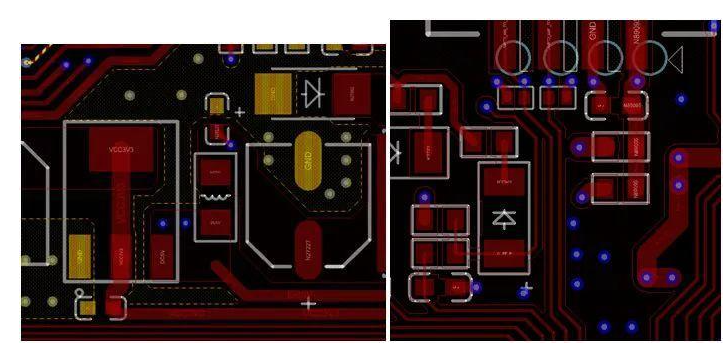

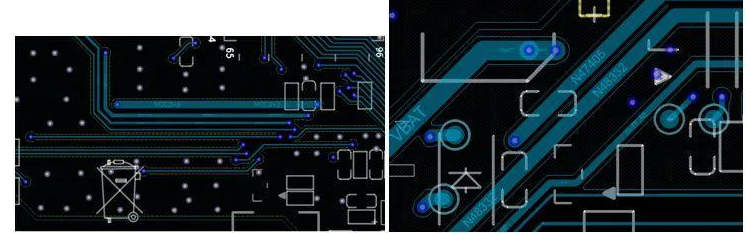

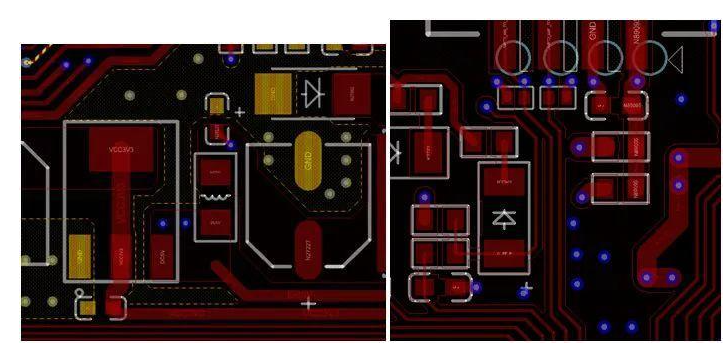

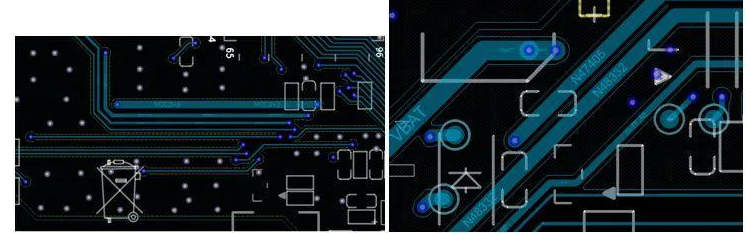

我仔细看了看,发现他的PCB的铺铜存在有些严重的问题,很多地方的地网络的铜呈现条形状,其中一端跟大地连起来,另外一端却是悬空的,没有和其他附近的地连通,也没有打孔和地层连接,这个PCB是一个四层层板,顶层和底层是元器件与信号层,第二层是地平面层,第三层是电源平面。所以只要能打过孔,就能和地平面连接上了。如下面的图所示。

从上面的图可以看到很多条形的地,夹于两根线之间。如果不理会这些条形的地,有没有问题呢?在高速电路板中,这种一端悬空的条状的地,会等效成天线,产生天线效应,向空间辐射,最终EMC测试可能通不过。

解决方法

我在会上提出了这个问题,建议优化这些铺铜。优化方法有,1,调小走线的间距,不让地铺进去。2,设置禁止区,不让地铺进去。3,调大走线的间距,让地铺过去,和旁边的地连起来。4,在条状的地的末端打过孔下到地平面层,让它和地平面连起来。

编辑:hfy

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

相关推荐

。减小差模干扰的主要方法是布线时尽量减短走线长度, 减小信号环路面积。2.2 PCB电路板上干扰源产生方式高速数字电路各类干扰的主要产生原因是由电源自身固有噪声频率及外部线路上各类变化

发表于 07-16 11:50

`altium3D显示时候只有元件和走线 没有电路板怎么处理啊?原来是有绿色电路板的,不知道怎么回事就变成黑色的只有器件和走

发表于 09-17 11:04

`用altium 画PCB 对称电路时走线没有走对称,看起来有点别扭。像这种对称电路走

发表于 01-07 11:20

是高速信号并产生传输线效应。因此必须避免传输线效应,防止原逻辑电路信号被叠加或相抵消而改变。2.1.2 严格控制关键网线的走线长度 如果

发表于 08-29 16:36

。由于电源层遍及电路板的全面积,因此直流电阻非常小,可以有效地降低噪声。 2.同类型信号线的分布 在设计PCB板时,对于处理器的输入/输出信号中的数据

发表于 09-05 16:38

嗨,我想知道电路板走线的延迟,很难测量横截面来计算C或L.所以我可以使用两个微探针(已知长度)并在迹线上放置微探针和另一个例如,如果我想测量迹线的电容,它会去哪里?我没有时域,所以是否可以在VNA

发表于 10-10 17:14

John Ardizzoni尽管其在高速电路中具有重要性,但印刷电路板(PCB)布局通常是设计过程中的最后步骤之一。

发表于 10-23 17:11

,要求每个电路模块尽量不产生电磁辐射,同叫又具有一定的抗电磁干扰的能力,以使系统达到相对的完全兼容。3 高速电路电磁兼容性设计3.1 高速PCB的叠层设计

发表于 11-26 16:54

上使用多个过孔,过孔会产生阻抗不匹配和电感。 图2PCB上的差分对走线 以前,只有不到50%的电路板采用可控阻抗互连线,而现在这一比例已超过90%。如今有不到50%的电路板使用了差分

发表于 11-27 10:56

蛇形走线,因为应用场合不同而具不同的作用:(1)如果蛇形走线在计算机板中出现,其主要起到一个滤波电感和阻抗匹配的作用,提高电路的抗干扰能力。

发表于 03-22 06:20

和阻抗匹配的作用,提高电路的抗干扰能力。计算机主机板中的蛇形走线,主要用在一些时钟信号中,如PCI-Clk,AGPCIK,IDE,DIMM

发表于 05-09 07:35

1.高速信号仿真电路基础2.高速信号仿真工具基础3.三大实例练习(1)电路板仿真设置、AuditSL、AllegroSigritySI等(2)Sigrity平台相关工具信号分析、信号反

发表于 03-09 10:57

硬件工程师做久了自然有自己处理电路板的一套方法,也许不是最好的办法,自己却能理解其中的意义。但是工作中还是要按照最完美的办法进行操作,本期我们就来了解一下关于高速信号走

发表于 10-30 08:33

,美工刀或手术刀,遮蔽胶带(如果切割的走线很长),和一些薄铜箔。

识别切割痕迹

使用放大镜或显微镜仔细检查柔性电路板并识别切割/断裂的痕迹。切割走线可以识别为

发表于 07-31 16:01

高速电路板中哪条线要如何如何走才好看

高速电路板中哪条线要如何如何走才好看

评论