设计背景:

IIC 简单来说,就是一种串行通信协议,IIC 的通信协议和通信接口在很多工程中有广泛的应用,如数据采集领域的串行 AD,图像处理领域的摄像头配置,工业控制领域的 X 射线管配置等等。除此之外,由于 IIC 协议占用的 IO 资源特别少,连接方便,所以工程中也常选用 IIC 接口做为不同芯片间的通信协议。

设计原理:

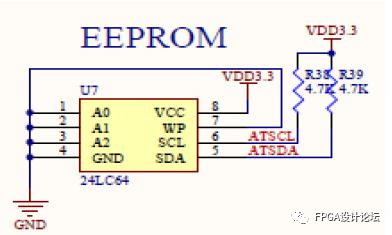

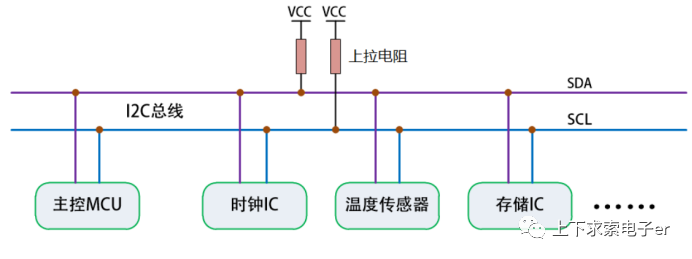

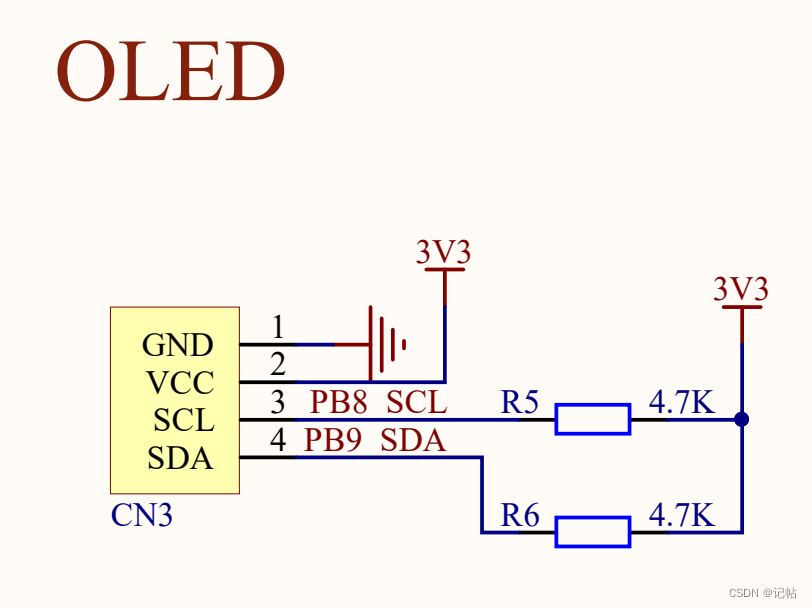

IIC 电路原理图如下:

24LC64 各引脚定义:

1、A0,A1,A2 为 24LC64 的片选信号,由于 IIC 总线可以挂载多个 IIC 接口器件,所以每个器件都应该有自己的“身份标识”,通过对 A0,A1,A2 输入不同的高低电平,就可以设置该 EEPROM 的片选信号。

2、WP 为读写使能信号,当 WP 悬空或者接地,EEPROM 可读可写,当 WP 接电源,EEPROM 只能读不能写。

3、SCL 为 IIC 接口的时钟线。

4、SDA 为 IIC 接口的数据线。

IIC 接口的读写时序:

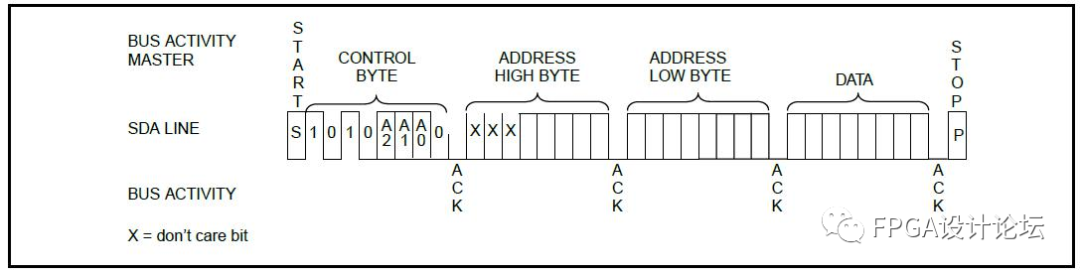

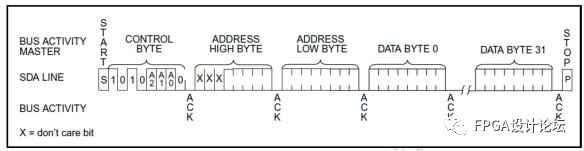

IIC 接口读写时序分为随机读写(单字节读写)和页面读写(多字节读写),先分析随机读写(Byte Write/Read)时序。Byte Write 时序如下:

时序解读:如果我们要向 EEPROM 写入一个字节,那么必须经过以下步骤:

1. 发送启动信号

2. 发送控制字

4. 发送高字节地址位

5. 接收并检测 EEPROM 发来的应答信号 ACK

6. 发送低字节地址位

7. 接收并检测 EEPROM 发来的应答信号 ACK

8. 发送 8bit 有效数据

9. 接收并检测 EEPROM 发来的应答信号 ACK

10.发送停止信号

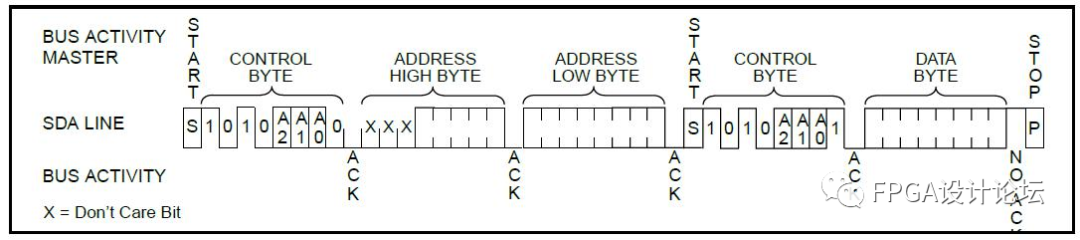

Byte Read 时序如下:

时序解读:如果我们要从 EEPROM 读出一个字节,那么必须经过以下步骤:

1. 发送启动信号

2. 发送控制字 1010_A2A1A0_0

3. 接收并检测 EEPROM 发来的应答信号 ACK

4. 发送高字节地址位

5. 接收并检测 EEPROM 发来的应答信号 ACK

6. 发送低字节地址位

7. 接收并检测 EEPROM 发来的应答信号 ACK

8. 发送启动信号

9. 发送控制字 1010_A2A1A0_1

10. 接收并检测 EEPROM 发来的应答信号 ACK

11. 读取一个字节数据

12. 发送 NO ACK 信号

13. 发送停止信号

接下来则需要分析各步骤具体意义:

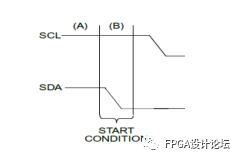

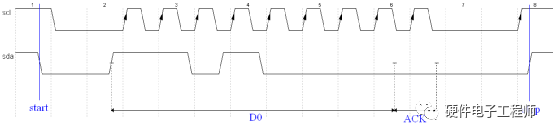

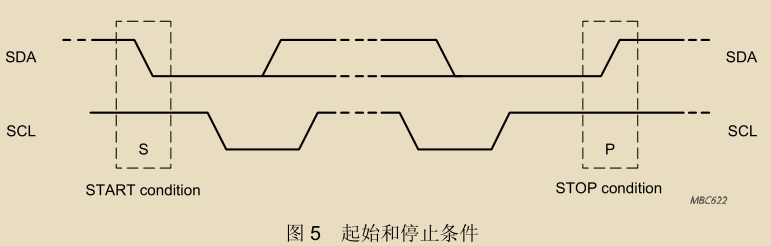

1.启动信号

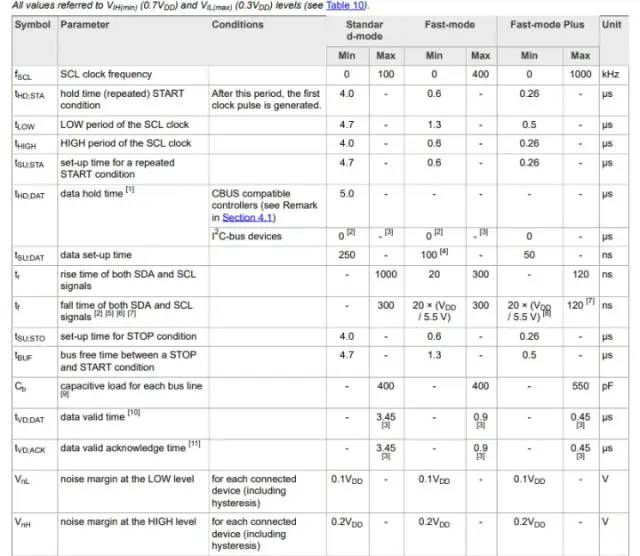

在 SCL 保持高电平期间,如果 SDA 出现由高到低的跳变沿,代表启动信号

2. 控制字

我们的控制字为 1010_0000,其中 1010 为 EEPROM 的型号标识,为一组固定的序列,紧接着 A2,A1,A0 就是我们的片选信号,最后一位为读写控制位,低电平代表写,高电平代表读,我们这里首先需要对 EEPROM 写入地址位,所以我们最后一位为 0。

3. 高/低位地址

由于 24LC64 有 64Kbit 的存储空间,所以我们需要 13 位的地址位宽才能寻址所有的存储空间,由于 IIC 协议规定只能以字节形式写入,所以必须将 13 位的地址扩展为 16 位的地址,分为高八位和低八位,多出来的前三位填充任意数据即可,对我们的寻址地址没有影响。

3. 停止信号

4. 应答信号 ACK

应答信号是由数据接收方发出的,当 SCL 为高电平期间,如果监测到 SDA 为低电平,说明有应答信号。

5. 非应答信号 NO ACK

非应答信号也是由数据接收方发出的,当 SCL 为高电平期间,如果 SDA 为高电平,说明有非应答信号。

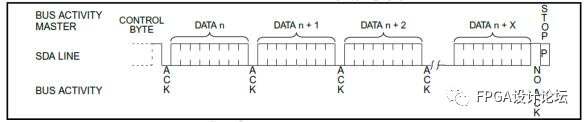

说明:由于 IIC 总线协议启动和停止信号都是在 SCL 高电平期间发生跳变,这就决定了我们其他数据的改变只能发生在 SCL 低电平期间,在 SCL 为高电平期间,数据必须保持稳定。即在 SCL 低电平改变数据,在 SCL 高电平采集数据。相比于单字节读写,页面读写只是增加了几个状态,具体时序如下,这里和后面的设计代码不做详细论述。

Page Write 时序如下:

Page Read 时序如下:

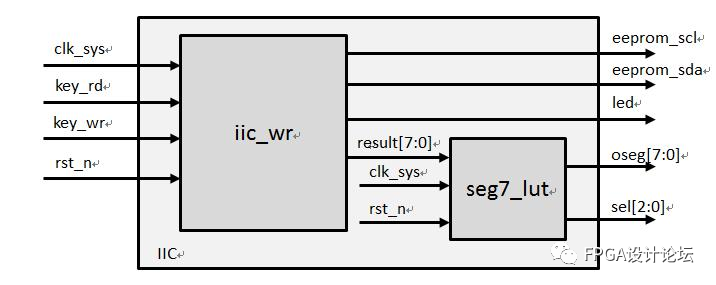

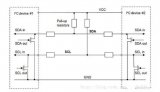

设计架构图:

本设计用两个按键控制 EEPROM 读写,当写按键按下时,向EEPROM 某一固定地址写入一个字节数据,当读按键按下时,将该地址数据读出,并显示到数码管,LED 灯是一个标志信号,LED 亮说明数据写入完毕。设计架构如下:

设计代码:

iic_wr 模块代码:负责进行 IIC 数据的读写

seg7_lut 模块代码,负责数码管显示

IIC 顶层模块代码:

tb 顶层测试模块代码:

仿真图:

随机读写,仿真写时序:

随机读写,仿真读时序:

在仿真时,需要将检测应答的状态跳过,直接向下一状态跳转,观察读写时序,当读写按键按下时,都会产生对应的动作。

责任编辑:lq

-

FPGA

+关注

关注

1602文章

21309浏览量

593124 -

IIC

+关注

关注

11文章

285浏览量

37795 -

工业控制

+关注

关注

36文章

1274浏览量

85449

原文标题:FPGA入门课程《基于 FPGA 的 IIC设计》

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA实现IIC协议的设计

用FPGA通过IIC总线配置ADV7391出色条测试画面,总是不成功怎么解决?

STM32基础知识:IIC概述与软件模拟IIC

用面向对象思想封装IIC、AT24C64驱动

IIC总线学习笔记

iic的时钟信号哪里来的?

fpga入门的基础知识 FPGA零基础学习IIC协议驱动设计

基于STM32和HAL库创建一个IIC设备

IIC总线调试故障具体原因的定位过程及解决方法

IIC总线的FPGA实现原理及过程

《基于FPGA的IIC设计》

《基于FPGA的IIC设计》

评论