随着信息化产业的不断推动,数字信号传输的速度越来越快,频率越来越高,传统设计的PCB板已经不能满足这种高频电路的需要。信号的完整性传输研究成为越来越关键的重要核心技术。当电路信号的频率增加到一定高度后,PCB中的导通孔PTH中无用的孔铜部分,其多余的镀铜就相当于天线一样,产生信号辐射对周围的其他信号造成干扰,严重时将影响到线路系统的正常工作,Backdrill的作用就是将多余的镀铜用背钻的方式钻掉,从而消除此类EMI问题。在降低成本的同时,满足高频、高速的性能。

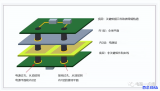

背钻其实就是一种特殊的控制钻孔深度的钻孔技术,在多层板的制作中,例如8层板的制作,我们需要将第1层连到第6层。通常首先钻出通孔(一次钻),然后镀铜。这样第1层直接连到第8层。实际我们只需要第1层连到第6层,第7到第8层由于没有线路相连,像一个多余的镀铜柱子。这个柱子在高频高速电路设计中,会导致信号传输的反射、散射、延迟等,给信号带来完整性方面的问题。所以将这个多余的柱子(业内叫STUB)从反面钻掉(二次钻)。因此叫背钻。

镀铜短线柱(STUB)如何影响高速信号?

Stub即镀铜短线柱,如上图所示。没有连接信号线的通孔镀铜部分。下图所示为两种通孔结构的信号传输时电平转换眼图。左边是具有完整的Stub镀铜短线柱,右边的是Stubless没有镀铜短线柱的情况。可以看出,通孔镀铜短线柱在Pedestal Width这段区域其Pedestal Height消隐脉冲高度处于逻辑0到1和逻辑1到0转换中的不确定状态。这些不确定电平翻转区域,使得数字接收更难以确定接收的信号到底是逻辑1还是逻辑0。不确定逻辑状态的电平值与Stub镀铜短线柱的等效阻抗成比例。较高的通孔短线柱阻抗使得逻辑电平更接近于期望的低电平0和高电平1。因此逻辑电平翻转状态更为明确。如右图所示,类似于眼图的眼睛张开的范围更大。增加短线柱阻抗的有效方法是通过去除非功能焊盘来减小并联电容。虽然这些技术有所帮助,但它们通常不足以将失真减少到可接受的水平。

不确定电平翻转的区域宽度与短线柱的长度成比例。越短的短线柱Stub产生的不确定区域宽度越窄。减小不确定电平翻转区域宽度的简单方法是通过背钻来减小通孔镀铜柱的总长度。下图所示为进行了适当背钻的通孔PTH的眼图。可以容易地看出,在背钻操作之后剩余的镀铜短线柱长度(在眼睛的左上角和左下角的不确定区域减小),类似于张开的眼睛范围更大,确定电平转换正常工作区间更大。

应当注意的是,采用构造技术(例如激光钻孔和改变板层堆栈顺序)使得导线被移动到更靠近过孔短线柱端部的层,也可以用于减小短线柱长度。但在许多高密度PCB板和背板/中间板中,从制造和成本核算的角度来看,这些方式并不总是可行的。在这种情况下,唯一的选择是通过backdrilling背钻删除via stub。当然,短线柱Stub去除不是唯一可以应用于通孔的信号完整性改进技术。使用例如正在申请的专利技术,Sanmina-SCI的Opti-Via TM“通孔调谐”算法来优化未经背钻的通孔的剩余部分也可以进一步减少通孔引起的信号失真。

背钻孔有什么样优点和作用?

影响信号系统信号完整性的主要因素除设计、材料、传输线、连接器、芯片封装等因素外,导通孔对信号完整性有较大影响。而背钻通过钻掉没有起到任何连接或者传输作用的通孔段,避免了多余Stub对信号完整性的影响。除此之外,背钻技术还有如下诸多优点。

减小杂讯干扰;

提高信号完整性;

局部板厚变小;

减少埋盲孔的使用,降低PCB制作难度。

背钻制作工艺流程

根据提供PCB,对PCB进行一钻定位并进行一钻钻孔;背钻的一钻孔偏会加大背钻孔与一钻孔对准度差异,对背钻精度造成较大影响,此处必须严格控制一钻孔位精度。

对一钻钻孔后的PCB进行电镀。此处孔铜不够的话,会严重影响要求。需采用低电流,长时间,一次性镀够。电镀后切片监控铜厚。电镀参数:15ASF×(48min+48min)。

采用钻刀对需要进行背钻的电镀孔进行背钻,二钻钻孔。背钻是利用钻机的深度控制功能实现盲孔的加工,以去除部分孔铜。其公差主要受到背钻设备精度和介质厚度公差的影响。

对整孔进行数值塞孔。背钻孔有一头大、一头小且有拐角的特点,理论上更容易产生气泡空洞,需要进行有效塞孔。

对塞孔处理后的板面进行处理。消除残留。由于铜面和树脂硬度有很大差异,需要保证磨板后板面平整。

背钻孔板技术特征有哪些?

背钻技术使用的情况比较特殊。要求也很复杂。通常应用与信号通信设备,大型伺服器,医疗电子,军事,航空航天等重要领域。这里领域有专业和深厚的技术储备和研发力量,需要进行高端技术和产品设计。通常来说,背钻孔板有如下技术特征。

多数背板是硬板

层数一般为8至50层

板厚:2.5mm以上

厚径比较大

板尺寸较大

外层线路较少,多为压接孔方阵设计

背钻孔板设计需要遵循的规则

一般首钻最小孔径>=0.3mm

一次钻的钻孔孔径推荐要求不低于0.3mm。如下图所示,首钻钻孔孔径用A表示。

背钻孔通常比需要钻掉的孔大0.4mm

背钻钻孔孔径一般推荐比一次钻孔径大0.25mm~0.4mm。保险起见推荐大0.4mm。如下图所示,背钻孔径用B表示。

背钻深度控制冗余0.2mm

背钻是利用钻机的深度控制功能实现的。由于背钻的钻刀是尖状的,钻到相应的层时由于钻刀的倾斜角总会保留有一小段余量。该背钻深度控制建议至少保留8mil即0.2mm。而且,在层叠设置的时候需要考虑介质厚度,避免出现走线被钻断的情况。如下图所示,背钻深度冗余用S表示。

如果背钻要求钻到M层,那么与M层相邻未被钻掉的层之间介质厚度最小0.3mm

背钻与走线间距

背钻孔的stub钻掉层走线与背钻的距离推荐不小于10mil(0.25mm)。如下图所示,虚线框圆圈距离背钻孔外沿的距离为10mil,在虚线框外都是安全的走线区域。

Altium Designer中如何设置背钻参数?

前面介绍了背钻技术以及背钻设计时需要考虑的参数。那么在Altium designer中该如何进行背钻设计中各参数的设置呢?下面用一具体案例来展示Altium Designer中进行背钻设计的方法。

步骤1:设置钻孔层对

首先打孔走线。比如一个8层板,从顶层Toplayer打孔,然后切换到Midlayer1上来走线。剩下的Midlayer2 到底层bottomlayer需要背钻Backdrilling。此处第一步就是在Design- Layer Stack Manager - Drill Pair 中设置。如下图所示,起始层Midlayer2,终止层Bottomlayer。切记要勾选Back drill pair选项框表示它是做背钻用的。

步骤2:确保信号层Midlayer1与背钻起始层Midlayer2之间层间距不小于0.3mm。

此处在层厚Thickness栏目,经检查满足要求。

步骤3:确定背钻孔需要钻掉的镀铜柱长度。

通过Layer Stack Manager中从Midlayer2到Bottomlayer之间的层厚加起来大概1mm左右。由于考虑到背钻深度控制冗余8mil(0.2mm),在层栈管理器页面Midlayer1与Midlayer2之间的层厚正好0.254mm介质厚度。因此可以设置需要钻掉的镀铜柱为1mm左右。当然这个数值需要根据工程师具体设计中根据要求可适当增减。

步骤4:设置背钻大小,深度以及网络。

如下图所示,在设置Max Stub Length及需要钻掉的镀铜柱深度为1,mm。设置背钻孔大小为比原通孔大小半径大0.2mm。使得背钻孔与原通孔孔径大0.4mm。再设置需要背钻的过孔网络即可完成背钻相关的规则设置。

最终的效果在Altium Designer中3D显示如下图。

责任编辑:lq

-

PCB板

+关注

关注

27文章

1368浏览量

50307 -

PCB设计

+关注

关注

392文章

4565浏览量

83111 -

高频电路

+关注

关注

12文章

204浏览量

35369

原文标题:规则设置如何应用于我的PCB设计?—Back Drill背钻孔

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何检测复杂的超高速调制光信号?

有想过吗,高速信号隔直电容为什么是几百NF量级的?

浅谈Via stub在DDR4并行链路上的表现

pcb高速信号知识科普

pcb上的高速信号需要仿真串扰吗

底层镀铜在PCB制造中的角色和使用条件

高速信号的走线闭环规则

镀铜短线柱(STUB)如何影响高速信号?

镀铜短线柱(STUB)如何影响高速信号?

评论