一、高速ADC

1.背景知识

随着计算机技术、通信技术和微电子技术的高速发展,大大促进了ADC技术的发展,ADC作为模拟量与数据量接口的关键部件,广泛应用于各领域,在信息技术中起着重要作用。ADC同计算机一样,经历了低速到高速的发展过程。ADC的低速(转换时间大于300uS )结构有积分型、斜坡型、跟踪型;ADC的中速(转换时间在1uS-300uS )结构有逐次逼近型;ADC的高速(转换时间小于1uS)结构有闪烁型、分区式以及高分辨率结构的∑-△型。这些不同的结构满足了实际应用的广泛性和多样性的需求,其中高速ADC已成为决定诸如雷达、通信、电子对抗、航天航空、导弹、测控、地展、医疗、仪器仪表、图像、高性能控制器及数字通信系统等现代化电子设备性能的重要环节。

2.基本原理

目前的高速ADC主要采用了以下两种结构形式。一种是全并行结构,也叫Flash结构。这种结构的ADC至少有2“-1个比较器,例如,一个八位ADC就至少有255个比较器。当ADC分辨率增加时,不仅电路体积庞大,而且功耗猛增,也易出现“火花码’,,因而一般用于分辨率较低的ADC,如六位、八位ADC.另一 种 结 构形式称为分区式结构或折叠式结构,如两步法、多步法。其电路结构主要包含了S/H(或T/H)放大器、Flash A/D转换器、时标电路及数字误差校正电路等。分区式结构ADC克服了纯Flash结构ADC随着分辨率增加,电路体积庞大、功耗猛增的缺点但又带来另一个问题,即差分放大器和其中与第二次转换处理输入电压有关的电路引入的误差,这些误差将超过转换器允许的误差,因此必须引入数字误差校正。

当前又有一种名为“流水线”的结构,它也是基于Flash结构的多步转换结构(分区式),它是SAR和Flash两种相结合的一种结构。这种结构实际上是牺牲ADC的速度来换取精度,因此适于较高精度的高速ADC.

二、流水线ADC结构

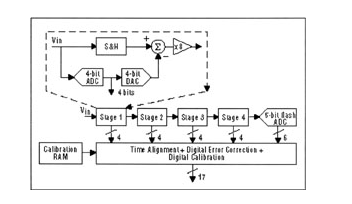

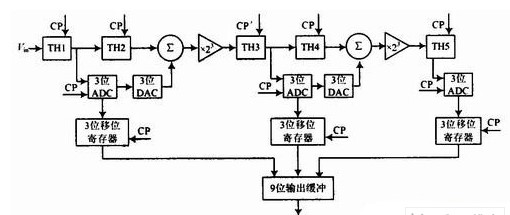

下图为12位流水线ADC的结构图。输入Vin首先被采样/保持(S&H)电路所采样,同时第一级的闪速ADC把它量化为3位,此3位输出送给一3位的DAC(具有12位精度),输入信号减去此DAC的输出,放大4倍送给下一级(第二级),继续重复上述过程,每级提供3位,直到最后一级4位闪速ADC。对应某一次采样,由于每级在不同的时间得到变换结果,因此在进行数字误差校正前用移位寄存器对各级的结果先按时间对准。注意只要某一级完成了某一采样的变换,得到结果并把差值送给下一级,它就可以处理下一个采样。因此流水线操作提高了处理能力。

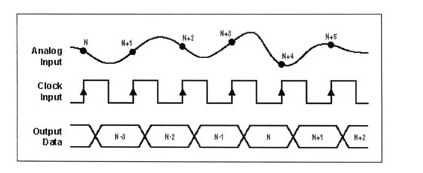

1. 延迟时间

由于每个采样必须通过整个流水线才能得到数字误差校正所需的各个位,因此流水线ADC有数据延迟。在图1的例子中,大约要延时3个周期(见下图)。

2. 数字误差校正

大多数现代流水线ADC采用“数字误差校正”技术来大大降低对闪速ADC(即内部的每个比较器)的精度要求。3位的差值输出其动态范围是输入信号Vin的1/8,然而随后的增益只有4,因此给第二级的输入只有第二级ADC 3位范围的一半(在第一级的3位变换没有误差的情况下)。

如果第一级的3位闪速ADC的某一个比较器有很大的失调,同时输入电压又正处于此比较点上,那么就会产生不正确3位码和不正确的3位DAC输出,此时产生了不同的差值。可以证明,只要放大后的差值没有超出后续的3位ADC的范围,以后产生的LSB码加上前面不正确的3位MSB码同样能产生正确的ADC结果。实际上,四级流水线中的第一级3位闪速ADC只需4位的精度。数字误差校正不能修正最后4位闪速转换器产生的误差。但是,这里产生的任何误差要除以前面的累积增益(44),因此只要求最后一级的精度大于4位。

在本节第一张图的例子种,虽然每级产生3位,但由于级间的增益是4,每级(第一级至第四级)的有效分辨率为2位。额外的位只是用于使尾数减半,使下一级3位ADC有额外的范围进行数字校正。这种方法被称之为级间“1位重叠”。因此整个ADC的有效位数是2+2+2+2+4=12位。

3. 元件精度

数字校正不能修正每个DAC和增益放大器的增益和线性特性。特别是前端的采样保持电路,DAC需要12位的精度。但是随后各级的元件只需较低的精度(如,第二级10位精度,第三级8位,等等),因为他们的误差要除以前面的级间增益。通常利用这一事实把流水线逐级做小来进一步降低功耗。

在大多数采用CMOS和BiCMOS技术的流水线ADC中,采样/保持、DAC、加法器和增益放大器通常用乘法DAC(MDAC)的单开关电容电路来实现。限制MDAC精度的主要因素是内在的电容不匹配。纯双极型实现方法更加复杂,主要受电流源DAC和级间增益放大器中电阻不匹配影响。通常12位或更高精度都需要阻容修正和数字校正,特别是第一级。

4. 数字标定

MAX1200/MAX1201/MAX1205系列(16位1Msps、14位1Msps和2Msps ADC)采用数字标定来保证其优越的精度和动态性能。MAX1200系列是CMOS流水线ADC,它由四级4位(其中一位重叠)和最后的5位闪速ADC构成,总位数是3+3+3+3+5=17位(参见图3)。额外的1到3位是数字标定用来量化误差项来达到更高的精度,舍掉它们后,最后得到14位或16位的精度。

标定从第三级的MDAC开始。第三级以上的MDAC误差已经足够小,不必标定。第三级的输出经剩余的流水线ADC数字化后,误差项存入片内的RAM中,第三级标定后,就可以用同样的方式由第三级来标定第二级,同样,第二级标定后,再标定第一级。为了使标定免受噪声的影响,采用取平均的方法(特别是第一和第二级的MDAC)。在正常转换期间,从RAM中取出标定的误差项来调整数字误差校正后的输出结果。

责任编辑人:CC

-

adc

+关注

关注

95文章

5648浏览量

539413 -

流水线ADC

+关注

关注

0文章

3浏览量

1819

发布评论请先 登录

相关推荐

流水线ADC结构解析 流水线ADC和其它ADC的比较

流水线ADC

流水线ADC的行为级仿真

采用三级流水线结构的9位100 MSPS A/D转换器的设计

了解流水线型ADC

一文详解流水线ADC结构

一文详解流水线ADC结构

评论