精密制造交接

另一个常见的挑战是在制造之前进行验证签核所需的时间。避免这种瓶颈及其相关影响的一种行之有效的方法是实施一种集成且连续的验证过程和方法,以使最终的验证签字过程得到控制和管理。这意味着提供通过铸造厂或OSAT的加工规则(PDK或PADK)的无制造错误的制造和装配数据。目标和挑战是在第一阶段中实现这一目标。

消除迭代需要设计环境具有满足流程规则的能力和特征,而又不依赖于可能会需要多次设计旋转才能达到切换标准的命中或未命中的手动方法。为了避免多次修改设计以通过制造商的规则,自动化是强制性的。

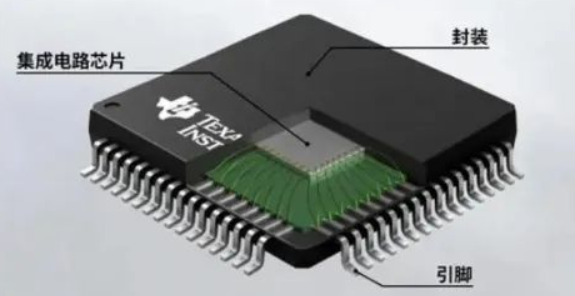

先进的IC封装几乎总是使用GDSII制造的。制造商,铸造厂或OSAT将通过此GDSII文件来验证是否符合其制造规则和约束,这当然会导致一个常见的难题:GDSII文件是从设计工具的本地CAD数据库进行后处理的,这就是问题可能发生并且确实发生的地方。

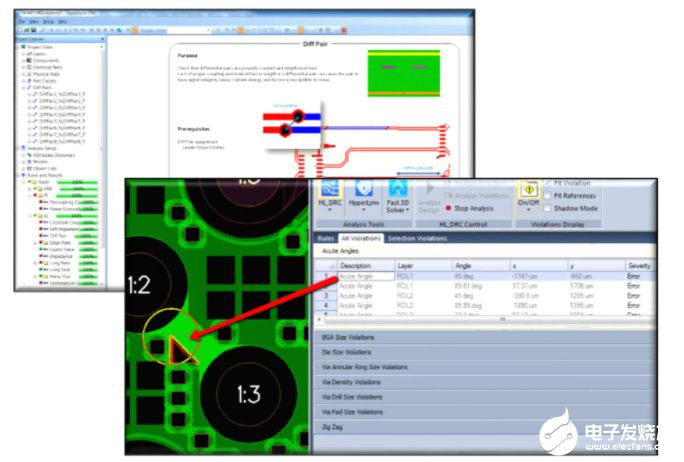

图5如果要避免重新旋转,精确创建制造定义的结构至关重要。资料来源:Mentor Graphics

无论您的CAD设计工具能生产出满足制造商制造规则的几何形状的好坏,都是将后处理衍生的GDSII用于签收,这就是当今大多数IC封装CAD设计工具的致命弱点。尽管CAD中的实际设计可以通过,但由于几何图形后处理质量差,因此生成的GDSII很少这样做,这通常导致设计旋转,因为设计人员难以获得可接受的GDSII。

金色签到

对于高级IC封装,黄金签收需要进行全面的检查,否则组装后的器件总产量将无法达到目标,并且会超出预计的组装和测试成本。全面的金色签字至少应包括物理验证,连接性检查(aka LVS)和异构程序集级别的验证(aka LVL)。这种全面的签核检查过程可以突出显示许多需要重做的问题。如果没有发现,这些问题很容易导致项目延误,增加成本并导致错过制造计划。

防止这种情况发生的一种方法是实施“左移”设计流程,该流程在设计中执行,以查找并消除明显的签核错误。使用这种方法可以消除80%以上的签核错误,并防止签核瓶颈和延迟。

IC验证的一个标志就是在一个框架内使用多个专用的EDA工具,以使设计人员能够执行各种验证过程。自动执行异构包装组装验证时的目标是相同的。基于已经根据目标晶圆代工厂规则对每个模具进行检查的前提,显着简化了异构验证。保持设计和验证环境之间的独立性以确保验证结果的准确性也很重要。

验证包括DRC,以验证管芯组件之间的相互作用,并且可能需要在每个管芯内提取多个层以查看这些相互作用。物理验证还包括LVL检查,以检查基板之间的对齐,缩放或补偿系数以及焊盘中心或重叠。对于EDA工具,工程师必须了解如何区分每个芯片和每个位置的分层。此外,该工具应利用数字孪生虚拟模型的数据来自动提取正确的装配体表示,以执行DRC和LVL检查。

IC中的连通性检查(LVS)会查看从物理布局数据得出的连接形状和引脚位置,以生成物理网表,并将其与黄金原理图网表进行比较以验证连通性。在每个基板级别和跨基板执行连接检查。以最简单的形式实现的自动化封装LVS流程必须确保中介板和封装GDSII正确地按预期将管芯连接到管芯(对于多管芯系统),并且将管芯连接到C4 / BGA凸点(对于单管芯和多管芯系统)由设计师。

如前所述,系统网表是从整个组件的数字孪生编译而成的。然后将该系统或黄金网表与从制造数据得出的物理设计连接性进行比较。虚拟模型可以突出显示警告或违规,因此设计人员可以在EDA工具的帮助下跟踪和调试错误。

图6基于几何的集成DRC可以防止过多的签核错误。资料来源:Mentor Graphics

2.5和3D异构封装通常包含多个设备和多个基板,以提供系统缩放和性能所需的解决方案。随着管芯和基板之间的轮廓线的减少,这些元件的紧密接近极大地增强了芯片-封装之间的相互作用,因此需要统一的协同设计流程。使用诸如高速接口或功率传输之类的关键元件,对一个基板的决策可能会对相邻基板产生连锁反应,或影响整个系统。

设计人员必须使用快速原型设计和协同设计来评估衬底的可布线性,电气和热性能以及测试,从而找到在单一环境中管理多个衬底的方法,同时跨地区和部门进行协作。随着方法和流程的成熟,系统级设计人员还需要了解封装DRC,LVL验证和组装级LVS是否足以保证正确的功能和成功制造异构组装的能力。

通过以高效,可重复和自动化的流程管理所有这些流程的单一环境,设计人员可以更好地预测和消除潜在的下游问题,有效地执行和评估折衷和设计方案,并清晰地将决策传达给利益相关者。

最后,在堆叠为2D和3D异构组件之前,已知的良好管芯(KGD)测试和封装级测试的生成至关重要。测试团队应重用芯片级的内置自测试(BIST),并通过将其映射到封装级别来扫描模式。封装互连结构的边界扫描测试可确保I / O实际上已连接,并且可以识别任何基板制造或组装问题。

完整的设计和验证流程

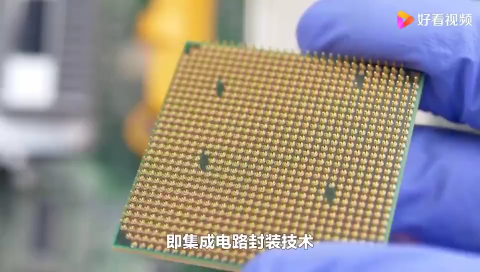

对于许多应用而言,下一代IC封装是在缩小整体封装尺寸的同时实现硅缩放,功能密度和异构集成的最佳途径。将多个设备集成到一个封装中可支持系统扩展需求,减少系统空间,降低制造成本,并通常提高质量和可靠性。

下一代IC封装设计需要一种新的方法来进行所有级别的设计和验证,即使使用数字孪生虚拟原型模型也可以驱动设计和验证的各个方面,即使使用了不同的设计工具也可以使设计人员进行管理。所有这些过程都以高效,可重复和自动化的流程进行。

西门子业务部门Mentor提供了一种高密度高级封装解决方案,该解决方案专为解决下一代IC封装设计的五个关键问题而开发。完整的设计和验证流程整合了行业的黄金标准进行验证。口径3DSTACK以及Xpedition基板集成商和Xpedition封装设计器,利用HyperLynx和FloTHERM进行跨域多物理场分析。

Keith Felton是Mentor Graphics的Xpedition IC封装解决方案的市场经理。

编辑:hfy

-

晶圆

+关注

关注

52文章

4523浏览量

126418 -

eda

+关注

关注

71文章

2535浏览量

170820 -

CAD

+关注

关注

17文章

1038浏览量

71545 -

IC封装

+关注

关注

4文章

172浏览量

26466

发布评论请先 登录

相关推荐

什么是集成电路封装?IC封装为什么重要?IC封装的类型

ad原理图封装怎么和pcb封装关联

四种IC封装设计的特点与用途

RedEDA使用教程(芯片封装设计RedPKG)

半导体封装设计工艺的各个阶段阐述

移动应用高级语言开发——并发探索

半导体封装设计与分析

封装设计中的电-热-力多物理场耦合设计

探索高级IC封装设计的相互关联(下)

探索高级IC封装设计的相互关联(下)

评论