知识越丰富,对知识的敬畏就越深。思维愈发严谨,说话也愈发谨慎,越来越像个老学究,很难再向初学者那样思路广欢乐多了。而普罗大众喜欢的是简单易懂,所以老舍巴金不如韩寒小四,研究雾霾的专家不如柴静的穹顶之下,各种明史学者也敌不过当年明月的一本明朝那些事。但严谨与娱乐也许并不对立,将其结合的最好的应该就是我们伟大的科学家爱因斯坦先生了吧。不信?来张图让大家感受一下。

嗯。大家好,我是Mr.S,上图是我的偶像。不出意外的话串扰将会像反射一样用一系列的文章来说明。在这里小编将尽力用简单的图像来表明串扰的一系列影响,希望大家能耐心的读下去。

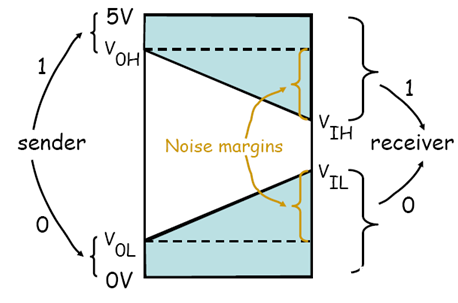

集成电路的发展很大一部分是建立在数字信号的发明上,使用数字信号通信大大提高了信道的噪声裕量。以DDR3信号为例,其接收端的判决电平通常为VinH=900mV,VinL=600mV,也就是说,如果输出为标准的0-1.5V信号的话,在信道上能够容忍的噪声裕量达到了600mV,相当于信号电平的40%。这40%的裕量将被反射,损耗,电源噪声,串扰等问题瓜分。

在这里,高速先生抛出第一个结论:大部分数字信号可能比大家想象中的要强壮得多(心のOS:不要再让我们一条信号一条信号的给你们仿真啦!)。

当然,信号的强壮不是我们为所欲为的资本。尽量的提高信号质量与系统的稳定性是我们攻城狮的职责。

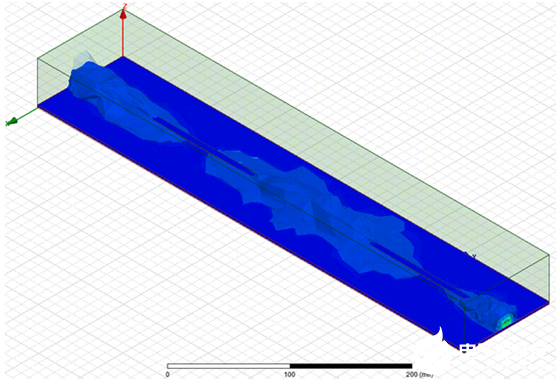

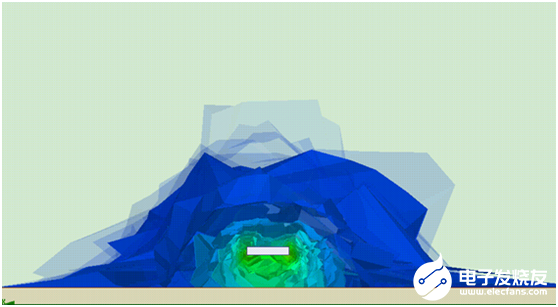

如我们一直强调的,信号传输的并不是电压与电流,而是电磁场。通过电场与磁场的不断转换,信号以光速从发送端传到接收端。当信号传输时,走线附近的电磁场分布如下图:

可以看到,大部分的电磁场分布在信号线以及回流路径之间。

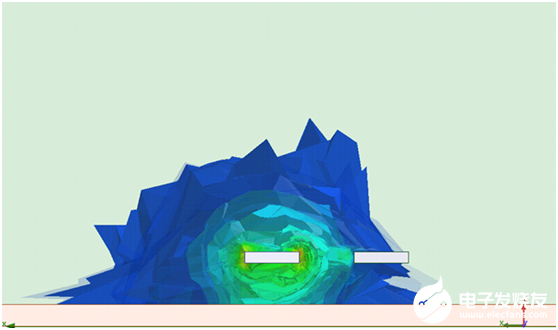

当另一根线闯入了这片电磁场区域时:

一部分的电磁场被吸走了。于是串扰出现了。

编辑:hfy

-

DDR3

+关注

关注

2文章

268浏览量

41769 -

数字信号

+关注

关注

2文章

792浏览量

47193 -

电磁场

+关注

关注

0文章

742浏览量

46810 -

接收端

+关注

关注

0文章

19浏览量

8410

发布评论请先 登录

相关推荐

数字信号技术:串扰是如何形成的?

数字信号技术:串扰是如何形成的?

评论