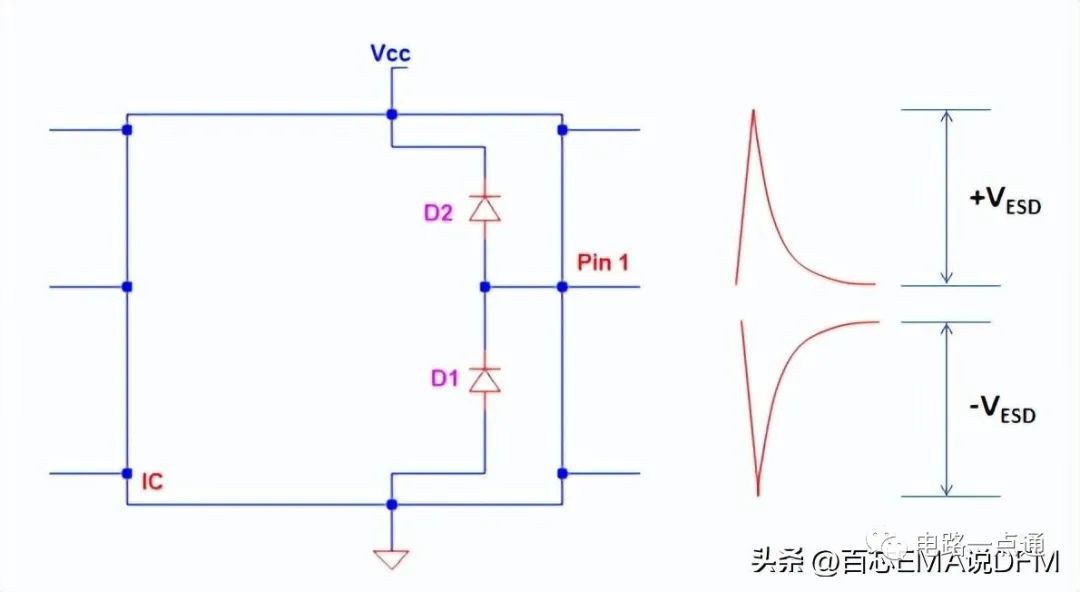

PI仿真一直都是业内的一个难点,也是存在很多争议的领域。以上的仿真结果,就存在一个疑问:由于埋容材料的使用,在一百多兆的位置出现了一个反谐振点,这是埋容材料和By Pass电容共同作用形成的阻抗峰值。这个峰值的存在,就是一个设计隐患,如果在这个频段附近存在较大的电流变化的时候,就会导致很大的电源噪声。

如何处理这个反谐振点,主要有以下思路:

一、 添加相应的板级By-Pass电容,抑制这个反谐振峰值。由于频点在一百多兆,在这频点起作用的电容值很小,需要的数量较多。这样就需要使用大量的小电容,没有达成节约分立电容数量的目的,并且有过设计嫌疑。

二、 添加封装寄生电感和Die电容的参数,准确仿真整个PDN路径的阻抗。这个方法困难的地方在于很多时候拿不到封装和Die的参数。

三、 不理会100M以上的频点的峰值。准确添加了封装和Die参数的全路径PDN阻抗分析, 100M以上频段的阻抗由于封装电感和Die电容的影响,一般情况下都会得到很好的抑制。这也是PI工程师经典的处理事情的方式,“铁路工人,各管一段”,忽略不属于我能解决的频段。

四、 新的解决方案,取得芯片的CPM模型,然后通过对电流的分析得到准确的目标阻抗要求,避免过设计

五、 SSN仿真分析,通过分析最终的时域噪声,来观察噪声分布的频段,以及噪声大小的变化趋势,来辅助电源PDN设计。

时域纹波验证

这个案例,我们把频域PDN阻抗曲线的结果,最终反映到时域的噪声上,图十二是针对1.5V时域SSN仿真的结果,也能看到使用埋容材料前后的区别

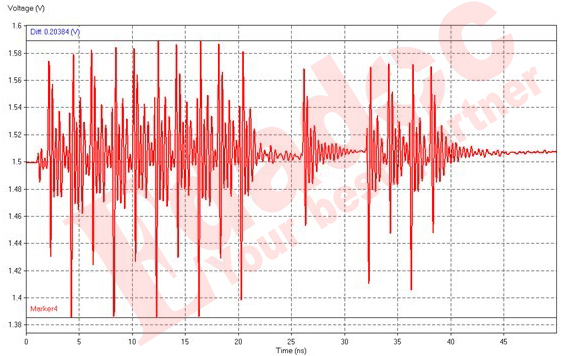

没有使用埋容的SNN仿真结果,从波形可以测得SSN的峰峰值为0.204V

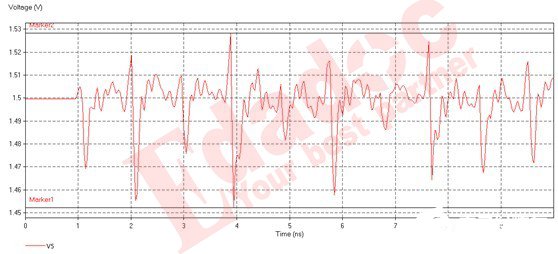

未删除电容的SNN仿真结果,从波形可以测得SSN的峰峰值为0.076V

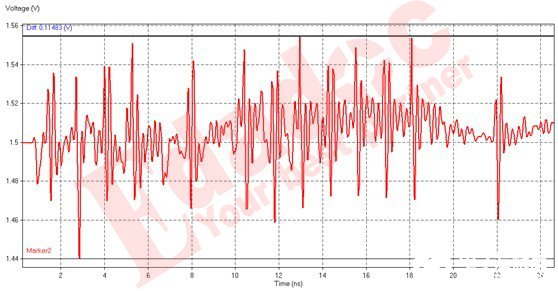

删除70%电容的SNN仿真结果,从波形可以测得SSN的峰峰值为0.115V

图十二 1.5V电源SSN仿真结果

从SSN仿真来看,使用埋容可以有效抑制噪声,并且在噪声裕量允许的范围内,可以大幅删除板上分立电容,节约板子的空间。

电源Noise测试验证

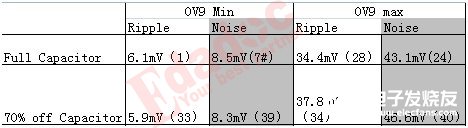

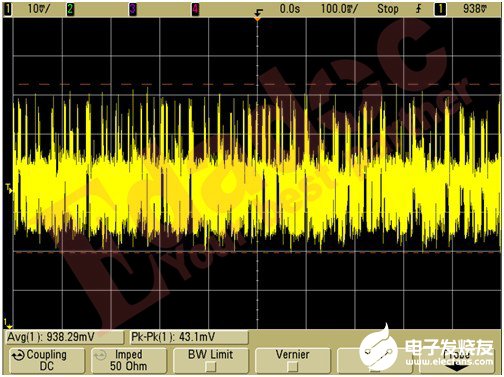

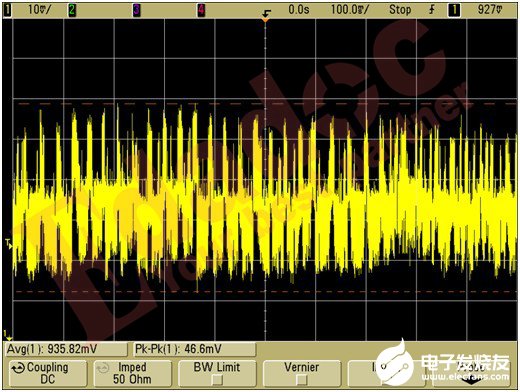

针对0.9V电源,测试结果如下表:Ripple为电源纹波测试,测试点为电源模块附近。Noise为电源噪声测试,测试点在主芯片附近。Min是负载较轻时的测试结果,Max为芯片全速运行,负载最重时的结果。

表一 0.9V 电源噪声和纹波测试结果

从上表可以看出,去除70%分立电容后,板子上的电源噪声没有明显增加, 因为使用埋容材料在177M附近形成的反谐振点没有导致较大的噪声。实际电源测试波形如下:

图十三 0.9V 电源未删除电容的噪声测试结果

图十四 0.9V 电源删除70%电容的噪声测试结果

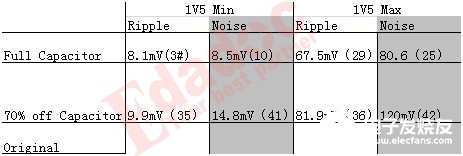

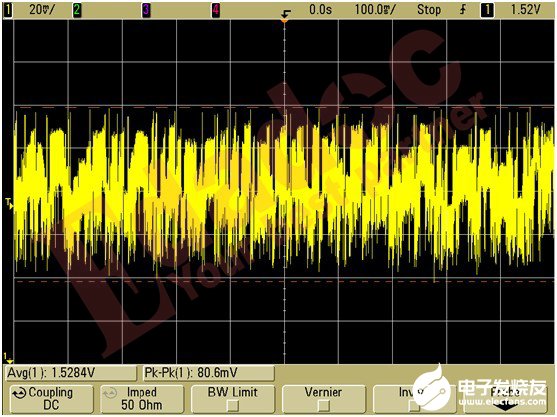

针对1.5V的测试结果如下:

表二 1.5V 电源噪声和纹波测试结果

从上表可以看出,去除70%分立电容后,1.5V在满负荷工作时,噪声变大,量值和趋势与仿真结果类似。观察噪声分布的频率,能看到实际噪声是因为PDN阻抗曲线在低频段整体变大引起的。实际电源测试波形如下:

图十五1.5V 电源未删除电容的噪声测试结果

图十六 1.5V 电源删除70%电容的噪声测试结果

结 论

Cadence-Sigrity 仿真软件,提供了从PDN阻抗分析到时域噪声SSN分析的全套解决方案,可以完美的支持PI设计仿真的需要。

通过Power SI提取PDN的阻抗,然后和Target Impedance进行对比,来衡量埋容的PCB设计带来的影响,同时进行电容优化。(这时候也可以采用Cadence-Sigrity的OPI 工具来协助电容选择和优化,效率更高)

然后采用Cadence-Sigrity的Speed 2000来进行SSN仿真分析,从时域角度验证埋容的PCB设计,确保设计成功。

编辑:hfy

-

PCB设计

+关注

关注

392文章

4568浏览量

83183 -

谐振

+关注

关注

5文章

325浏览量

39234 -

PDN

+关注

关注

0文章

71浏览量

22568

发布评论请先 登录

相关推荐

PCB设计如何处理这个反谐振点

PCB设计如何处理这个反谐振点

评论