与以前的测试要求和方法相比,当前使用 32 欧姆负载的耳机端口测试提出了新的挑战。当前的 Microsoft Windows 徽标计划版本 3 要求在整个 20Hz 到 20KHz 带宽上进行串扰测试,而不是简单地在 1KHz 或 10KHz 处进行串扰测试。不幸的是,由于低阻抗负载引起的高电流,我们不能再忽视与布线和连接器阻抗相关的返回路径阻抗的影响。尽管大多数系统比所提供的模型更复杂,但我们可以了解选择好的连接器和降低整体返回路径阻抗的重要性。

耳机端口的简要概述

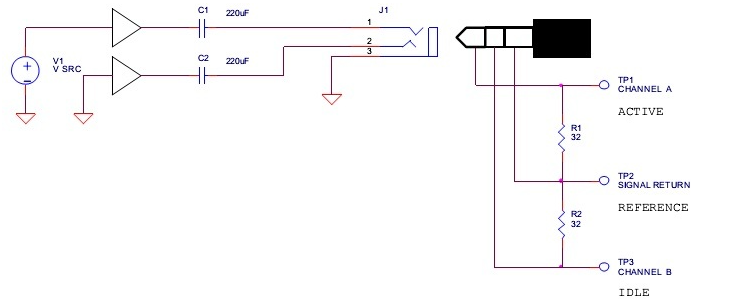

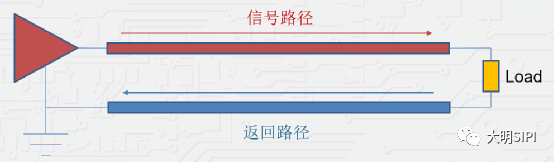

让我们看一个简化的耳机端口。(图 1 - 简化电路)耳机放大器(编解码器或分立放大器)将一条走线驱动到耦合电容器,将另一条走线驱动到插孔。放大器有输出阻抗,走线有一定的阻抗,插孔也是。电容器具有频率相关阻抗。为了进一步简化我们的分析,我们将忽略除电容器之外的所有这些电路元件的复杂部分(电感和电容),而只关注其阻抗的实部(电阻)。幸运的是,这不会显着改变我们的结果。

简化电路

简化为用于仿真的等效电路为了将系统简化为易于模拟的东西,我们将许多电阻组合在一起。放大器的输出电阻、走线电阻、插头接触电阻、电缆电阻和测试设备连接器电阻将由放置在放大器输出端的集总电阻 Rs 表示。系统接地阻抗、套管接触电阻、电缆电阻以及负载公共点和返回引脚之间的电阻将由放置在系统接地点的 Rg 表示。

减少单频计算

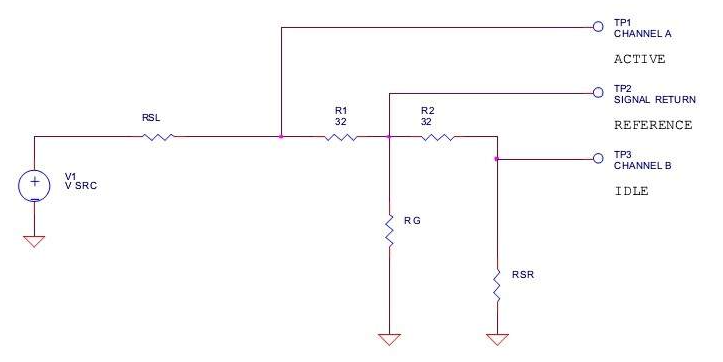

如上图所示,串扰在整个频率范围内相当恒定,实际上在低端有所改善,因为交流耦合电容导致幅度响应降低。因此,在任一频率下,我们都可以在 RS 上增加交流耦合电容,进一步减少电路和辅助计算。最终的等效电路如下所示。

最终简化电路

插孔接触电阻和电缆电阻对串扰有什么影响?

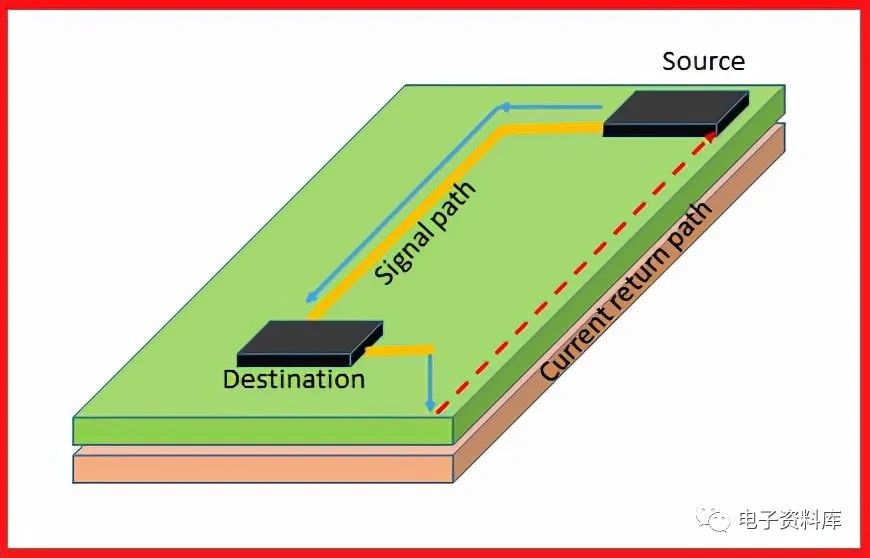

通常,返回路径本身的电阻非常低,因为我们经常使用地平面以及插孔和音频设备之间的短距离。但是,通常需要将某些插孔(例如台式 PC 中的前面板插孔)放置在远离音频设备的位置。最小化电缆和连接器阻抗至关重要。即便如此,返回路径阻抗的最大贡献因素是 3.5 毫米立体声插孔中套管连接的接触阻抗。典型设备的接触阻抗范围从 30 毫欧到 100 毫欧(最大值)。不幸的是,即使是几十毫欧也会导致系统表现出超过 -70dB 的串扰(一个共同目标),如下图所示。

源阻抗有影响吗?

自然,但这种影响通常很小,除非输出阻抗与负载阻抗相比较大,这是不推荐的。32 欧姆负载的串扰与源阻抗的关系图显示了大输出阻抗可能带来的好处,但大部分输出功率永远不会到达负载,并且会以热量而非声音的形式消散。

返回路径阻抗,而不是音频设备的固有串扰,通常是现代系统中低阻抗(耳机)串扰性能的限制因素。需要仔细注意布线和连接器,以满足当前对 PC 行业施加的严格要求。具体来说,选择 3.55 毫米插孔,保证接触阻抗小于 10 毫欧,并确保前面板连接器的任何额外布线和连接器阻抗增加的返回路径阻抗小于 30 毫欧。

编辑:hfy

-

连接器

+关注

关注

96文章

12598浏览量

133091 -

接触电阻

+关注

关注

1文章

88浏览量

11699

发布评论请先 登录

相关推荐

高速电路PCB “地”、返回路径、镜像层和磁通最小化

信号返回路径:参考平面设计为两个好还是一个好?

EMC中的猪尾巴效应是指什么?

PCB中的返回路径如何工作,在设计中成功创建参考平面的技巧

关于返回路径与返回电流

高速电路PCB“地”、返回路径、镜像层和磁通化

浅谈建模返回路径阻抗效应

浅谈建模返回路径阻抗效应

评论