EMC整改六步走

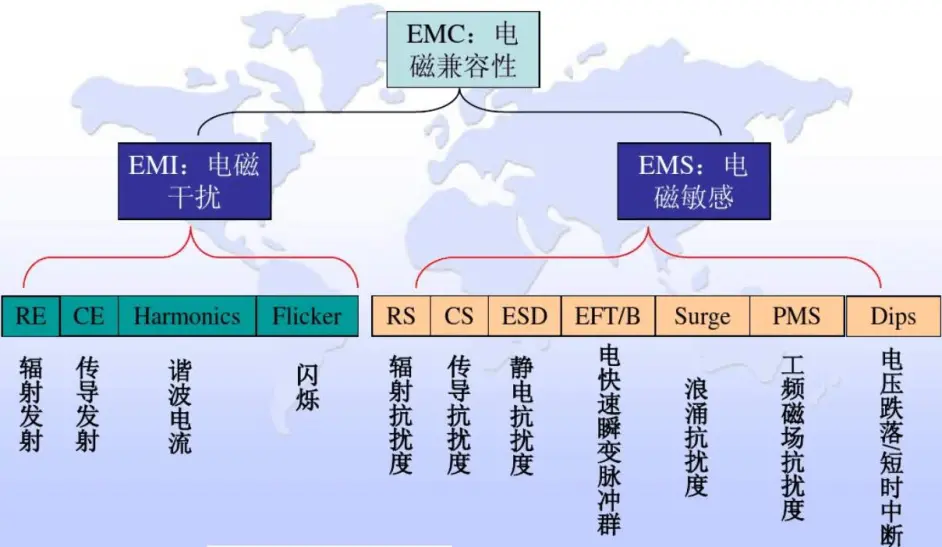

电磁兼容性EMC(Electro Magnetic Compatibility)是指设备或系统在其电磁环境中符合要求运行并不对其环境中的任何设备产生无法忍受的电磁干扰的能力。因此,EMC包括两个方面的要求:一方面是指设备在正常运行过程中对所在环境产生的电磁干扰不能超过一定的限值;另一方面是指器具对所在环境中存在的电磁干扰具有一定程度的抗扰度,即电磁敏感性。

各种运行的电子设备之间的干扰主要以电磁传导、电磁感应和电磁辐射三种方式彼此关联并相互影响,在一定的条件下会对运行的设备和人员造成干扰、影响和危害。关于具体EMC领域的整改文章其实不少。

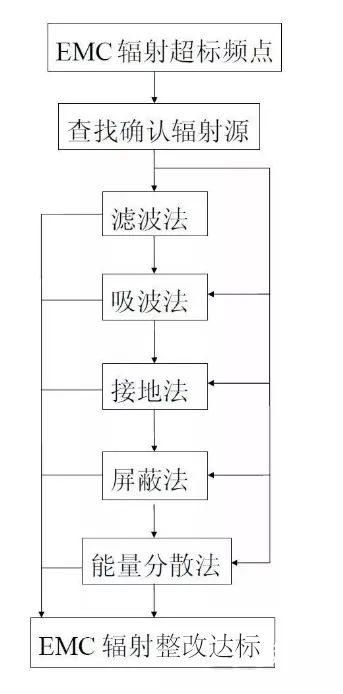

EMC 整改六步法如下:第一步查找确认辐射源,第二步滤波,第三步吸波,第四步接地,第五步屏蔽,第六步能量分散法。具体思路如下图所示:

第一步:查找确认辐射源的方法有排除法、频谱分析仪频点搜索法、元件固有频率分析法。而排除法包含有拔线法、分区工作排除法、低电压小电流的人体触摸法,区域屏蔽排除法。元件固有频率分析法是指对一些元件的固定频率及其倍频频率分析归类法,如晶振和 DDR 等元件的工作频率都是固定的。

第二步:滤波一般分为电容滤波、RC 滤波和 LC 滤波等;

第三步:吸收电磁波方法有电路串联磁珠法、绕穿磁环法和贴吸波材料法。使用吸收电磁波方法时要特别注意:辐射超标电磁波频率必须在所使用的吸波材料所吸收电磁波频率范围之内,否则造成吸波法会失效。

第四步:接地法一般分为单点接地法和多点接地法。

第五步:屏蔽法一般有加屏蔽罩屏蔽法、外壳屏蔽法和PCB 走线布局屏蔽法。

第六步:能量分散法是指一些被测物的控制软件可利用展频和跳频等技术对能量集中的频段进行展宽频率带宽和跳变频率实现分散频段能量,从而使附加在单点频率上的能量降低,也就是起到了单点频率辐射的电磁波强度降低的功效。故此法对尖峰毛刺形波形的频率辐射超标会起到显著效果,对包络形波形频率辐射超标起不到明显作用。

这个EMC整改六步法比较适用于常见电子设备的整改。但上面的6种方法,其实天纵君认为它们虽有助于提高 EMC 辐射整改效率,节省周期,快速通过EMC测试,但其并不是根本性解决EMC问题的方案,EMC的问题最理想还是在设计端就进行考虑,而不是事后用一些“围追堵截”的方案来应急。

EMC(Electromagnetic Compatibility)即我们常说的电磁兼容技术。它包含了EMI和EMS两个部分的要求,即在电气装置或系统共同的电磁环境条件下,既不受电磁环境的影响,也不会给环境以干扰。

EMC整改方法

首先,要根据实际情况对产品进行诊断,分析其干扰源所在及其相互干扰的途径和方式。再根据分析结果,有针对性的进行整改。

一般来说主要的整改方法有如下几种:

1、减弱干扰源在找到干扰源的基础上,可对干扰源进行允许范围内的减弱,减弱源的方法一般有如下方法:

a、在IC的Vcc和GND之间加去耦电容,该电容的容量在0.01μF到0.1μF之间,安装时注意电容器的引线,使它越短越好。

b、在保证灵敏度和信噪比的情况下加衰减器。如VCD、DVD视盘机中的晶振,它对电磁兼容性影响较为严重,减少其幅度就是可行的方法之一,但其不是唯一的解决方法。

c、还有一个间接的方法就是使信号线远离干扰源。

2、电线电缆的分类整理在电子设备中,线间耦合是一种重要的途径,也是造成干扰的重要原因,因为频率的因素,可大体分为高频耦合与低频耦合。因耦合方式不同,其整改方法也是不同的,下边分别讨论:

(1)低频耦合是指导线长度等于或小于1/16波长的情况,低频耦合又可分为电场和磁场耦合。

电场耦合的物理模型是电容耦合,因此整改的主要目的是减小分布耦合电容或减小耦合量,可采用如下的方法:

a、增大电路间距是减小分布电容的最有效的方法。

b、追加高导电性屏蔽罩,并使屏蔽罩单点接地能有效的抑制低频电场干扰。

c、追加滤波器可减小两电路间的耦合量。

d、降低输入阻抗,例如CMOS电路的输入阻抗很高,对电场干扰极其敏感,可在允许范围内在输入端并接一个电容或阻值较低的电阻。

磁场耦合的物理模型是电感耦合,其耦合主要是通过线间的分布互感来耦合的,因此整改的主要方法是破坏或减小其耦合量,大体可采用如下的方法:

a、追加滤波器,在追加滤波器时要注意滤波器的输入输出阻抗及其频率响应。

b、减小敏感回路与源回路的环路面积,即尽量使信号线或载流线与其回线靠近或扭绞在一体。

c、增大两电路间距,以便减小线间互感来减低耦合量。

d、若有可能,尽量使敏感回路与源回路平面正交或接近正交来降低两电路的耦合量。

e、用高导磁材料来包扎敏感线,可有效的解决磁场干扰问题,值得注意的是要构成闭和磁路,努力减小磁路的磁阻将会更加有效。

(2)高频耦合是指长于1/4波长的走线由于电路中出现电压和电流的驻波,会使耦合量增强,可采用如下的方法加以解决:

a、尽量缩短接地线,与外壳接地尽量采用面接触的方式。

b、重新整理滤波器的输入输出线,防止输入输出线间耦合,确保滤波器的滤波效果不变差。

c、屏蔽电缆屏蔽层采用多点接地。

3、改善地线系统

理想的地线是一个零阻抗,零电位的物理实体,它不仅是信号的参考点,而且电流流过时不会产生电压降。在具体的电气电子设备中,这种理想地线是不存在的,当电流流过地线时必然会产生电压降。

据此可根据地线中干扰形成机理可归结为以下两点,第一,减小低阻抗和电源馈线阻抗。第二,正确选择接地方式和阻隔地环路,按接地方式来分有悬浮地、单点接地、多点接地、混合接地。如果敏感线的干扰主要来自外部空间或系统外壳,此时可采用悬浮地的方式加以解决,但是悬浮地设备容易产生静电积累,当电荷达到一定程度后,会产生静电放电,所以悬浮地不宜用于一般的电子设备。

单点接地适用于低频电路,为防止工频电流及其他杂散电流在信号地线上各点之间产生地电位差,信号地线与电源及安全地线隔离,在电源线接大地处单点连接。单点接地主要适用于频率低于3MHz的情况。多点接地是高频信号唯一实用的接地方式,在射频时会呈现传输线特性,为使多点接地的有效性,当接地导体长度超过最高频率1/8波长时,多点接地需要一个等电位接地平面。多点接地适用于300KHz以上。混合接地适用于既然有高频又有低频的电子线路中。

4、屏蔽

屏蔽是提高电子系统和电子设备电磁兼容性能的重要措施之一,它能有效的抑制通过空间传播的各种电磁干扰。屏蔽按机理可分为磁场屏蔽与电场屏蔽及电磁屏蔽。电场屏蔽应注意以下几点:

1、选择高导电性能的材料,并且要有良好的接地。

2、正确选择接地点及合理的形状,最好是屏蔽体直接接地。磁场屏蔽通常只是指对直流或甚低频磁场的屏蔽,其屏蔽效能远不如电场屏蔽和电磁屏蔽,磁屏蔽往往是工程的重点,磁屏蔽时:

a、要选用铁磁性材料。

b、磁屏蔽体要远离有磁性的元件,防止磁短路。

c、可采用双层屏蔽甚至三层屏蔽。

d、屏蔽体上边的开孔要注意开孔的方向,尽可能使缝的长边平行于磁通流向,使磁路长度增加最少。一般来说,磁屏蔽不需要接地,但为防止电场感应,还是接地为好。电磁场在通过金属或对电磁场有衰减作用的阻挡体时,会受到一定程度的衰减,即产生对电磁场的屏蔽作用。在实际的整改过程中视具体需要而定选择何种屏蔽及屏蔽体的形状、大小、接地方式等。

5、改变电路板的布线结构

有些频率点是通过电路板上走线分布参数所决定的,通过前述方法不大有用,此类整改通过在走线中增加小的电感、电容、磁珠来改变电路参数结构,使其移到限值要求较高的频率点上。对于这类干扰,要想从根本上解决其影响,就要重新布线。

小结:总之前面几种方法对提高电磁兼容性都有好处,但应用最为广泛的是改变地线结构及电线电缆的分类整理的方法,这些方法不仅节约成本,而且是最有效的整改方法。屏蔽虽然会增加成本,但是其所起到的屏蔽效能有时是其它方法无法媲美的。所以,在实际的整改中应以改变地线结构、电线电缆的分类整理、屏蔽的方法为主,以其它方法为辅。

EMC领域的三个重要规律和EMC问题三个要素

一、EMC三个重要规律

规律一、EMC费效比关系规律:EMC问题越早考虑、越早解决,费用越小、效果越好。

在新产品研发阶段就进行EMC设计,比等到产品EMC测试不合格才进行改进,费用可以大大节省,效率可以大大提高;反之,效率就会大大降低,费用就会大大增加。经验告诉我们,在功能设计的同时进行EMC设计,到样板、样机完成则通过EMC测试,是最省时间和最有经济效益的。相反,产品研发阶段不考虑EMC,投产以后发现EMC不合格才进行改进,非但技术上带来很大难度、而且返工必然带来费用和时间的大大浪费,甚至由于涉及到结构设计、PCB设计的缺陷,无法实施改进措施,导致产品不能上市。

工程师在整改测试中

天纵检测在实际检测工作中经常碰到的情况是:通过“围追堵截”的方法通过相关EMC测试和认证的强制要求,但这样的产品在实际生产的可生产性和产品实际适用性接近于零。这就造成实验室样品和实际成品是不一致的,EMC的整改成了“掩耳盗铃”的摆设了,因此真正要考量EMC问题是要在产品设计时就要考虑进去的,而不应该把主要对策放在产品测试阶段。

规律二、高频电流环路面积S越大, EMI辐射越严重。

高频信号电流流经电感最小路径。当频率较高时, 一般走线电抗大于电阻,连线对高频信号就是电感,串联电感引起辐射。电磁辐射大多是EUT被测设备上的高频电流环路产生的,最恶劣的情况就是开路中的“天线形式”。对应处理方法就是减少、减短连线,减小高频电流回路面积,尽量消除任何非正常工作需要的“天线”,如不连续的布线或有天线效应之元器件过长的插脚。减少辐射骚扰或提高射频辐射抗干扰能力的最重要任务之一,就是想方设法减小高频电流环路面积S。在天纵检测实践中一些具体方法就是处理好接地问题(电源地与信号地)。

规律三、环路电流频率f越高,引起的EMI辐射越严重,电磁辐射场强随电流频率f的平方成正比增大。

减少辐射骚扰或提高射频辐射抗干扰能力的最重要途径之二,就是想方设法减小骚扰源高频电流频率f,即减小骚扰电磁波的频率f。关于这个f规律,天纵经验上看很多是因为屏蔽和外壳设计或做工造成的,因为频率越高,波长越小,越是容易从外壳或屏蔽体的小缝隙中泄露出来。

二、EMC问题三要素

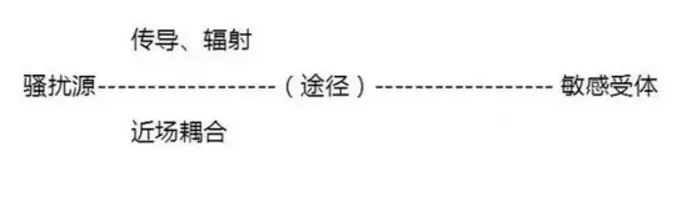

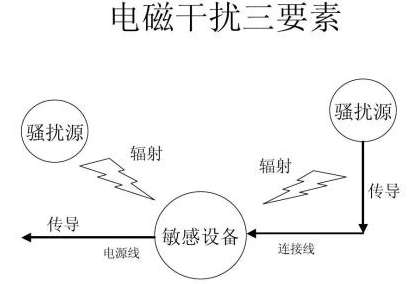

开关电源及数字设备由于脉冲电流和电压具有很丰富的高频谐波,因此会产生很强的辐射。电磁干扰包括辐射型(高频) EMI、传导型(低频)EMI,即产生EMC问题主要通过两个途径:一个是空间电磁波干扰的形式;另一个是通过传导的形式,换句话说,产生EMC问题的三个要素是:电磁干扰源、耦合途径、敏感设备。辐射干扰主要通过壳体和连接线以电磁波形式干扰空间电磁环境;传导干扰是通过电源线骚扰公共电网或通过其他端子(如:射频端子,输入端子)影响相连接的设备。

T、AV设备可能的骚扰源:

A) FM接收机、TV接收机本机振荡,基波及谐波由高频头、本机振荡电路产生;

B) 开关电源的开关脉冲及高次谐波,同步信号方波及高频谐波,行扫描显像电路产生的行、场信号及高频谐波;

C) 数字电路工作需要的各种时钟信号及高频谐波、以及它们的组合,各种时钟如CPU芯片工作时钟、解码器工作时钟、视频同步时钟等;

D) 数字信号方波及高频谐波,晶振产生的高次谐波,非线性电路现象(非线性失真、互调、饱和失真、截止失真)等引起的无用信号、杂散信号;

E) 非正弦波波形,波形毛剌、过冲、振铃,电路设计存在的寄生频率点。

F) 对于敏感受体通过耦合途径接受的外部骚扰包括浪涌、快速脉冲群、静电、电压跌落、电压变化和各种电磁场。

电磁骚扰的特性 :

① 单位脉冲的频谱最宽;

② 频谱中低频含量取决于脉冲的面积,高频分量取决于脉冲前后沿的陡度;

③ 晶体振荡电平必须满足一定幅度, 数字电路才能按一定的时序工作,使晶振产生的骚扰呈现覆盖带宽、骚扰电平高的特点;

④ 收发天线极化、方向特性相同时,EMI辐射和接受最严重;收发天线面积越大, EMI危害逾大;

⑤ 骚扰途径:辐射,传导,耦合和辐射、传导、耦合的组合。

⑥ 电源线传导骚扰主要由共模电流产生;

⑦ 辐射骚扰主要由差模电流形成的环路产生。

真传一句话,假传万卷书。我们清楚了EMC中的三个规律和三个要素,会使得EMC问题变得简单和有规可循。了解了EMC的规律和传播要素,其实解决EMC问题的方法和思路也就清晰明了了,我们只要中断其中的一个因素,EMC问题必然都能得到很大的改良。

责任编辑:lq

-

emc

+关注

关注

165文章

3641浏览量

181139 -

电磁感应

+关注

关注

17文章

582浏览量

57493 -

电容滤波

+关注

关注

6文章

54浏览量

57958

原文标题:EMC整改学不会?看看行业大佬怎么说!

文章出处:【微信号:fcsde-sh,微信公众号:fcsde-sh】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

TIM_PWM+DMA输出三个不同占空比的单脉冲,为什么第三个数据总是第一个输出?

三个TLE9877用ssc相连影响烧录怎么解决?

请问ADXL345三个轴采样频率最高能达到多少?

EMC运行三大规律

看懂EMC整改知识:原来竟然如此简单!|深圳比创达EMC(下)

76E003的仿真烧录需要占用三个IO,这三个IO除了仿真怎么设置成普通IO使用?

滤波、接地、屏蔽、三个视角看EMC设计

如何在MPC5748G中同时开发三个内核?

EMC整改的三大规律和三大要素

EMC领域的三个重要规律和EMC问题三个要素

EMC领域的三个重要规律和EMC问题三个要素

评论