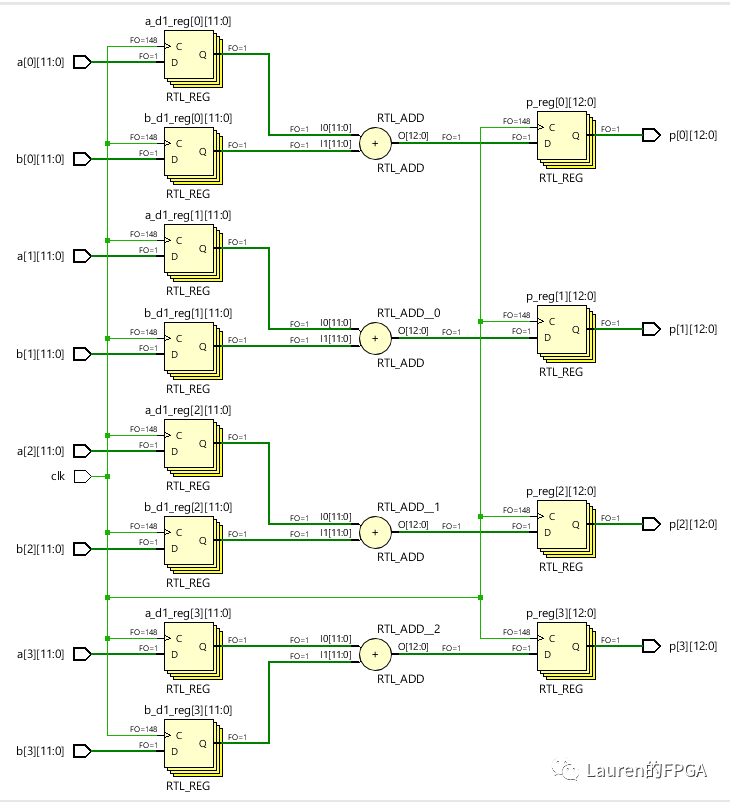

这里并行加法是指多个加法操作同时执行,这意味着需要消耗多个加法器。这里我们以4个12-bit数相加(加数和被加数均为12-bit,故和为13-bit,从而避免了溢出问题)。相应的电路图如下图所示。图中的RTL_ADD即为加法器,同时此电路对输入和输出数据均添加了流水寄存器。

此电路对应的RTL代码如下图所示,这里我们使用了SystemVerilog来描述。输入a和b均为4个12-bit数据构成的数组。输出p也是4个12-bit构成的数组。代码第17行至第23行是核心部分,包括了对输入、输出添加流水寄存器和加法操作。

责任编辑:lq

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电路图

+关注

关注

10209文章

10644浏览量

509778 -

加法器

+关注

关注

6文章

174浏览量

29719 -

数组

+关注

关注

1文章

408浏览量

25593

原文标题:并行加法的高效实现

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

verilog中for循环是串行执行还是并行执行

中的for循环也是并行执行的。 Verilog中的for循环可以用来实现重复的操作,例如在一个时钟周期中对多个电路进行操作。在循环内部,多个语句可以同时执行,而不受循环次数的限制。这种并行执行的机制使得Verilog在硬件设计中

如何在FPGA中实现高效的compressor加法树呢?

大规模的整数加法在数字信号处理和图像视频处理领域应用很多,其对资源消耗很多,如何能依据FPGA物理结构特点来有效降低加法树的资源和改善其时序特征是非常有意义的。

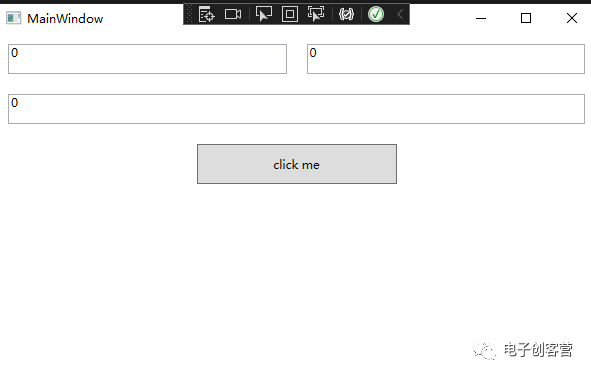

使用MVVM框架实现一个简单加法器

使用MVVM框架来实现一个简单加法器。最终效果如下,点击按钮可以对上面两个文本框中的数字进行相加得出结果显示在第三个文本框中。重点在于看mvvm框架下程序该怎么写。使用CommunityToolkit.Mvvm框架,通过nuget进行安装。

为什么研究浮点加法运算,对FPGA实现方法很有必要?

,浮点加法器是现代信号处理系统中最重要的部件之一。FPGA是当前数字电路研究开发的一种重要实现形式,它与全定制ASIC电路相比,具有开发周期短、成本低等优点。 但多数FPGA不支持浮点运算,这使FPGA在数值计算、数据分析和信号处理等方

NVMe在FibreChannel上的性能优势:一种新的并行高效协议

电子发烧友网站提供《NVMe在FibreChannel上的性能优势:一种新的并行高效协议.pdf》资料免费下载

发表于 08-30 09:50

•0次下载

全加法器的工作原理和电路解析

加法器可以是半加法器或全加法器。不同之处在于半加法器仅用于将两个 1 位二进制数相加,因此其总和只能从 0 到 2。为了提高这种性能,开发了FullAdder。它能够添加三个 1 位二

并行FIR滤波器MATLAB与FPGA实现

本文介绍了设计滤波器的FPGA实现步骤,并结合杜勇老师的书籍中的并行FIR滤波器部分进行一步步实现硬件设计,对书中的架构做了复现以及解读,并进行了仿真验证。

并行加法的高效实现

并行加法的高效实现

评论