赛灵思为 FPGA 和 MPSoC 器件中所有受支持的 I/O 标准提供了 I/O 缓存信息规范 (I/O Buffer Information Specification, IBIS) 模型。

本篇博文旨在提供有关如何为可编程逻辑 (PL) 和处理器系统 (PS) 多用途 I/O (MIO) 进行 IBIS 模型名称解码的指导信息。 本文主要分 3 个部分:

PL I/O 标准

PS MIO 标准

PS DDR I/O 标准

在这 3 个章节中包含多个解码器表格,其中逐一细分罗列了模型名称的每个部分并提供了一些模型名称示例。

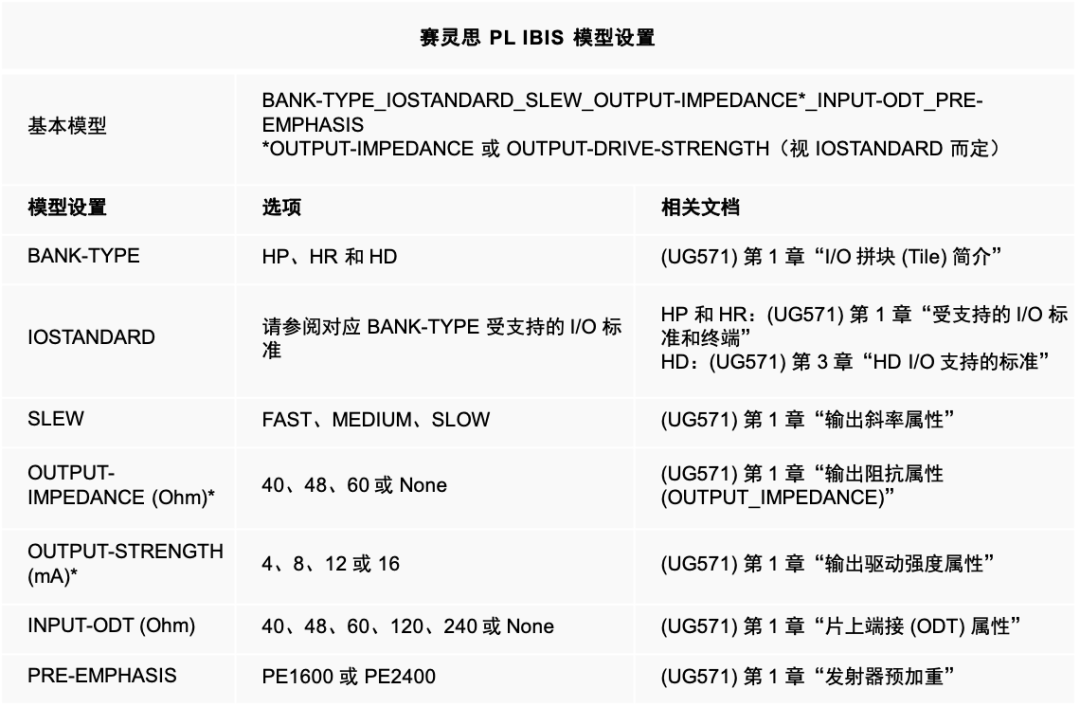

1. 赛灵思 PL I/O 标准 IBIS 解码器

PL IBIS 解码器可用于为所有可编程逻辑 I/O 执行 PL IBIS 模型解码。 它适用于 Zynq MPSoC PL I/O。

表 1:PL IBIS 解码器

所有模型(LVDS 除外*)都将包含“bank 类型 (Bank Type)”、“I/O 标准 (IOStandard)”、“斜率 (Slew Rate)”和“输出阻抗/驱动强度 (Output Impedance/DriveStrength)”。

*LVDS 模型将包含“bank 类型 (Bank Type)”、“LVDS”、“I/O 标准 (IOStandard)”和“数字端接 (Digital Termination)”。

内部 100-ohm 差分终端仅在以 1.8V (LVDS) 或 2.5V (LVDS_25) 加电的 bank 中可用。 请参阅(UG571) v1.12 第 103 页以获取详细信息。

https://china.xilinx.com/support/documentation/user_guides/c_ug571-ultrascale-selectio.pdf

注:并非每个 IBIS 模型都包含所有模型设置。

如果模型名称中不含某项设置,即表示此模型不支持该项设置。

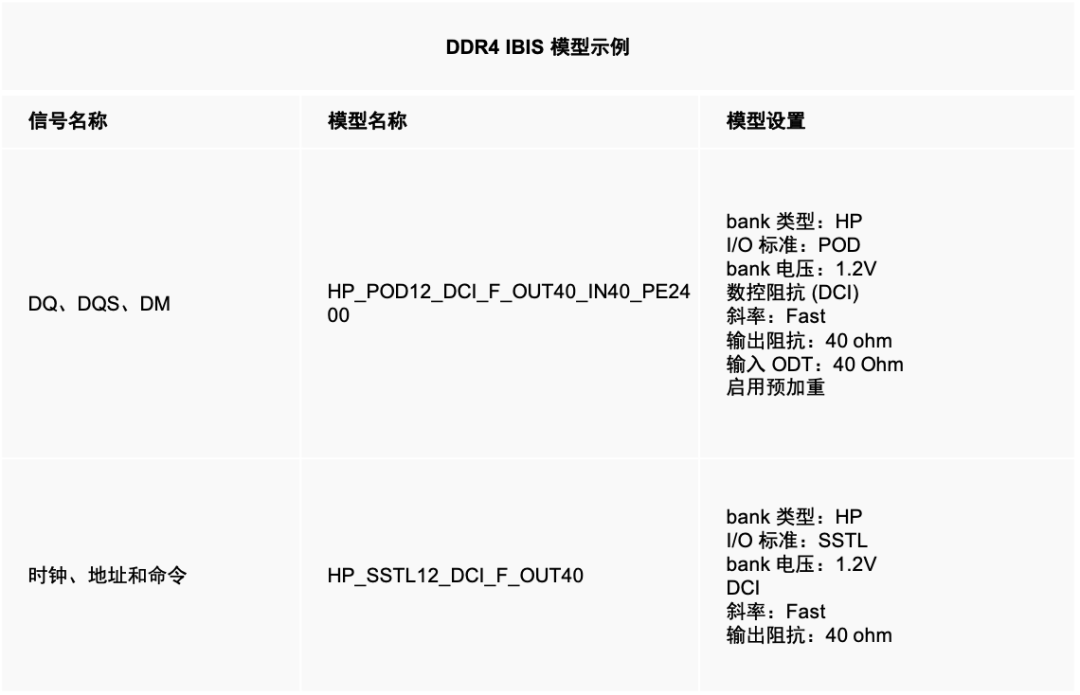

表 2 和表 3 提供了适用于 DDR4 和 SelectIO 的 PL IBIS 模型示例。

表2:PL DDR4 IBIS 模型

差分信号在 IBIS 文件中的“[Diff Pin]”关键字下指定。

表 3:PL SelectIO IBIS 模型

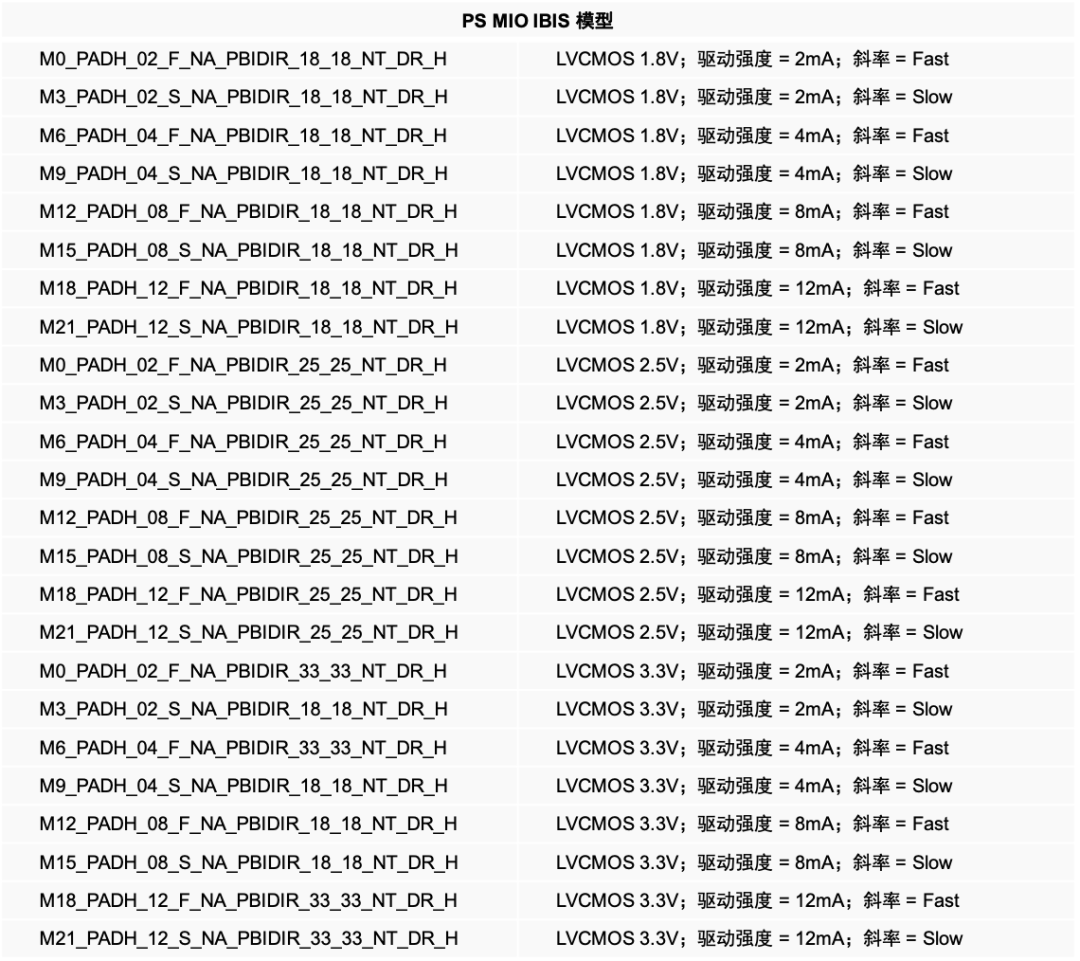

2. 赛灵思 Zynq MPSoC PS MIO IBIS 模型

Zynq MPSoC MIO 管脚支持 LVCMOS,可提供以下选项

接口电压:1.8V、2.5V 或 3.3V

驱动强度:2mA、4mA、8mA 或 12mA

斜率:Slow 或 Fast

MIO IBIS 模型格式为M0_PADH_02_F_NA_PBIDIR_18_18_NT_DR_H。

表 4 对每个 IBIS 模型的驱动设置进行了解释。

表 4:PS MIO IBIS 模型

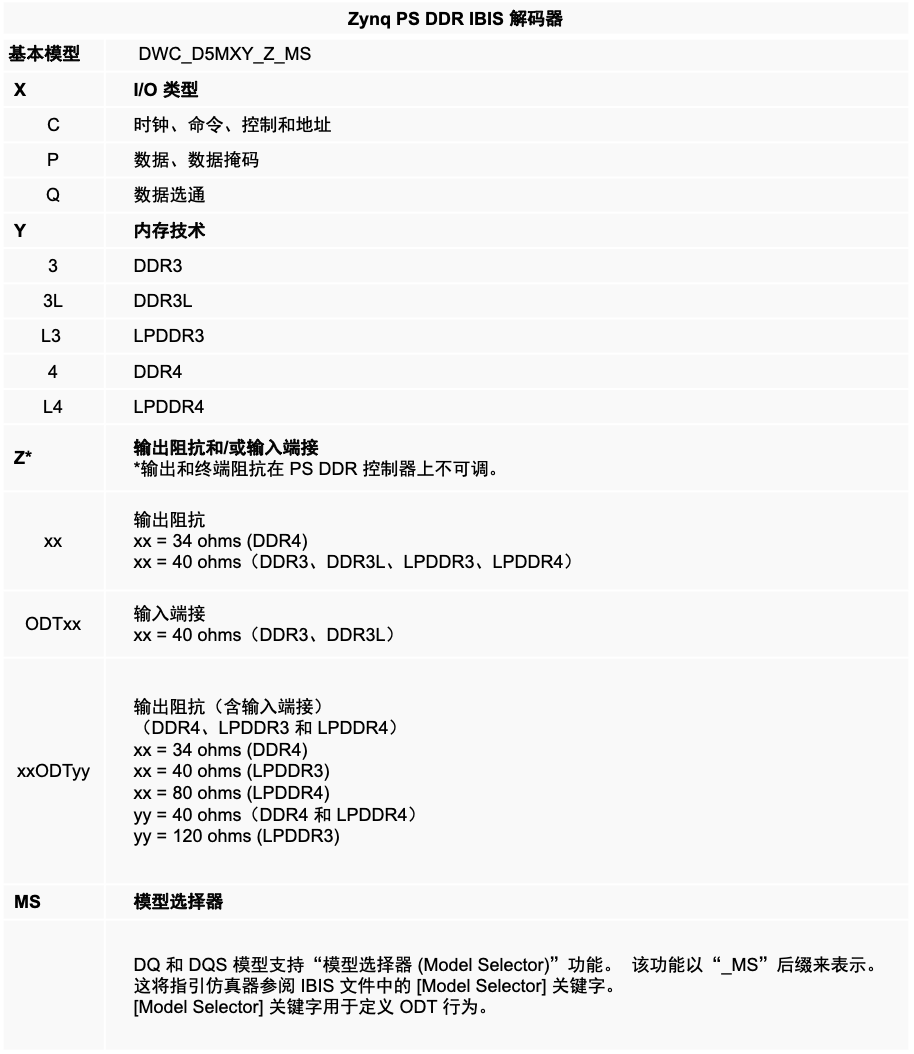

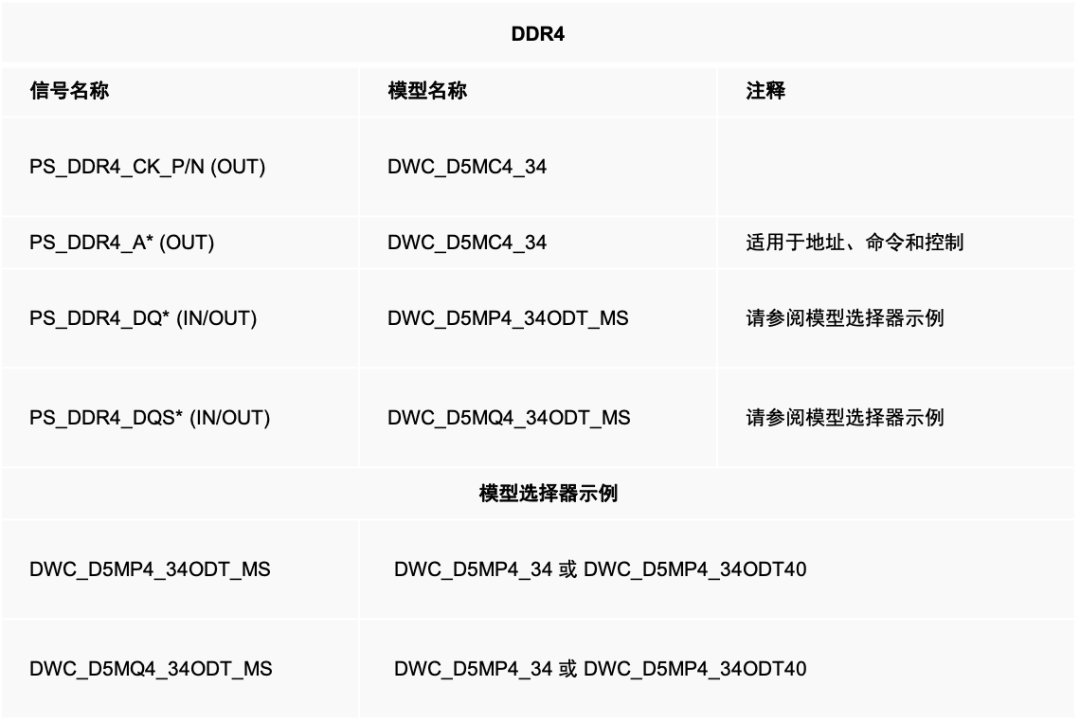

3. 赛灵思 Zynq MPSoC PS DDR IBIS 模型

Zynq MPSoC PS DDR IBIS 信号与所有其它信号都不同。

表 5 显示了适用于 Zynq MPSoC PS DDR IBIS 模型的解码器。

其中为每一种 DDR 内存类型的 IBIS 模型都提供了相应的示例。

表 5:PS DDR IBIS 解码器

表 6 到 10 提供了对应受支持的 PS DDR 技术的 Zynq PS DDR IBIS 示例。

表 6:PS DDR3

表 7:PS DDR3L

表 8:PS LPDDR3

表 9:PS DDR4

表 10:PS LPDDR4

责任编辑:lq

-

处理器

+关注

关注

68文章

18261浏览量

222087 -

解码器

+关注

关注

9文章

1073浏览量

40151 -

可编程逻辑

+关注

关注

7文章

511浏览量

43903

原文标题:开发者分享 | 赛灵思 PL 和 PS IBIS 模型解码器

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA零基础学习系列精选:半导体存储器和可编程逻辑器件简介

可编程片上系统是什么意思

可编程片上系统是什么

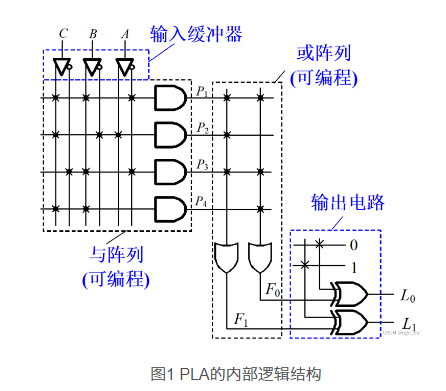

可编程逻辑阵列PLA内部逻辑结构示意

CH32X035 的可编程协议 I/O 微控制器(PIOC)资料更新了

安全挖掘快速多用途工具

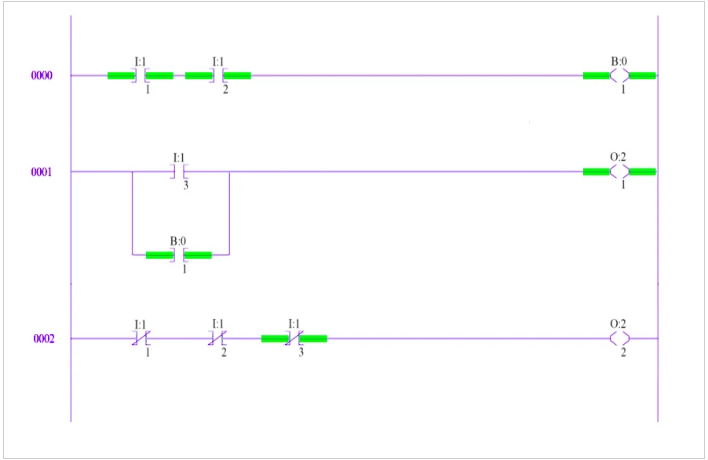

可编程逻辑控制器 (PLC) 中的梯形逻辑

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?

PLC可编程逻辑控制器的常见错误类型以及修复方法

Arm PMC-100可编程MBIST控制器技术参考手册

什么是可编程片上系统?PSOC和FPGA的区别

可编程逻辑器件测试

如何为可编程逻辑和处理器系统多用途 I/O (MIO) 进行IBIS模型名称解码

如何为可编程逻辑和处理器系统多用途 I/O (MIO) 进行IBIS模型名称解码

评论