大规模数据中心、企业服务器或电信交换站使得功耗快速增长,因此高效AC/DC电源对于电信和数据通信基础设施的发展至关重要。但是,电力电子行业中的硅MOSFET已达到其理论极限。同时,近来氮化镓(GaN)晶体管已成为能够取代硅基MOSFET的高性能开关,从而可提高能源转换效率和密度。为了发挥GaN晶体管的优势,需要一种具有新规格要求的新隔离方案。

GaN晶体管的开关速度比硅MOSFET要快得多,并可降低开关损耗,原因在于:

栅极电容和输出电容更低。

较低的漏源极导通电阻(RDS(ON))可实现更高的电流操作,从而降低了传导损耗。

无需体二极管,因此反向恢复电荷(QRR)低或为零。

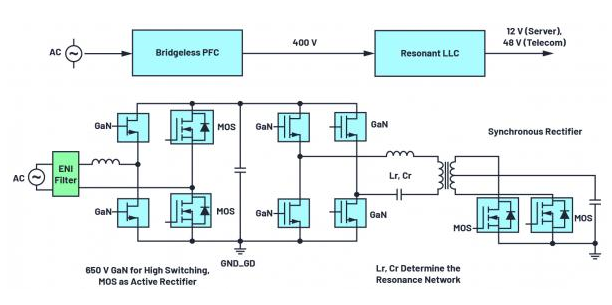

GaN晶体管支持大多数包含单独功率因数校正(PFC)和DC-DC部分的AC/DC电源:前端、无电桥PFC以及其后的LLC谐振转换器(两个电感和一个电容)。此拓扑完全依赖于图1所示的半桥和全桥电路。

如果将数字信号处理器(DSP)作为主控制器,并用GaN晶体管替换硅MOSFET,就需要一种新的隔离技术来处理更高的开关频率。这主要包括隔离式GaN驱动器。

图1.适合电信和服务器应用的典型AC/DC电源

典型隔离解决方案和要求

UART通信隔离

从以前的模拟控制系统转变为DSP控制系统时,需要将脉宽调制(PWM)信号与其他控制信号隔离开来。双通道ADuM121可用于DSP之间的UART通信。为了尽量减小隔离所需系统的总体尺寸,进行电路板组装时使用了环氧树脂密封胶。小尺寸和高功率密度在AC/DC电源的发展过程中至关重要。市场需要小封装隔离器产品。

PFC部分隔离

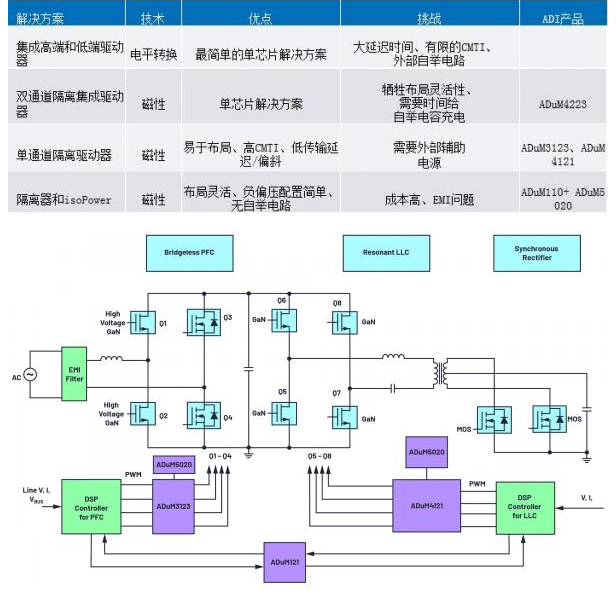

与使用MOS相比,使用GaN时,传输延迟/偏斜、负偏压/箝位和ISO栅极驱动器尺寸非常重要。为了使用GaN驱动半桥或全桥晶体管,PFC部分可使用单通道驱动器ADuM3123,LLC部分则使用双通道驱动器ADuM4223 。

为隔离栅后的器件供电

ADI公司的isoPower?技术专为跨越隔离栅传输功率而设计,ADuM5020紧凑型芯片解决方案采用该技术,能够使GaN晶体管的辅助电源与栅极的辅助电源相匹配。

隔离要求

为了充分利用GaN晶体管,要求隔离栅极驱动器最好具有以下特性:

●最大允许栅电压《7 V

●开关节点下dv/dt》100 kV/ms ,CMTI为100 kV/?s至200 kV/?s

●对于650 V应用,高低开关延迟匹配≤50 ns

●用于关断的负电压箝位(–3 V)

有几种解决方案可同时驱动半桥晶体管的高端和低端。关于传统的电平转换高压驱动器有一个传说,就是最简单的单芯片方案仅广泛用于硅基MOSFET。在一些高端产品(例如,服务器电源)中,使用ADuM4223双通道隔离驱动器来驱动MOS,以实现紧凑型设计。但是采用GaN时,电平转换解决方案存在一些缺点,如传输延迟很大,共模瞬变抗扰度(CMTI)有限,用于高开关频率的效果也不是很理想。与单通道驱动器相比,双通道隔离驱动器缺少布局灵活性。同时,也很难配置负偏压。表1对这些方法做了比较。

表1.驱动GaN半桥晶体管不同方法的比较

图2.在isoPower器件中实现UART隔离和PFC部分隔离,需要采用ISO技术及其要求

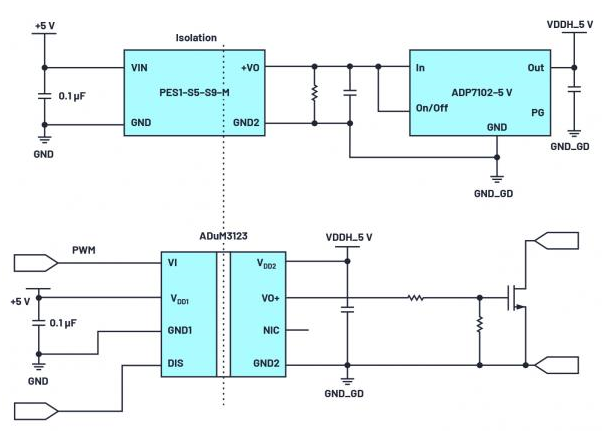

对于GaN晶体管,可使用单通道驱动器。ADuM3123是典型的单通道驱动器,可使用齐纳二极管和分立电路提供外部电源来提供负偏压(可选),如图3所示。

新趋势:定制的隔离式GaN模块

目前,GaN器件通常与驱动器分开封装。这是因为GaN开关和隔离驱动器的制造工艺不同。未来,将GaN晶体管和隔离

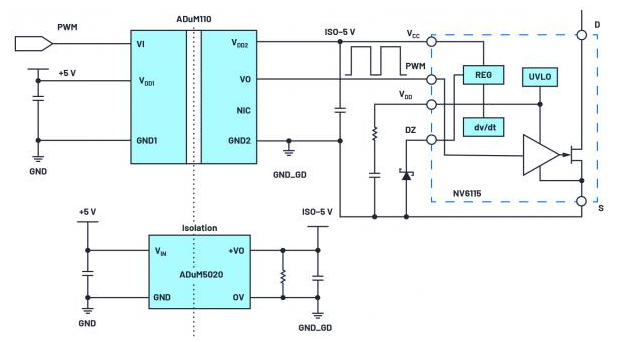

栅驱动器集成到同一封装中将会减少寄生电感,从而进一步增强开关性能。一些主要的电信供应商计划自行封装GaN系统,构建单独的定制模块。从长远来看,用于GaN系统的驱动器也许能够集成到更小的隔离器模块中。如图4所示,ADuM110N等微型单通道驱动器(低传输延迟、高频率)和isoPower ADuM5020设计简单,可支持这一应用趋势。

图3.用于GaN晶体管的单通道、隔离式isoCoupler驱动器

图4.iCoupler ADuM110N和isoPower ADuM5020非常适合Navitas GaN模块应用

结论

与传统硅基MOSFET相比,GaN晶体管具有更小的器件尺寸、更低的导通电阻和更高的工作频率等诸多优点。采用GaN技术可缩小解决方案的总体尺寸,且不影响效率。GaN器件具有广阔的应用前景,特别是在中高电压电源应用中。采用ADI公司的iCoupler?技术驱动新兴GaN开关和晶体管能够带来出色的效益。

责编AJX

-

AD

+关注

关注

27文章

853浏览量

149368 -

晶体管

+关注

关注

76文章

9040浏览量

135137 -

GaN

+关注

关注

19文章

1761浏览量

67838

发布评论请先 登录

相关推荐

GaN晶体管在AC/DC电路设计中的重要性和作用

GaN晶体管在AC/DC电路设计中的重要性和作用

评论