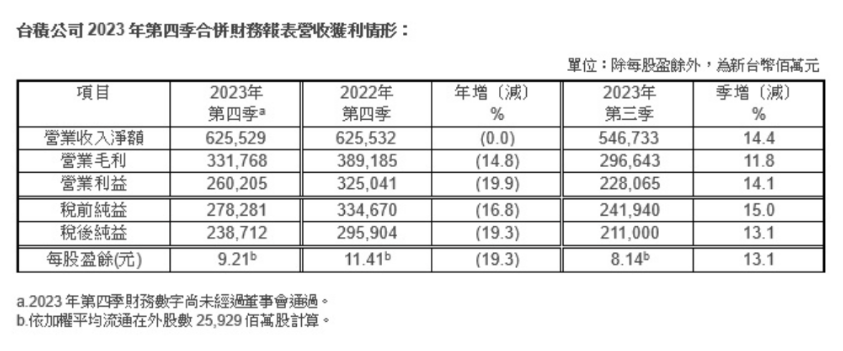

乔治敦大学沃尔什外交学院安全与新兴技术中心(CSET)的两位作者编写的一份题为《AI Chips: What They Are and Why They Matter》的报告,借助模型预估得出,台积电每片5nm晶圆的收费可能约为17,000美元,是7nm的近两倍。

该报告同时估计,每片300mm直径的晶圆通常可以制造71.4颗5nm芯片,这让无晶圆芯片公司的制造成本达到每颗238美元(约为1642元)。

不仅不如,通过对半导体行业和AI芯片设计的调查,作者通过模型不仅估算出5nm芯片238美元的制造成本,还提出了每颗芯片108美元的设计成本以及每颗芯片80美元的封装和测试成本。

这使芯片设计公司为每颗5nm芯片支付的总成本将高达426美元(约为2939元)。

5nm之后“高贵”的先进制程

市场研究机构International Business Strategies (IBS)给出的数据显示,28nm之后芯片的成本迅速上升。28nm工艺的成本为0.629亿美元,到了7nm和5nm,芯片的正本迅速暴增,5nm将增至4.76亿美元。三星称其3nm GAA 的成本可能会超过5亿美元。

设计一款5nm芯片的总成本将高达近5亿美元,那平均到每颗芯片的成本有多高?CSET在报告中的模型类比了英伟达P100 GPU,这款GPU基于台积电16nm节点处制造,包含153亿个晶体管,裸片面积为610 平方毫米,相当于晶体管密度25 MTr/mm2。

由此计算,直径300毫米的硅晶片能够生产71.4颗 610平方毫米的芯片。

假设5nm GPU的芯片面积为610平方毫米,并且晶体管密度比P100 GPU高,达到907亿个晶体管。下表中是用模型估算的台积电90至5nm之间的节点晶体管密度。在90至7nm范围内的节点,模型使用具有相同规格的假想GPU,包括晶体管除晶体管密度,假想的5nm GPU与假设节点关联。

CSET的成本模型使用的是无晶圆厂的角度,包含建造工厂的成本、材料、人工,制造研发和利润等。芯片制造出来后,将外包给芯片测试和封装(ATP)公司。

当然,使用更先进的制程节点芯片设计公司也会有相应的成本增加。最终看来,芯片设计成本和ATP成本之和等于总生产成本,得出每颗5nm芯片支付的总成本将高达426美元成本的结论。

之所以先进制程芯片的成本不断增加,不可忽视的是半导体制造设备成本每年增加11%,每颗芯片的设计成本增加24%,其增长率都高于半导体市场7%的增长率。

2018年的时候,台积电CEO魏哲家就打趣地说,台积电预计在5nm投资了250亿美元,各位就知道以后价格是多少了!

并且,随着半导体复杂性的增加,对高端人才的需求也不断增长,这也进一步推高了先进制程芯片的成本。报告中指出,研究人员的有效数,即用半导体研发支出除以高技能研究人员的工资,从1971年到2015年增长了18倍。

换句话说,摩尔定律延续增加大量的投入和人才。

雷锋网此前报道,为了支撑先进制程,台积电十年内研发人数增加了三倍,2017年研发人员将近6200人,比2008年多了近两倍,这6200人只从事研发,不从事生产。

先进制程的高成本如何影响半导体和AI发展?

半导体市场以超过世界经济3%的速度增长。目前,半导体产业占全球的0.5%经济产出。对于半导体产业而言,先进的制程和高性能芯片驱动着行业的进步,晶体管成为关键。

晶体管尺寸减小使每个晶体管的功耗也降低,CPU的峰值性能利用率每1.57年翻一番,一直持续到2000年。此后,由于晶体管尺寸减小放缓,效率每2.6年翻一番,相当于每年30%的效率提升。

报告中指出,台积电声称的节点进步带来的速度提升和功耗降低,从90 nm和5 nm之间以恒定比例变化,但趋势趋于平稳。三星两种指标在14 nm和5 nm之间都有下降趋势,但缺少大于14 nm的节点处的数据。

不过,由于半导体设备、研发等成本持续增加,这也让大量晶圆代工厂无法参与先进制程的生产和竞争,比如,GlobalFoundries就不生产14 nm以下的芯片。

下表给出了每个工艺节点量产的时间以及代工厂的数量,可以看到,随着制程的向前推进,晶圆代工厂数量越来越少。目前先进的制程工艺代工厂仅剩台积电、三星和英特尔。

虽然代工厂越来越少,但业界对于先进制程的需求并没有减少。AI芯片就对先进制程有不小的需求,最先进的AI芯片比最先进的CPU更快,且具有更高的AI效率算法。AI芯片的效率是CPU的一千倍,这相当于摩尔定律驱动下CPU 26年的改进。

这要求晶体管持续改进,晶体管的改进仍在继续,但进展缓慢。得益于FinFET晶体管的发明,英特尔在2011年推出了商业化的22nm FinFET,业界也基于FinFET将半导体制程从22nm一直向前推进到如今的5nm。

到了2nm,台积电和英特尔都采用GAA(Gate-all-around,环绕闸极)或称为GAAFET维持先进制程的性能提升。魏哲家透露,台积电制程每前进一个世代,客户的产品速度效能提升30%- 40%,功耗可以降低20%-30%。

但高昂的成本和性能提升的幅度减少,让AI公司在计算上花费的时间和金钱更多,进而成为AI发展的瓶颈。

报告指出,AI实验室的训练的费用非常高,估算AlphaGo、AlphaGo Zero、AlphaZero和AlphaStar模型的训练成本每个为5000万到1亿美元之间。

值得关注的是,由于CSET当前正在关注AI和先进计算的进步所带来的影响。该报告称,美国政府正在考虑如何控制AI技术,但由于AI软件、算法和数据集不是理想的控制目标,因此硬件成为了重点。

未来,有多少AI芯片功能能够用得起先进制程?AI在全球的发展又会受到怎样的限制?

责任编辑:tzh

-

芯片

+关注

关注

446文章

47651浏览量

408558 -

封装

+关注

关注

123文章

7209浏览量

141003 -

晶体管

+关注

关注

76文章

9018浏览量

134962 -

AI

+关注

关注

87文章

26301浏览量

263903

发布评论请先 登录

相关推荐

半导体发展的四个时代

半导体发展的四个时代

中国大陆半导体成熟制程产能稳步提升

英特尔推出面向AI时代的系统级代工,并更新制程技术路线图

半导体先进封装技术

台积电2023年Q4营收稳健,先进制程营收占比高达67%

芯片先进制程之争:2nm战况激烈,1.8/1.4nm苗头显露

鑫巨半导体获近亿元A轮融资,用于先进封装IC载板生产装备产业化

英特尔和新思科技深化合作,提供基于英特尔先进制程节点的领先IP

先进制程芯片的“三大拦路虎” 先进制程芯片设计成功的关键

半导体Chiplet技术的优点和缺点

半导体企业如何决胜2023秋招?

“2023年半导体先进技术创新发展和机遇大会”第二批展商公布

先进制程的高成本如何影响半导体和AI发展?

先进制程的高成本如何影响半导体和AI发展?

![[<b class='flag-5'>半导体</b>前端工艺:第二篇] <b class='flag-5'>半导体制程</b>工艺概览与氧化](https://file1.elecfans.com/web2/M00/B1/D7/wKgZomVdeemAEcbqAAInhahz1Ko856.png)

评论