为了向当今的大电流,低压PCB上的负载提供指定的电源电压,设计人员必须通过了解可用的解决方案及其权衡因素,将IR压降降低。

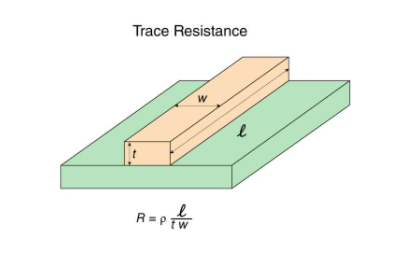

尽管低功耗组件的大量使用,但当今的印刷电路板(PCB)仍需要大量电流,而常用的电路板消耗50、100甚至200 A的电流。每当电流传递给负载时,都会存在基于IR的压降,设计人员在对电路板进行布局以及放置电源,直流电源轨和负载时必须考虑这一损耗。为了保持一致和可靠的运行,重要的是要确保该压降不会将这些直流电源电压推到其频带的下限。通常,它是标称值的正负几个百分点。诸如FR-4之类的PCB层压板上的铜(之所以称呼是因为每平方英尺重1盎司),厚度为35 µm;2盎司 当然,铜的厚度是原来的两倍,而“薄”的铜则只有一半。使用1盎司。铜作为一个例子,一个10厘米长,1毫米宽的跟踪将具有约50μm的电阻Ω(铜的电阻率是1.74 × 10 -8 Ω⋅m在20 ° C)。有许多方便的在线电阻计算器,例如Trance-Cat的 计算器(图1)。

图1

如果通过该走线提供10 A电流,则IR压降约为500 mV(0.5 V),这是很大的。这意味着负载处的直流电源电压比电源电压低一半,而且还浪费了功率(I 2 R)和伴随的散热。请注意,压降不是电源轨标称电压值的函数,它仅取决于电流和电阻。因此,一个15 V的电源轨的损耗与一个3 V的电源轨相同,但是在较低的电压下,比例损耗要大得多。情况可能变得更糟。某些设计将低电阻接地层(通常作为独立的PCB层)用于模拟和数字信号接地以及dc电源返回接地。但是,许多设计都受益于(或要求使用)信号和电源接地的单独接地路径,以降低噪声,甚至可以使用单独的直流回路。在这种情况下,IR压降实际上增加了一倍,其中一个压降使电源输出轨负载,而第二个压降使负载电流返回电源。

克服红外压降

设计人员有多种选择可降低IR压降:在中间总线转换器(IBC)布置中使用较高电压的直流电源轨,例如48 V或12/12 V dc,然后在靠近各自的位置放置多个本地负载点(PoL)dc-dc转换器负载。这解决了IR下降问题(并且还大大减少了导轨中的噪声吸收),但是却增加了DC-DC转换器和PCB面积的成本。尽管如此,它还是一种较多使用且有效的解决方案。调整直流标称电源值以预补偿IR压降。这是一种有效的“解决方法”,但同时也带来了一些风险。

-某些其他非常好或偏爱的耗材无法调节,因此必须排除在外。

-如果在使用过程中负载电流需求下降(几乎总是如此),则IR下降也将下降,并且电源实际上可能会提供过高的电源电压。

-如果必须在现场更换电源,则可能无法将补偿设置为补偿电压或调整不当,从而导致电路无法正常工作或电路断断续续。

使用远程感测,这是某些耗材支持的开尔文感测的一种变体。电源具有两条额外的引线,因此,即使IR下降和负载发生漂移,它也可以检测负载处的电压并动态调整其输出以保持该值。这是有效的,但也有缺点:

-传感反馈回路的动态响应可能不够快而无法补偿,或者可能太快,过冲和振荡。

-感测引线形成物理上较大的反馈环路,可能会吸收系统噪声,从而导致电源误读所感测的值;再次,这甚至可能引起供电轨的振荡。

考虑其他解决方案

所有这些选项都在使用中,并且它们都可以在定义明确且受控的条件下工作,但是它们都是“解决方法”和“补丁”,它们是从技术上更强大,更可靠的解决方案,其减少了跌落。同样,还有选择和权衡:

使用较厚的铜包层;2盎司 甚至3盎司 可用。厚度加倍会使电阻减半,但这样做会增加原始PCB材料的成本并增加板重;将更多的铜放到不需要的地方;并且由于化学蚀刻或附加电镀所需的额外时间而增加了制造时间,这是可以创建PCB铜路径的两种方式。

使用更宽的PCB走线;同样,将宽度加倍会使阻力减半。但是,成本是这些直流电源轨及其接地回路的额外PCB“不动产”。一些先进的布局会尽可能使用较宽的走线,但也会通过缩小走线来避开板上的障碍物和狭窄的间隙区域。如果10厘米的行程仅在行程的一厘米处狭窄,则电阻的增加显然仅发生在该短段上。

使用立式母线(也拼写为母线或母线)来布线电源,从而使用未使用的z轴(高度)尺寸。即使该板是薄型SMT设计,通常也会留有相对较厚的薄型母线的净空,因此它提供了低电阻的直流路径。这些杆中有许多是作为两层(或多层)结构提供的,一层用于一个或多个供电轨,另一层用于接地回路。成本只是BOM组件成本,对PCB本身的影响很小,因为它们不需要更厚的铜,更宽的走线或其他解决方法。

母线的厚度,高度层,引脚间距和长度范围很广。例如,E-Fab提供的一个母线具有两个铜层,这些铜层被绝缘体隔开(图2)。这些层具有交错的PCB引脚配置,以便引脚交替供电和接地。

图2

母线排提供了另一个“免费”的好处:它们使PCB变硬以防挠曲,这是大型板或在振动环境(军用/航空,汽车和许多其他应用)中要考虑的问题。某些设计仅将母线用于较高电流的负载,例如MOSFET或IBGT。这样可以降低其适度的成本,并减轻与电池条相关的布局问题(如果有),同时提高其有效性。

结论

从纯电气的角度来看,确保来自电源的全部标称电压到达负载,并以不明显的IR电压损耗或I 2R功耗达到负载,这对于可靠的非间歇性能至关重要。每个问题的解决方案都需要权衡,没有标准答案,但是每个问题的缺点都应仔细理解和评估。

编辑:hfy

-

pcb

+关注

关注

4220文章

22468浏览量

385661 -

印刷电路板

+关注

关注

4文章

718浏览量

34785 -

DC-DC转换器

+关注

关注

10文章

597浏览量

55213 -

总线转换器

+关注

关注

0文章

9浏览量

9652

发布评论请先 登录

相关推荐

PCB设计上如何将IR压降降低

PCB设计上如何将IR压降降低

评论