下一代航天和国防以及测试和测量系统带宽从10s到100s MHz横跨到GHz的瞬时带宽。相控阵雷达、5G无线测试系统、电子战以及数字示波器的发展趋势正在推动业内向更高带宽发展,并且大幅增加系统中的通道数量。

这些趋势使包括数据转换器、时钟和电源等组件的信号链设计变得复杂化。选择合适的数据转换器、同步多个通道以及优化电源,对于在多个通道上实现必要的带宽至关重要。

选择适合的数据转换器

每个系统架构都是从对系统性能影响最大的器件开始;在宽带系统中,最先开始的就是数据转换器。选择哪一款数据转换器取决于您对以下问题的回答:

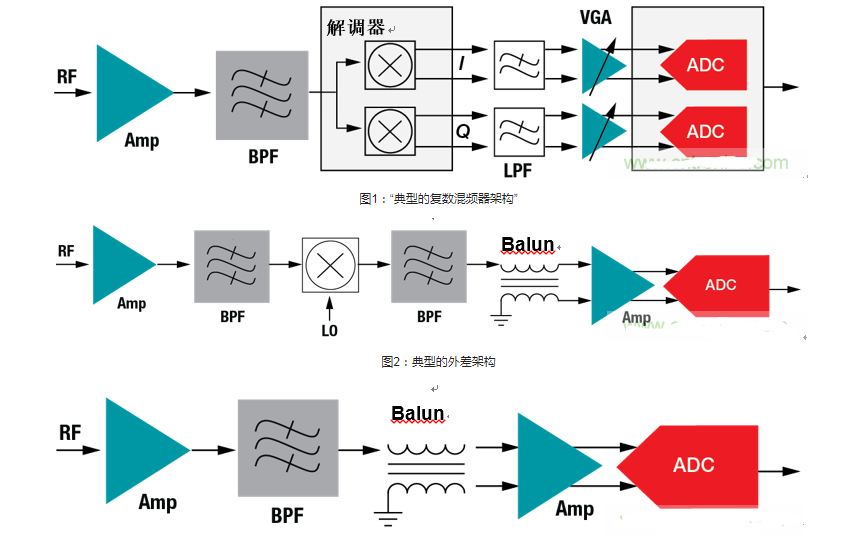

您是否会使用零中频(IF)/复数混频器架构(如图1所示)?

● 优势:模数转换器(ADC)的输入带宽和采样率低于其他架构,由此可简化或消除滤波。

● 劣势:对于I和Q路径,每个天线元件需要两个ADC通道,且混频器图像可能会降低系统性能。

您是否会使用外差法(如图2所示)?

● 优势:您只需要一个数据转换器通道,且ADC输入带宽低于射频(RF)采样。

● 劣势:需要一个或多个混频器,信号图像和产生的谐波会使滤波复杂化;很难调整响应频率;必须移动本地振荡器(LO)。

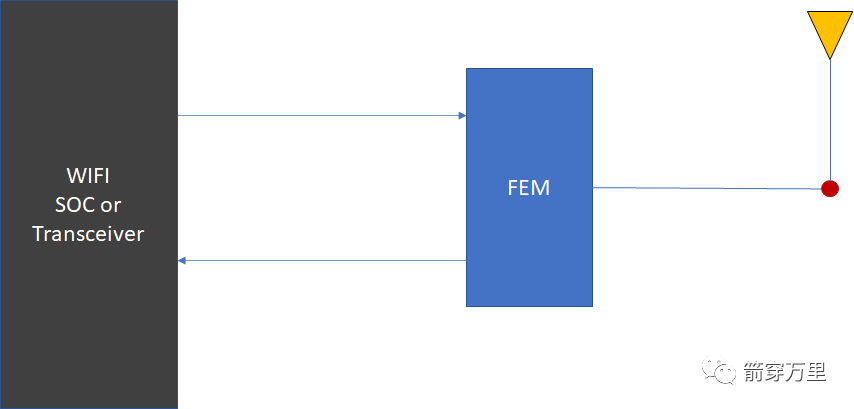

您是否会使用直接射频采样(如图3所示)?

● 优势:由于信号链简化,不再需要混频器;且使用数字下变频器(DDC)和数控振荡器(NCO)可以很轻松以数字方式调整频率。

● 劣势:最高信号频率必须在ADC的输入带宽内;需要进行频率规划以实现最高性能。

图3:典型的射频采样架构

您需要测量的最宽带宽信号是什么?

● 数据转换器的采样率至少应为直接采样信号瞬时带宽的2.5倍,或是零中频的1.25倍。

● 为获得最佳性能,约为瞬时带宽10倍的采样率将使您更轻松避免信号谐波和杂散。

TI的射频采样频率规划器、模拟滤波器和DDC Excel计算器可以满足频率规划和滤波要求,并向您展示信号的复杂数字抽取效果。

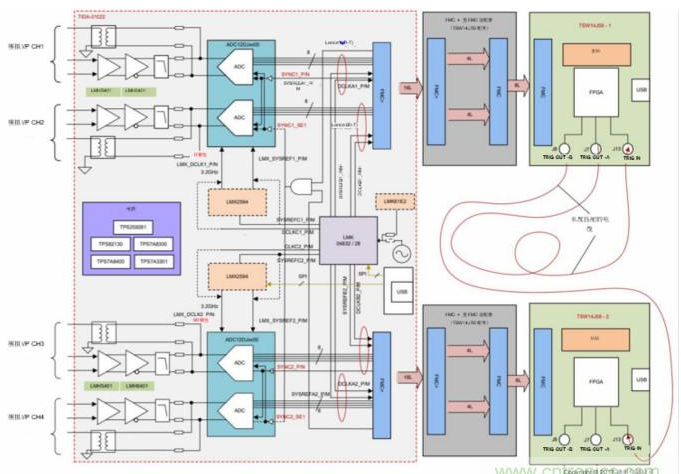

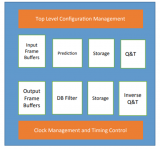

如前所述,宽带系统需要高采样率转换器。例如,信号带宽为1 GHz的射频采样系统可以从带~10-GSPS转换速度的数据转换器中受益,从而避免信号谐波。目前,TI最快的转换器是ADC12DJ3200,它是一种12位ADC,可在双通道模式下每通道运行3.2 GSPS或在单通道模式下运行6.4 GSPS。但即使在单通道模式下,它也不能满足所需的10-GSPS速度。为了满足这一要求,适用于DSO、雷达和5G无线测试系统的灵活3.2GSPS多通道AFE参考设计将两个ADC12DJ3200组合在一块板上,如图4所示。

图4:多通道AFE参考设计框图

此参考设计提供了系统灵活性,因为它可以在四通道、3.2-GSPS模式或双通道、6.4-GSPS模式下运行,或者作为一个单通道以高达12.8 GSPS的速度运行。我们的适用于高速示波器和宽带数字转化器的12.8-GSPS模拟前端参考设计说明了两个ADC的板载交错。

现在,随着我们新的双通道5.2-GSPS ADC12DJ5200RF的推出,您的下一代设计将具有更高的性能和灵活性。由于ADC12DJ5200RF与ADC12DJ3200兼容引脚,我们很快就可以修改现有的参考设计,且现在可以提供适用于12位数字转换器的可扩展20.8GSPS参考设计。在20.8GSPS时,器件的整个8-GHz输入带宽可以在单个捕获中实现数字化。

设计时钟架构

选择数据转换器之后,就必须设计一个时钟架构。为单个数据转换器提供时钟非常简单,但是许多系统,比如我们的交错设计,需要同时为多个转换器提供时钟。例如,大型相控阵系统可以有数百个或数千个通道。而TI有多个器件和参考设计来应对此设计挑战。

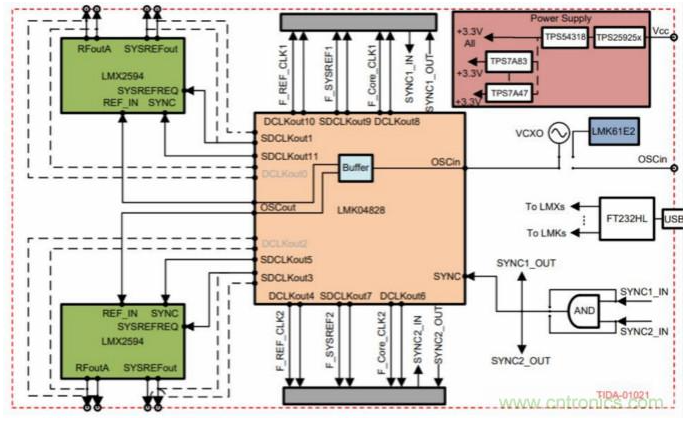

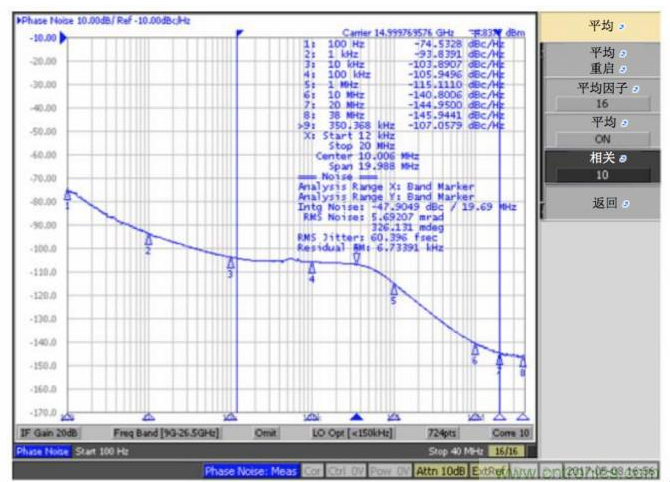

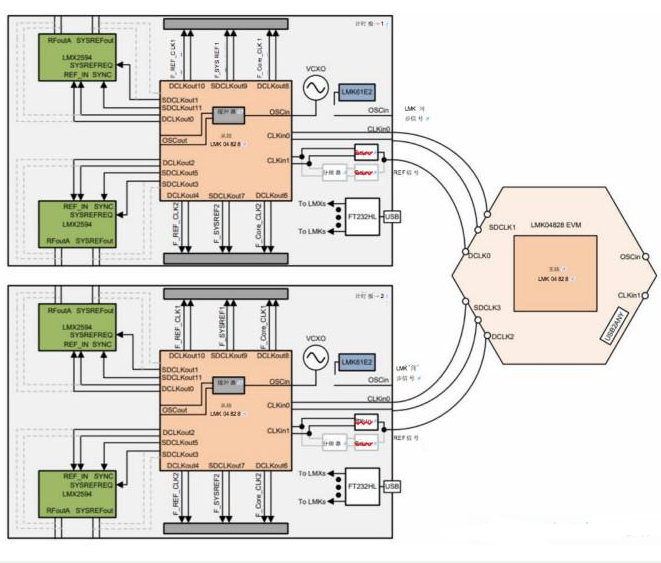

我们的适用于DSO、雷达和5G无线测试仪的多通道JESD204B 15-GHz时钟参考设计是一个完整的时钟子系统。此设计(如图5所示)包含如LMK61E2可编程振荡器和LMK04828等多个时钟参考,一个带有14个独立时钟输出的时钟分配器件,以及两个可提供高达15 GHz的超低相位噪声时钟的LMX2594锁相环/合成器(如图6所示)。此外,LMX2594还可以为带JESD204B接口的数据转换器生成同步SYSREF时钟。LMX2594还能够跨越多个设备同步时钟的相位。在参考设计中,您可以找到多个频率下的相位噪声图(如图6所示),并发现通道到通道偏斜的测量值小于10 ps。

图5:多通道JESD204B 15-GHz时钟框图

图6:15 GHz时的LMX2594相位噪声

根据配置,该电路板最多支持两个数据转换器和两个现场可编程门阵列(FPGAs),且可轻松适应多达六个转换器和一个FPGA的时钟。然而,许多系统需要更多的通道。对于这类情况,我们的适用于雷达和5G无线测试仪的高通道数JESD204B时钟生成参考设计和适用于雷达和5G无线测试仪的高通道数JESD204B菊链时钟参考设计能够在树形结构(如图7所示)或菊花链配置中运行时钟。您可以使用这些方法扩展到数千个通道,同时对系统性能的影响降至最低。

图7:JESD204B时钟生成参考设计树形结构框图

电源设计

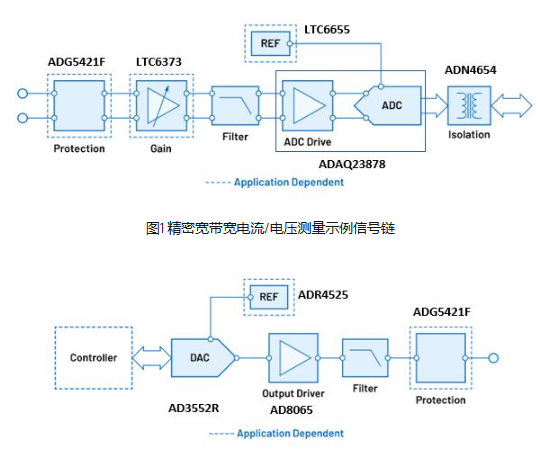

一旦时钟架构确定,那么下一个挑战就是电源设计。由于数据转换器和时钟对DC/DC转换器的开关噪声敏感,所以大多数电源设计人员都会采用带低噪声、低压差稳压器的DC/DC转换器(LDO)。然而,经过精心布局和过滤,在许多电源上经常不需要LDO。

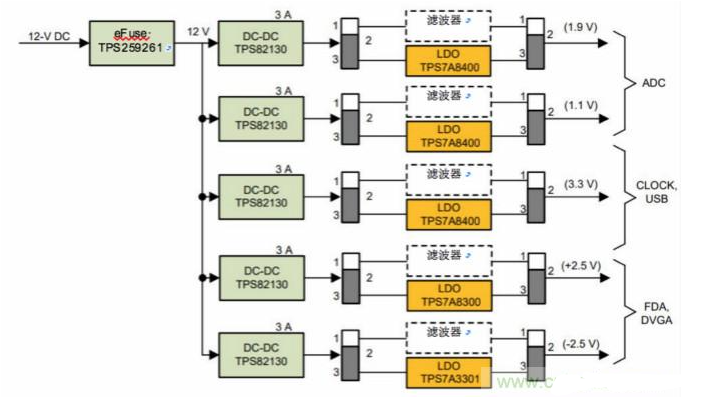

前面提到的3.2-GSPS多通道模拟前端参考设计具有一个完整电源,包括DC/DC稳压器和LDO,如图8所示。此设计上的LDO可以用滤波器绕过,以测试哪些电源对开关噪声最敏感。我们的测试证实,绕过LDO时不会对设计的性能产生任何影响,也表明了电源效率增高的额外好处。

图8:3.2-GSPS多通道AFE参考设计电源框图

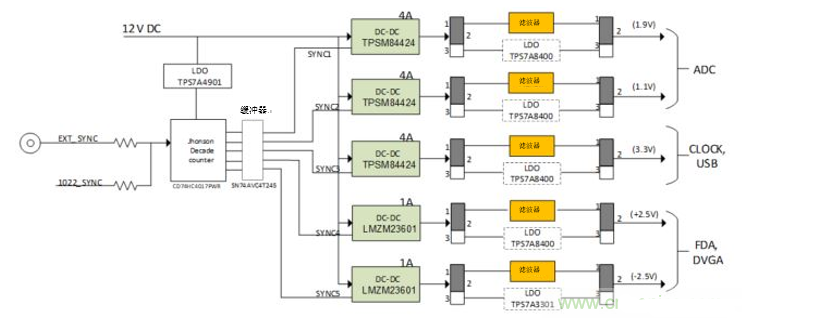

该电路板包含一系列沿顶部的排针引脚,这些排针引脚支持新的设计绕过板载电源解决方案,例如我们的可最大限度提高12.8GSPS数据采集系统性能的低噪声电源参考设计(如图9所示),能够同步所有DC/DC稳压器与主时钟,从而更容易滤除转换器开关噪声。此外,您可以将时钟的相位移到每个转换器,以便所有转换器不会同时切换,从而降低总开关能量。最后,参考设计上的DC/DC转换器更加高效,降低了电路板上的总功耗。与最初设计一样,LDO仍然可以被绕过。

图9:低噪声电源参考设计框图

编辑:hfy

-

转换器

+关注

关注

27文章

8163浏览量

141511 -

DC-DC转换器

+关注

关注

10文章

593浏览量

55202 -

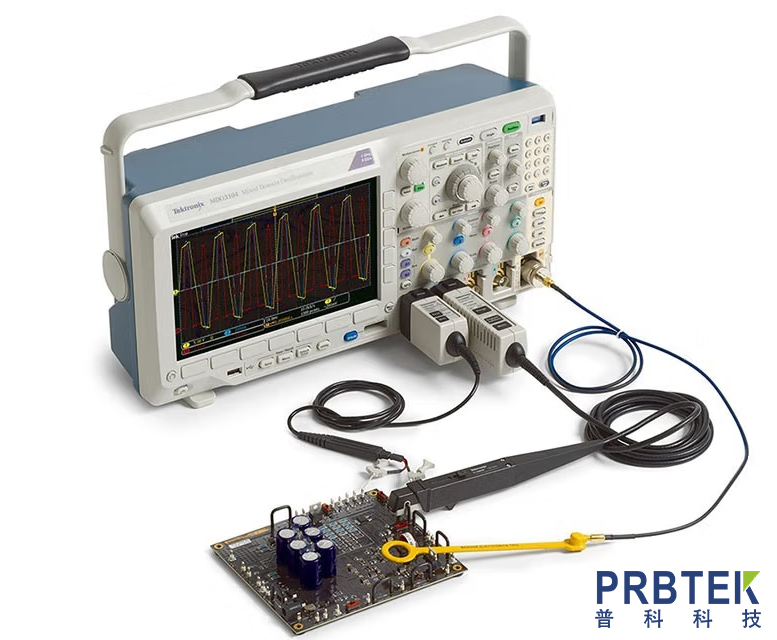

数字示波器

+关注

关注

6文章

476浏览量

33231 -

数据转换器

+关注

关注

1文章

335浏览量

27782 -

低噪声电源

+关注

关注

0文章

6浏览量

5799

发布评论请先 登录

相关推荐

智能座舱主流音频架构设计方案

TAU1312 多系统多频 RTK 定位模块

商城库存系统中心架构设计与实践案例

常用射频系统架构设计方案

SWE.2软件架构设计

5G+能源管理系统架构设计方案

基于分级安全的OpenHarmony架构设计

FPGA设计中动态时钟的使用方法

多通道系统宽带宽信号测量及时钟架构设计方案

多通道系统宽带宽信号测量及时钟架构设计方案

评论