作者:Kendall Castor-Perry

在一些关于驱动采样ADC的文章中,谈到了电阻和电容影响输入端的稳定性。这个问题能被提出来是好事,但在我看来,处理方式似乎总是有点经验主义,却并没解释那些经验从何而来。你们都想知道原因的,对吧?这里是我多年前做过的一些仿真试验,相信可以对此作出一些解释。

高速ADC将输入电压采样到内部电容上,因此存在充电电流。在为电荷转移保留的一小段采样周期时间内,必须获取快速变化的输入电压以实现高精确度。输入端子和采样开关之间通常没有缓冲。因此,电荷流的时域性能由内部电容器和充电电流通路(包括芯片外部和内部)的阻抗之间形成的时间常数来确定。

充电过程不是由ADC设计人员或数据表编写人员控制的。如果外部阻抗影响充电波形(读数器亦如此)的稳定性,则可能阻碍输入电压在规定时间内达到足够的精度。与电平和斜率相关的误差也会随之出现,甚至在低频输入信号上出现增益和线性问题。

这样的ADC作为一个采样数据系统却不适合做连续瞬态分析——这真让人惊讶!然而,采样周期内的充电完全可以由等效输入网络对表示时钟的电压阶跃输入的响应来预测。用时钟作为输入信号,在时域中将组合的外部和内部网络仿真为滤波器(嘿,想到这一点了吗?),便可检查外部元件的影响。这种方法在下一个时钟边缘之外是不准确的——但如果到那时系统还未稳定下来,那这个系统就会完全不准确。

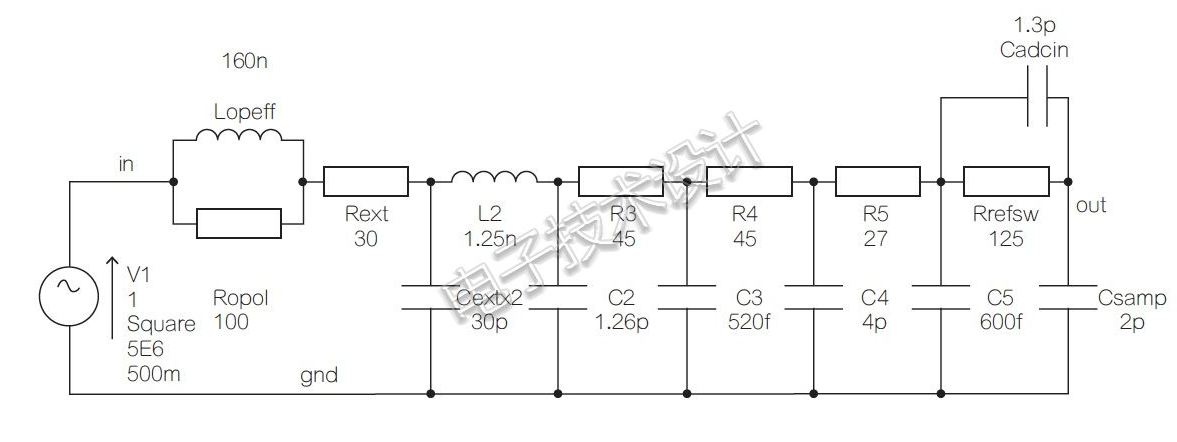

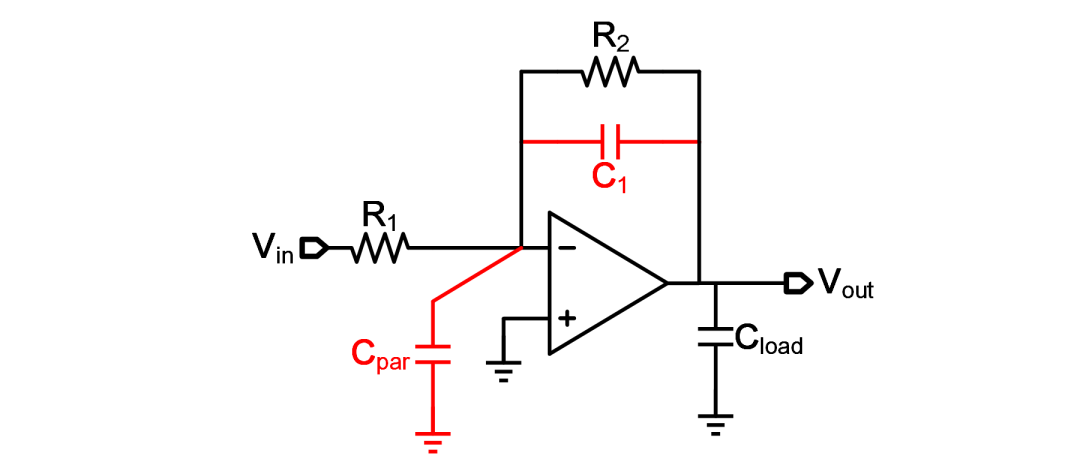

等效电路如图1所示,它源自一款现在已经相当过时的Burr-Brown ADC的原理图,其中有一个拓扑改变以方便仿真,即重新安排梯形电路的最后一个分支,让2pF采样电容接地;而且,整个电路是这个差分电路的单端等效电路。与外部元件相比,内部细节影响不大。

图1:基本电路分析。

对于80MHz转换器来说,输入为5MHz方波是较慢的采样速率,这说明外部元件值虽然看起来合理,但也可能导致不好的稳定性。文中的图显示了采样电容器上电压的稳定性。忽略三个时钟周期中的第一个(仔细观察它与其它周期的细微差别),我并没有让电路达到稳定状态,好吧,这是我的错。

这里展示了对三个参数的扫描:电容Cextx2、串联电阻Rext和缓冲器Lopeff的有效电感(类似积分器的放大器噪声增益带宽将其输出电阻Ropol转换为电感)。

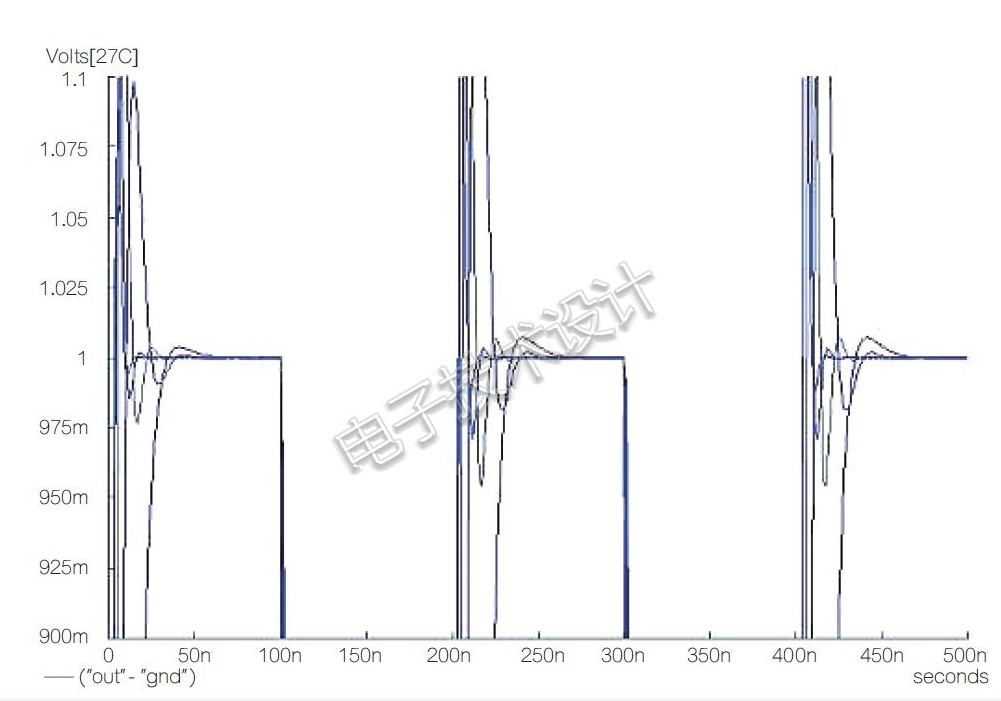

布局电感包括在内,但源阻抗的电感元件完全由驱动放大器的上升闭环输出阻抗支配。改善这种系统的稳定性的主要原因是使用了宽带放大器,而不是放大器输出级能有效驱动ADC不良输入阻抗这类略而不证的断言。现在开始扫描。首先是电容Cextx2(图2):

图2:在3pF和300pF之间扫描输入电容(最慢速度)。

随着电容器数值的增加,波形受到的阻尼效果变得更好,但稳定所需的时间却更长。这里,Rext=30Ω,Lopeff=160nH(对应具有100Ω开环Ropol和100MHz噪声增益带宽的放大器)。无论通过什么方法来改善实际波形,增大电容都将延长稳定时间。所以对于高速系统,应该使该电容尽可能小。接下来,我们扫描电阻Rext(图3):

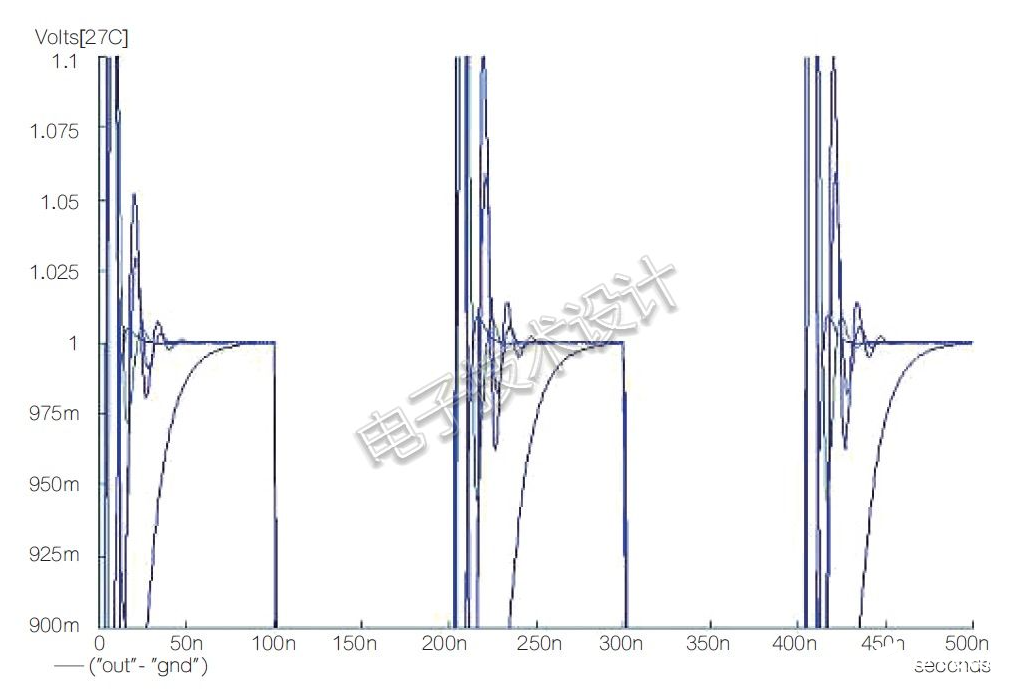

图3:在3Ω和300Ω之间扫描外部电阻(最慢速度)。

扫描该电阻会改变外部RC时间常数,但由于串联电压下降,增大Rext比增大Cextx2具有更显著的效果。这里Cextx2=30pF,Lopeff=160nH。增大电阻值改善了在输入端形成的谐振电路阻尼,特别是当输入电容值较小时,但这同时也降低了系统速度。由于源电感增加(即运算放大器的噪声增益带宽减小),电阻器数值也需要增大,以保持较好的采集波形。

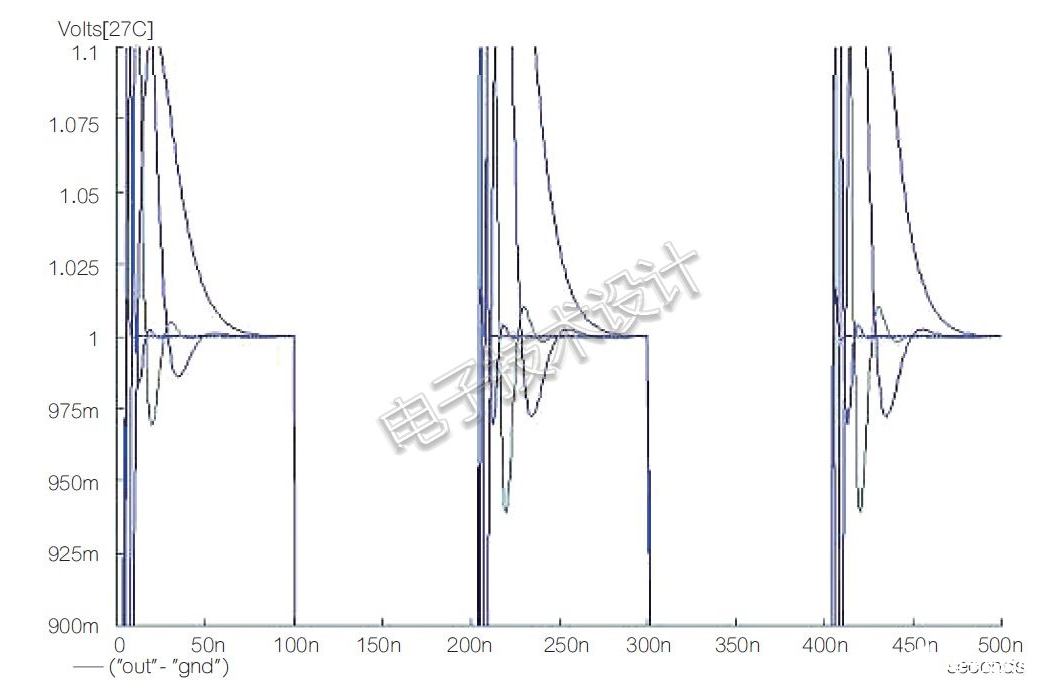

现在来看看电感——实际上我们是扫描放大器的GBW。图4显示了将放大器的噪声增益带宽从1000MHz降低到10MHz的影响,此时Rext=30Ω,Cextx2=30pF。如同所预料的,使用较慢的运算放大器显著延长了稳定所需的时间。此外,较大的过冲可能会导致输入极问题。

图4:在16nH和1600nH之间扫描有效的源电感(最慢速度)。

随着运算放大器GBW的降低,干净采集时间(采用最恰当的Rext和Cextx2)也会增加,这表明较慢的缓冲放大器可能根本无法以所需的速度实现准确采集。波形的变化表明,如果三个主要外部元件中任意一个的值固定不变(比如运算放大器不能改变,或ADC有一个较大的Cin),就需要优化其他两个元件来获得良好的性能。值得注意的是,这个固定值的选择有可能根本无法实现所需的稳定时间!

希望上面的分析能让你明白问题可能出现在哪里,以及如何在系统中查找问题——亲自尝试一下吧!

编辑:hfy

-

电容器

+关注

关注

63文章

5811浏览量

96760 -

转换器

+关注

关注

27文章

8200浏览量

141737 -

运算放大器

+关注

关注

211文章

3983浏览量

170670 -

adc

+关注

关注

95文章

5648浏览量

539421 -

波形

+关注

关注

3文章

343浏览量

31244

发布评论请先 登录

相关推荐

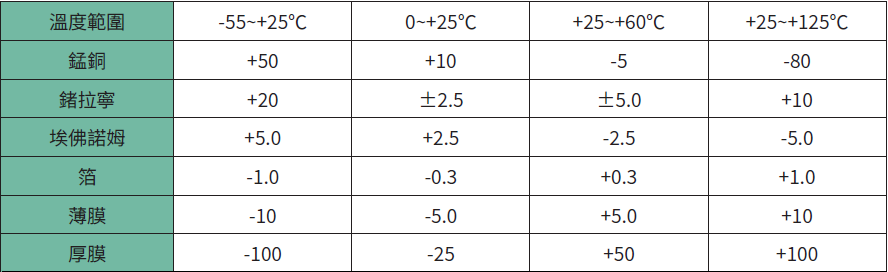

什么是热电偶稳定性?影响热电偶稳定性的主要因素

晶振的频率容差定义 振荡器稳定性的重要性 影响频率稳定性的因素

什么是晶振的频率稳定性?如何确保晶振的稳定性呢?

为了稳定性必须在MOSFET栅极前面放一个100Ω电阻吗

探讨关于驱动采样ADC的电阻和电容影响输入端的稳定性

探讨关于驱动采样ADC的电阻和电容影响输入端的稳定性

评论