组合逻辑电路设计实验报告

一、实验目的

1.加深理解组合逻辑电路的工作原理。

2.掌握组合逻辑电路的设计方法。

3.掌握组合逻辑电路的功能测试方法。

二、实验环境

1、PC机

2、Multisim软件工具

三、实验任务及要求

1、设计要求:

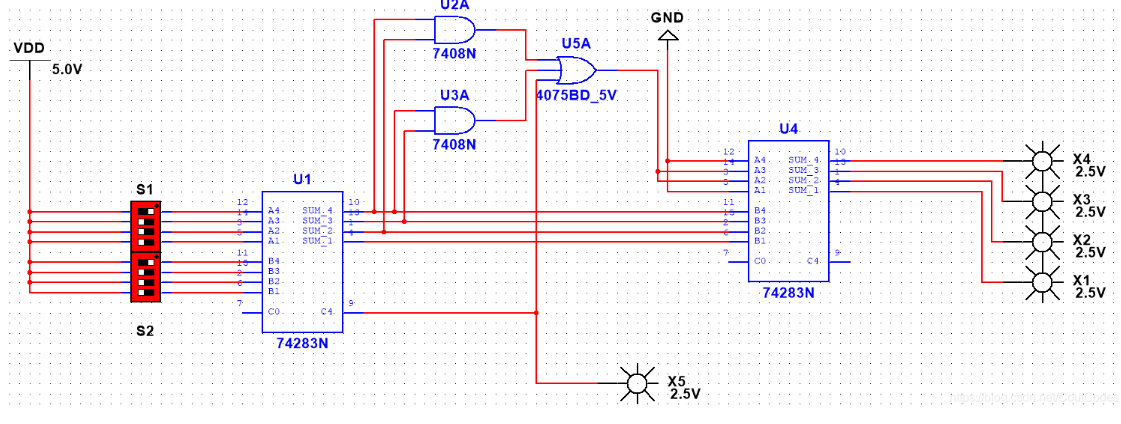

用两片加法器芯片74283配合适当的门电路完成两个BCD8421码的加法运算。(输入两个以BCD8421码表示的十进制数,输出也是以BCD8421码表示的和,并用数码管显示出来。)

2、实验内容:

按要求完成上述电路的功能。

验证其功能是否正确。

四、实验设计说明(简述所用器件的逻辑功能,详细说明电路的设计思路和过程)

1.所用器件及其逻辑功能

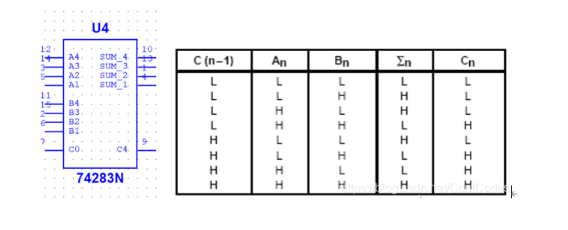

74283是一个超前进位的4位全加器,可以搭配逻辑门组4位二进制加减法器。

由上述真值表可以得到SUM_i和Ci的逻辑表达式如下:

SUM_i= Ai+Bi+Ci-1 Ci= AiBi+(Ai+Bi)Ci-1

2. 电路的设计思路和过程

(1)分别用两个四位二进制数表示两个十进制数,如用A3A2A1A0表示被加数,用B3B2B1B0表示加数,用S3S2S1S0表示“和”,用C表示进位。

(2)由于BCD8421码仅代表进制的0—9,所以加法修正规则当>9时,修正值为当S》9时,修正值为D3D2D1D0=0110(加6进行修正),而这又细分为三种情况,SUM_4∩SUM_4=1,SUM_4∩SUM_3=1,和进位;当S《9时,修正值为D3D2D1D0=0000。

(3)由真值表得:D3=D0=0,D2=D1=C4 + S4S3 + S4S3

五、实验电路(画出完整的逻辑电路图和器件接线图)

六、总结调试过程所遇到的问题及解决方法,实验体会

1、设计过程中遇到过哪些问题?是如何解决的?

对于软件的操作还不够熟悉,进行百度软件的使用教程进行学习,使自己更加清除的了解原件的添加位置。

2、通过此次组合逻辑电路实验,你对组合逻辑电路的设计是否有更清楚的认识?若没有,请分析原因;若有,请说明在哪些方面更加清楚。

有,对组合逻辑电路中规模集成芯片的认识更深了,对于加法器的认识也更加深入,通过这次实验也更加深刻的理解了他的真正函数式。

时序逻辑电路设计实验报告

一、实验目的

1.加深理解时序逻辑电路的工作原理。

2.掌握时序逻辑电路的设计方法。

3.掌握时序逻辑电路的功能测试方法。

二、实验环境

1、PC机

2、Multisim软件工具

三、实验任务及要求

1、设计要求:

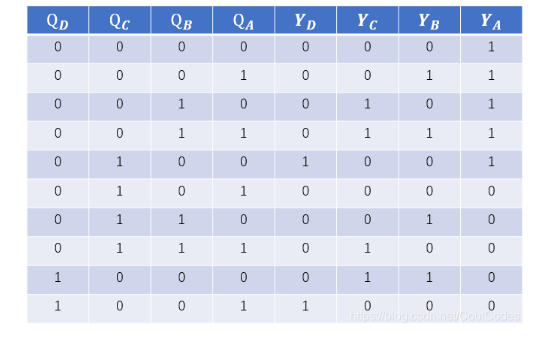

要求设计一个计数器完成1→3→5→7→9→0→2→4→6→8→1→… 的循环计数(设初值为1),并用一个数码管显示计数值(时钟脉冲频率为约1Hz)。

2、实验内容:

(1) 按要求完成上述电路的功能。

(2) 验证其功能是否正确。

四、实验设计说明(简述所用器件的逻辑功能,详细说明电路的设计思路和过程)

1.所用器件和逻辑功能

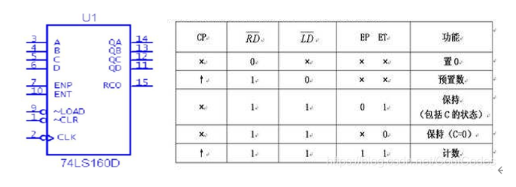

74160计数器:同步十进制计数器

2.电路的设计思路和过程

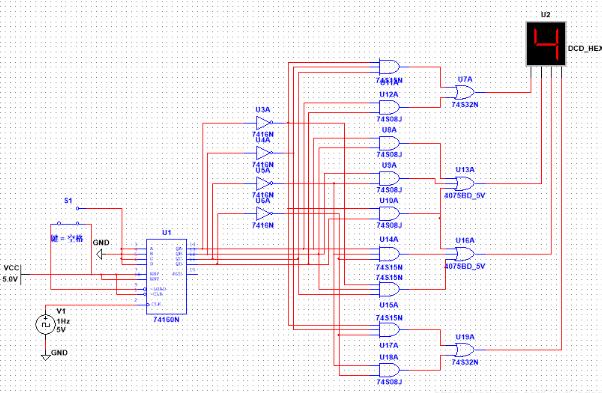

(1)本实验选用一个74160十进制计数器进行计数、控制显示,数字显示器进行数字循环显示。

(2)电路设计思路及过程:利用输入关系和输出关系,获得如下真值表:

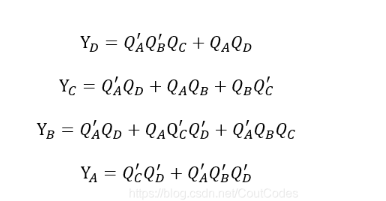

利用卡诺图化简法获得真值表达式:

并根据真值表达式,连接电路图,即可完成要求。

五、实验电路(画出完整的逻辑电路图和器件接线图)

六、总结调试过程所遇到的问题及解决方法,实验体会

1、设计过程中遇到过哪些问题?是如何解决的?

一开始是想使用老师说所的触发器和门电路设计电路图的,但是在完成的过程中,因为对于触发器并不是十分的熟悉,在完成电路的连接之后,始终无法获得正确的答案,无奈之下选择另辟蹊径,直接选择输入和输出的对应关系的真值表达式来连接电路,并且最终完成。

2、通过此次时序逻辑电路实验,你对时序逻辑电路的设计是否有更清楚的认识?若没有,请分析原因;若有,请说明在哪些方面更加清楚。

有,本次实验尝试了两种方法完成。第一种是利用了D触发器,第二种是利用计时器完成。通过这次实验,我对时序电路涉及到的器件更熟悉,对中规模集成电路芯片的认识更深,也掌握了时序逻辑电路的设计方法和任意进制计数器的构成方法。

编辑:hfy

-

电路设计

+关注

关注

6563文章

2316浏览量

195222 -

计数器

+关注

关注

32文章

2121浏览量

92927 -

触发器

+关注

关注

14文章

1675浏览量

60390 -

组合逻辑电路

+关注

关注

6文章

59浏览量

14490

发布评论请先 登录

相关推荐

时序逻辑电路设计

时序逻辑电路设计

时序逻辑电路

两款时序逻辑电路设计实验方案报告解析

两款时序逻辑电路设计实验方案报告解析

评论