综合(Synthesis)是指将RTL设计转换为门级描述。Vivado开发套件中的综合工具是一款时序驱动型、专为内存使用率和性能优化的综合工具,支持System Verilog 2012、Verilog 2005、VHDL 2008、混合语言中的可综合子集,以及XDC设计约束文件(基于工业标准的SDC文件),此外还支持RTL属性来控制综合细节。

综合设置选项

在Flow Navigator中点击Settings,切换到Synthesis标签中:

1.Constraints部分

选择用于综合的约束集,一个约束集是一组XDC约束文件,默认选择状态为active的约束集。设计约束分两种:

物理约束:定义管脚布局、单元(如块RAM、查找表、触发器等)布局的的绝对或相对位置;

时序约束:定义设计的频率需求。如果没有时序约束,Vivado会根据布线长度和布局拥挤度优化设计。

2.Options部分

选择综合运行时使用的策略(strategy)。Vivado提供了几种预定义的策略,后文将讲述如何创建自定义策略。这里给出综合策略中每个设置选项的含义:

flatten_hierarchy:定义综合工具如何控制层次结构(比如模块之间的调用),选择将所有层次展开融为一体进行综合,还是分别独立综合再连接到一起。

none表示从不展开层次结构,综合输出与原始RTL有相同的层次;

full表示全部展开层次结构,只留下顶层;

rebuilt让综合工具展开层次结构后进行综合,综合后再按原始RTL重建层次结构。这样既保留了跨界优化的好处,又让最终层次结构与RTL类似,便于分析。

gated_clock_conversion:选择是否将门控时钟转换为使能信号。设计中应该避免使用门控时钟,需要的时钟信号应尽可能由MMCM/PLL产生。转换过程需要与RTL属性配合工作,具体在第24篇介绍。

bufg:设置综合工具可以从设计中推断出多少个BUFG。比如使用默认的12时,如果RTL中实例化了3个BUFG,那么综合工具最多还可以推测出9个没有明确实例化的BUFG。

fanout_limit:设置一个信号的最大驱动负载数量,如果超出了该限制,就会复制一个相同的逻辑来驱动超出的负载。这里只是一个总体设置,在RTL设计中还可以使用RTL属性进行更具体的设置,具体在第24篇介绍。

directive:设置Vivado综合运行时擦爱去的优化方式,具体包括

Default,默认设置。

RuntimeOptimized,执行最短时间的优化选项,会忽略一些RTL优化来减少综合运行时间。

AreaOptimized_high/medium,执行一些通用的面积优化。

AlternateRoutability,使用算法提高布线能力,减少MUXF和CARRY的使用。

AreaMapLargeShiftRegToBRAM,将大型的移位寄存器用块RAM来实现。

AreaMultThresholdDSP,会更多地使用DSP块资源。

FewerCarryChains,位宽较大的操作数使用查找表(LUT)实现,而不用进位链。

retiming:启用该功能,可以通过在组合门和LUT之间移动寄存器(达到寄存器平衡状态)提高内部时钟时序路径的电路性能。该功能会保留原来的功能和电路延迟,也不需要改变RTL源文件。

fsm_extraction:设置综合如何从设计中提取和映射有限状态机,具体在第24篇介绍。

keep_equivalent_registers:阻止合并有相同输入逻辑的寄存器。

resource_sharing:设置不同信号间共享算数操作符,选择为auto时设计会根据设计时序判断是否进行资源共享。

no_lc:选中会关闭LUT组合。

no_srlextract:选中该选项时,移位寄存器会用普通的寄存器实现,而不用FPGA内部专用的SRL资源。

max_bram:设置设计中运行使用的最大块RAM数量。通常当设计中有黑盒子或第三方网表时,使用该选项来节省空间。默认值为-1,表示允许使用该FPGA中所有的块RAM。

max_uram:设置设计中运行使用的最大UltraRAM数量(对于UltraScale架构FPGA而言)。-1,表示允许使用该FPGA中所有的UltraRAM。

max_dsp:设置设计中运行使用的最大DSP块数量。通常当设计中有黑盒子或第三方网表时,使用该选项来节省空间。默认值为-1,表示允许使用该FPGA中所有的DSP资源。

max_bram_cascade_height:设置可以将BRAM级联在一起的最大数量。

max_uram_cascade_height:设置可以将URAM级联在一起的最大数量。

cascade_dsp:设置在求DSP块输出总数时使用多少个加法器,默认计算时会使用块内部的加法器链。设置为tree会强制将该计算在fabric结构中实现。

no_timing_driven:禁用默认的时序驱动综合算法,这样可以减少综合运行时间,但会忽略综合中时序的影响。

sfcu:在单文件编译单元模式下运行综合。

assert:将VHDL中的assert状态纳入评估。失败或错误级别会停止综合进程并产生一个错误信息;警报级别会产生一个警告信息。

tcl.pre/tcl.post:选择tcl文件,在综合前和综合后会自动运行其中的命令。这两个文件应该放在相应的运行目录下,如project/project.runs/run_name。

创建综合策略

除了Vivado提供的配置好的综合策略外,还可以自行配置。在Settings中根据需要修改了设置选项后,点击右侧的Save strategy as按钮(如下图红框),会弹出窗口,填写策略名称和相关描述,即可保存为用户自定义的综合策略。综合策略列表的User defined strategies中即会出现自定义的综合策略。

在Settings->Tool Settings->Strategies中也可以设置综合策略,点击“+”即可新建策略。如果想在已有策略的基础上修改,则选中一个策略,点击上方的Copy Strategy按钮,User Defined Strategies中就会出现备份以供修改(Vivado提供的策略是不能修改的)。点击Apply应用配置后,综合策略列表中就会出现自定义的策略。

控制文件编译顺序

综合时必须选取合适的编译顺序,比如一个文件需要用到另一个文件中的相关申明。Vivado按照RTL文件的层次化结构编译文件,相关顺序显示在Sources窗口的Compile Order子窗口中(在底部选择切换)。

Vivado可以自动识别和设置最佳的顶层模块,同时自动管理编译顺序。顶层模块文件和该层次结构下所有的文件,都会以正确的顺序用于综合和仿真。Sources窗口的右键菜单->Hierarchy Update命令用于设置Vivado如何处理设计中文件的改动。

Automatic Update and Compile Order设定当源文件发生改动时,工具自动管理编译顺序,Compile Order窗口中将显示编译顺序,Hierarchy窗口中显示文件是否在层次结构中使用以及所处的位置。

Automatic Update, Manual Compile Order设定Vivado可以自动决定最佳顶层模块,但是允许人工设定编译顺序。在Compile Order窗口中拖动文件所处位置即可完成修改。

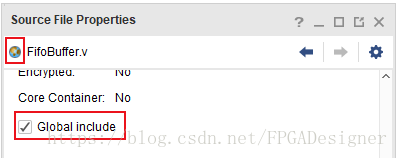

Vivado支持将Verilog(.v)或Verilog Header(.vh)文件作为全局`include文件。Vivado会在其它源文件前优先处理此类文件。选中需要添加的文件,右键->Set Global Include即可,或者在属性窗口中选中相应复选框。

编辑:hfy

-

vhdl

+关注

关注

30文章

814浏览量

127666 -

RTL

+关注

关注

1文章

377浏览量

59042 -

Vivado

+关注

关注

18文章

787浏览量

65089

发布评论请先 登录

相关推荐

Vivado编译常见错误与关键警告梳理与解析

使用Vivado高层次综合(HLS)进行FPGA设计的简介

Vivado那些事儿:节省编译时间系列文章

vivado 2018.1 综合失败且不报错、不生成runme.log日志文件,求大神帮忙

Vivado使用指南

嵌入式HLS 案例开发步骤分享——基于Zynq-7010/20工业开发板(1)

Vivado综合阶段什么约束生效?

在Artix 7 FPGA上使用Vivado的组合逻辑与顺序逻辑

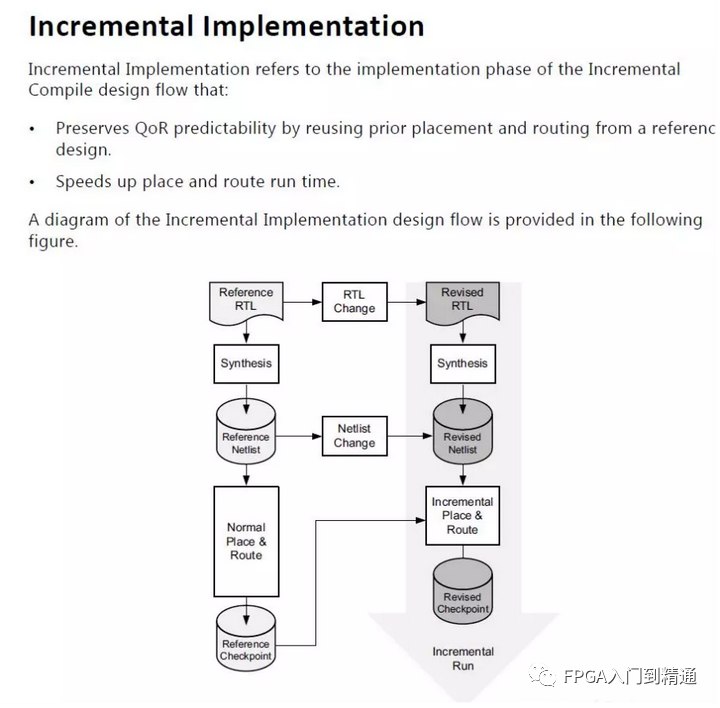

Vivado增量编译的基本概念、优点、使用方法以及注意事项

编译器的乱序策略

Vivado Design Suite 用户指南介绍

Vivado布线和生成bit参数设置

Vivado开发技巧:综合策略与合适的编译顺序

Vivado开发技巧:综合策略与合适的编译顺序

评论