描述

内核重置应该保持断言状态,直到相关时钟稳定为止。在从重置中取出以太网 IP 核之前,它必须具有稳定的频率而且没有故障。这适用于 SerDes 时钟和 IP 核时钟。 如果在一个时钟中检测到后续不稳定性,就必须重置 100G 以太网 IP 核。

这种不稳定性的一个实例是 CDR 锁丢失。

用户逻辑应该确定所有需要重置的外部条件(例如:时钟故障、CDR 锁丢失或电源故障)。

解决方案

QPLL 和 TX 数据通道QPLL 和 TX 数据通道需要在 GT 参考时钟输入之后重置,而且为 GT 初始化状态计时的 dclk/init_clk 会变得有效。

这可通过 Vivado 内核的 sys_reset 输入完成,也可通过异步下降的 GT 封装程序的 gtwiz_reset_all 输入完成。

如果 GT 参考时钟和 dclk/init_clk 在配置时有效,则内核中包含的 GT 初始化状态机将自动触发该重置。

TX 数据通道:

在串行数据生效后,GT 需要一个 GTRXRESET,以确保正确的 CDR 锁定数据。

电缆拔出并重新插入后或为链路合作伙伴上电或对其进行重置后,都需要该操作。

在内核层面上,为了避免在链路的 TX 端发生中断,可以使用 gtwiz_reset_rx_datapath 触发重置。

如果可行的话,光学设备的信号检测或信号损失反转可用来触发该重置。

如果信号检测或信号丢失不可用,可添加超时逻辑监控对齐/链路状态是否尚未完成,并发布 gtwiz_reset_rx_datapath 重置。

如果启用自动协商,则自动协商状态机提供一个内建的 500ms 超时来重新启动 AN 和重置状态机。

该轮询及复位程序将在标准上电时钟稳定重置序列后使用:

1) 等待 500ms

2) 轮询 stat_rx_aligned 状态

- 如果 stat_rx_aligned 无效,则断言 GT rx_datapathonly_reset,然后转到步骤 (1)

- 如果 stat_rx_aligned 有效,则断言 GT rx_datapathonly_reset,然后转到步骤 (3)

3) 等待 500ms

4) 轮询 stat_rx_aligned 状态

- 如果 stat_rx_aligned 无效,然后转到步骤 (2)

- 如果 stat_rx_aligned 有效,请在步骤 (4) 中等待

在某些拓扑上,如在 PAM4 PHY 或其它 PHY 情况下,可以看到 RX 串行数据需要很长时间才能完全稳定,而且可能会导致 GT RX 缓冲器错误。

如果 CDR 锁性能良好,完成对齐可能仍会出现 GT RX 缓冲器错误,因此可能需要对 GT RX 缓冲器状态进行更进一步的监控,才能触发重置。

-

以太网

+关注

关注

40文章

5069浏览量

166189 -

缓冲器

+关注

关注

6文章

1566浏览量

44866 -

cdr

+关注

关注

0文章

48浏览量

17986 -

UltraScale

+关注

关注

0文章

113浏览量

31326

发布评论请先 登录

相关推荐

赛灵思推出全球最大容量的FPGA – Virtex UltraScale+ VU19P

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器

Zynq UltraScale+ MPSoC的发售消息

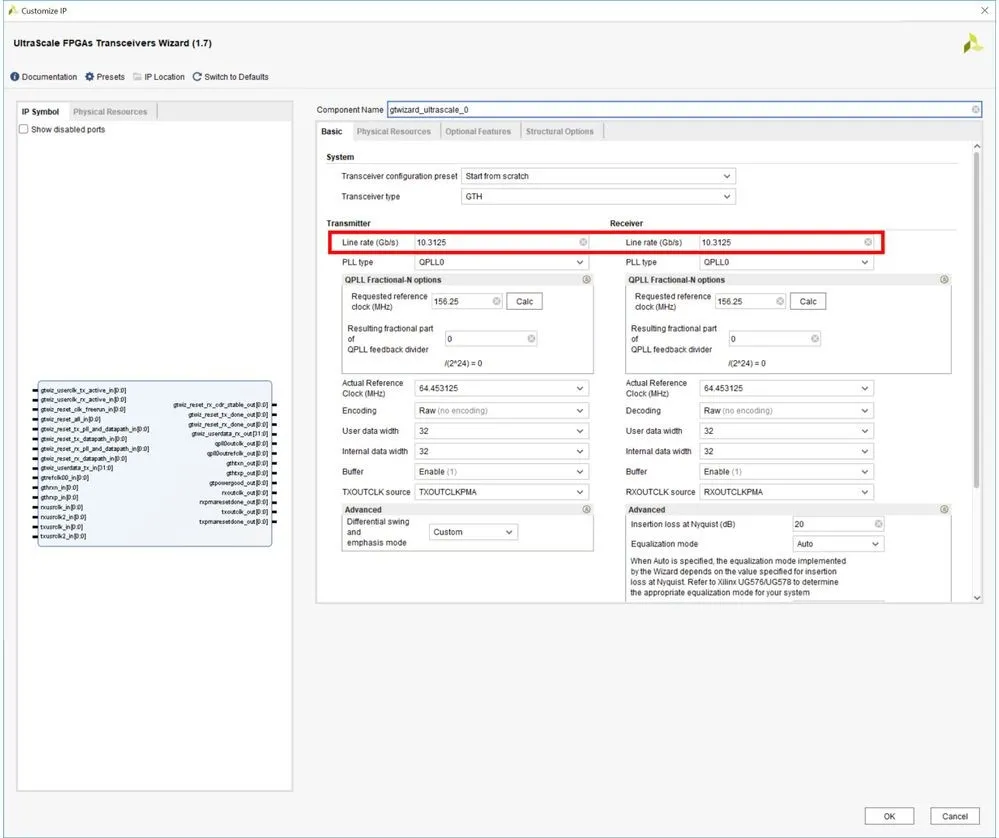

UltraScale/UltraScale+ GTH/GTY 收发器线速率设置的方法

UltraScale/UltraScale+的时钟资源

UltraScale和UltraScale+ FPGA封装和管脚用户指南

AMD推出全新Spartan UltraScale+ FPGA系列

UltraScale/UltraScale+内核重置

UltraScale/UltraScale+内核重置

评论