作者:易志强,韩 宾,江 虹,张秋云

0 引言

随着科学技术的快速发展,数据采集系统已广泛应用于航天、军事、工业、医疗等各个领域,尤其在高精度产品的检测和监控项目中发挥着至关重要的作用[1]。在实际工程应用中,要求采集系统具有高速率、高精度、实时处理、系统稳定性好和通道数量多等特点。但是,传统的数据采集方案多数以ARM处理器(Advanced RISC Machine,ARM)或数字信号处理器(Digital Signal Processing,DSP)作为控制核心,并不能有效解决高速数据采集处理中实时性和同步性的技术难题[2]。

与DSP和ARM相比,FPGA在数据采集领域有着极其重要的地位。FPGA具有时钟频率高、内部延时小、纯硬件并行控制、运算速度快、编程配置灵活、开发周期短、抗干扰能力强、内部资源丰富等优点,非常适用于实时高速数据采集[3-4]。

针对上述问题,本文设计了一种以FPGA作为主要处理器的16通道实时高速高精度的同步数据采集系统,本方案在实际监测工程中的采样频率为200 kHz,运用FPGA合理地控制和协调数据流在各个模块之间传输,进而实现系统所需求的实时、同步和高速采集等功能。

1 系统总体设计

1.1 系统总体设计结构

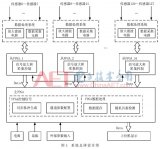

本系统的总体结构设计如图1所示,该系统由数据前采集前端处理、数据存储系统、选通开关控制系统和FPGA核心控制系统四部分构成。采集前端处理主要对输入测量系统的模拟信号进行滤波处理和幅值控制,以保证输入采集芯片的模拟信号更加稳定;FPGA核心控制系统通过使用FPGA作为核心控制器件,实现了数据同步处理、实时采集、数据缓存、时序约束、端口控制、数据判读数、据存储等功能;数据存储系统的功能是将判读后的数据实时存储到Flash中;选通开关控系统则是利用1选8多路复用开关ADG1408和固态继电器G3FD-X03SN实现被测设备的输入信号选通和电源通断控制,使被测设备能安全快速地进入到监测状态。本系统需要对8个被测设备进行同步实时循环测量与控制,并对测量数据进行记录判读、传输与存储。主要包括:供电管理与电源控制、直流电压电流实时监测、模拟信号通道切换、射频信号切换、数据存储等功能。

1.2 系统工作原理

系统上电后,等待FPGA初始化完成,进入等待连接状态。当外部输入相关命令参数后,由FPGA接收并解析命令。先控制系统内部选通开关工作,将被选中的设备信号接入采集系统中。然后向被测设备发出控制信息,同时采集系统实时监控被测设备的供电情况,随后,将采集的数据缓存到FPGA内部随机存取存储器(Random Access Memory,RAM)中等待处理。最后将采集到的数据通过FPGA片上先进先出队列(First Input First Output,FIFO)回传到外部监视器上进行实时显示,按照相应规则进行判决并存储,形成测试数据报表。

2 部分硬件电路设计

2.1 信号调理电路设计

由于输入系统的被测信号的电压幅值为27 V,无法直接对被测信号进行采集处理,因此本系统设计了信号调理电路对输入系统的模拟信号进行滤波处理和幅值控制。该电路通过采用可编程放大器AD8065设计了一个具有较平坦通带的二阶有源巴特沃斯低通滤波器,对前端输入模拟电压信号进行滤波处理。随后,利用芯片MAX4080将模拟电流信号转换成模拟电压信号。然后,使用高精度的电阻网络分压方式对被测模拟电压进行比例降压,再经过高性能运放AD8276进行模拟电压调理。最后,传送到模拟数字转换器(Analog-to-Digital Converter,ADC)进行采样。经过该硬件调理后,可以保障输入采集芯片的模拟电压信号具有平滑、稳定的特性。

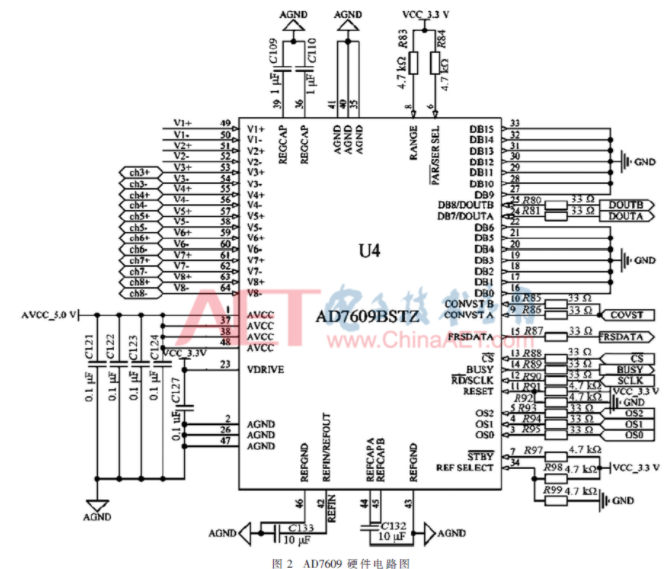

2.2 A/D转换电路设计

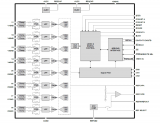

A/D模数转换器是数据采集的核心器件,影响着整个系统的采样精度、采样速率和数据吞吐量,所以芯片选型是采集系统设计中最关键的一步。本系统设计采用ADI公司的高精度、低功耗、电荷再次分配逐次逼近型模数转换器AD7609,该产品是一款8通道、18位、真差分、同步采样模数转换芯片。本系统采用两片AD7609芯片构成了16路通道的数据采集电路。AD7609硬件电路图如图2所示,将并行/串行接口选择输入端与3.3 V电平直接相连,再将芯片引脚CONVST A和CONVST B短接在一起,并施加同一个转换信号可以实现8个通道同时转换。

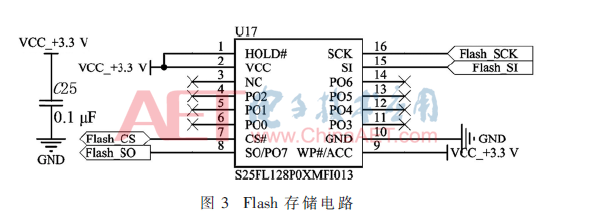

2.3 存储电路设计

数据采集完成后,将相应通道的采样数据发送到监视器进行实时显示和存储到Flash闪存中,等待外部控制器发送读取命令。本系统采用ST公司的S25FL128P Flash存储器进行实时存储。该芯片存储容量为128 Mbit,通过SPI接口与外部控制器建立通信,接口的时钟频率最大可达到104 MHz。该芯片具有设计简单、存储数据稳定和价格低廉等特点,具有广泛的实用性。Flash存储电路如图3所示。

3 系统软件设计

FPGA软件设计主要划分成系统同步时钟、数据采集、数据缓存、数据存储4个模块,下面依次介绍各个模块的设计。

3.1 系统同步时钟模块

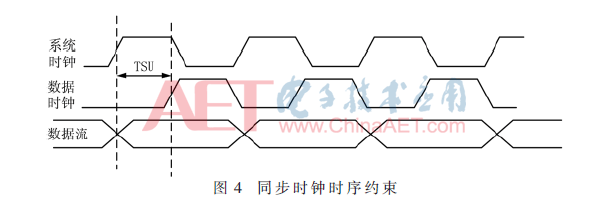

由于A/D采样和Flash数据存储时钟均为50 MHz,而数据处理和RAM缓存读写控制的时钟均为100 MHz。因此,为了保证系统各模块之间数据传输与处理的同步性,本系统采用FPGA内部的锁相环(Phase Locked Loop,PLL)IP核倍频或分频生成100 MHz和50 MHz的时钟。通过调用锁相环设计出一个具有低抖动、低延迟的系统时钟,保障了高速采集系统运行更加稳定[5-6]。与大多数时钟同步方案不同,该系统同步时钟模块除了使用PLL之外,还要通过时序约束的方式来减小数据与时钟之间偏斜,重新建立时钟偏斜的保持时间(Time Setup,TSU)如图4所示。通过时序约束不仅能实现系统时钟同步,还能避免出现数据传输错误。

3.2 数据采集模块

FPGA对AD7609的控制主要是通过对转换信号CONVST AB、片选信号CS、时钟信号SCLK进行控制,完成采样率调整和采样启停控制。如图5(a)所示,本模块通过控制AD7609在转换期间读取数据的方式进行采样。当检测到BUSY下降沿时,则完成所有通道的数据转换。从图5(b)的仿真图可以看出,通过使用系统同步时钟模块可以实现16路通道的同步采集功能。由于AD7609的输出编码方式为二进制补码,因此采集完成后可以通过ADC传递函数得到转换后数字信号代表的幅值,转换公式为:

式中,CODE为转换后的二进制码,V+和V-是电源供电电压,REF则为基准电压。

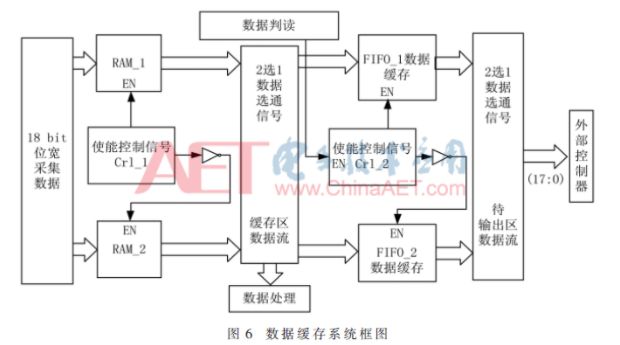

3.3 数据缓存模块

由于系统为16通道同步数据采集,因此每完成一次采集会产生大量待处理数据。并且由于FPGA与外部处理器通信之间存在硬件差异,会导致其与外部处理器之间存在传输处理速度不匹配的问题。因此,为了满足系统所需实时存储和传输要求,本系统采用了一种乒乓结构的传输方式[6]进行数据缓存。利用FPGA内置的知识产权核(Intellectual Property core,IP)资源,在ISE14.7软件操作平台上,构建系统所需18 bit位宽的块RAM和FIFO各两片进行轮流读写操作,实现数据实时缓存的功能。如图6所示,若使能信号Crl_1处于高电平,则控制RAM_1进行存储。当RAM_1存储满后,产生另一个使能控制信号Crl_2并将使能信号Crl_1电平翻转,由RAM_2继续行数据存储。当使能信号Crl_2到来时,等待系统判读生效后,则控制FIFO进行数据缓存。若该控制信号处于高电平则FIFO_1进行数据缓存。当FIFO_1缓存满后则将使能控制信号Crl_2的电平翻转,由FIFO_2继续缓存,并将FIFO_1中的数据通过某种协议传送到外部控制器进行处理。如此周而复始,在RAM和FIFO缓存器中进行乒乓操作,可以实现系统所需实时存储和传输功能。

如图7数据缓存仿真图所示,通过时序约束实现了两个不同缓存器之间的同步读写操作,很好地完成了乒乓式的数据缓存功能。

3.4 数据存储模块

利用外部处理器设定一个阈值,将缓存进RAM中的数据与阈值比对。若大于阈值电压,则判读无效将被测设备电源和信号选通开关断开;反之,数据判读有效,需要将采集时间、外部命令输入以及采集数据组帧后,实时存储到Flash中。本模块利用FPGA通过SPI总线与M25P128芯片建立主从关系,实现了Sector擦除、Page编程、地址管理、数据读取等功能,从而快速、准确地在Flash芯片中实现数据读写功能。该模块采用了摩尔状态机实现状态跳转,既消除了状态跳转时造成的毛刺,又很好地完成了存储与读取功能。数据存储与读取状态图如图8所示。图中地址管理除了实现页面读写地址转换外,还要将第一个页面用于存储下最后一次存储的地址,在断电重启后,能紧接着掉电前的数据继续进行数据存储。

Flash数据存储仿真图如图9所示,数据存储功能是将8 bit的并行数据通过Flash_SI引脚串行输入到Flash芯片中实现数据存储功能。数据读取功能则需要创建一个8位的移位寄存器将Flash_SO引脚的串行数据转为并行数据,传输到外部处理器进行处理。

4 结论

针对传统数据采集处理系统不能有效地实现数据在传输和存储过程中的同步性、实时性问题,本文设计了一种基于FPGA的16通道高精度同步实时高速采集系统。该系统采用FPGA控制AD7609在转换期间读取数据的传输方式,使系统能够达到200 kHz采样率。通过合理利用FPGA内部资源,实现数据缓存的乒乓传输方式,从而完成了数据的实时传输和Flash的实时存储功能,增强了数据传输和存储的可靠性、有效性和稳定性,极大地发挥出了FPGA的高速数据并行处理能力和时序约束能力。本系统已成功应用于某实际工程监测项目中,具有一定的应用价值。

参考文献

[1] 黄鸿靖.面向信号模拟的实时数据采集与块数据传输技术研究[D].杭州:浙江大学,2018.

[2] 赵树磊,刘敬猛,张慧,等.基于FPGA临空数据采集系统的设计[J].电子技术应用,2018,44(12):123-126.

[3] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2005.

[4] 王建中,杨璐.高速实时系统数据采集与传输[J].计算机科学,2016,43(S2):604-606.

[5] 皮代军,张海勇,叶显阳,等.基于FPGA的高速实时数据采集系统设计[J].现代电子技术,2009,32(6):12-14.

[6] 张素萍,李朝强,张建芬.一种高速实时数据采集处理系统设计[J].火力与指挥控制,2016,41(7):125-129.

作者信息:

易志强,韩 宾,江 虹,张秋云

(西南科技大学 信息工程学院,四川 绵阳621010)

编辑:hfy

-

FPGA

+关注

关注

1600文章

21281浏览量

592866 -

数据采集

+关注

关注

38文章

4477浏览量

112299 -

射频信号

+关注

关注

6文章

190浏览量

20444 -

数字信号处理器

+关注

关注

5文章

309浏览量

27195

发布评论请先 登录

相关推荐

高速数据采集卡在宽带实时频谱分析中应用

如何实现更高精度的同步测量?如何做好同步数据采集的时间校准?

AD7175-2适合做高精度数据采集吗?

AD4858:缓冲的8个同步同步同步取样 20比1 MSPS数据采集系统初步数据表 ADI

基于FPGA的高速数据采集系统该怎么设计?

基于FPGA的16通道实时高速高精度的同步数据采集系统

基于FPGA的16通道实时高速高精度的同步数据采集系统

评论